MIMO verlangt nach FinFET

Sieben Punkte, die Analog-Entwickler beachten müssen

Fortsetzung des Artikels von Teil 7

7. Simulationen strukturieren und aufteilen

FinFET-Modelle sind komplex, was zu langsamen Simulationen führt. Da der parasitäre Widerstand nicht ignoriert werden kann, werden die meisten Simulationen mit einer extrahierten Netzliste durchgeführt, die Tausende von Komponenten enthält.

Für eine gründliche Verifizierung des IC-Entwurfs ist daher ein Brute-Force-Ansatz erforderlich, der sich auf große Server und Multicore-Simulatoren stützt. Es ist zu empfehlen, die Simulationsstrategie an diese Herausforderung anzupassen und die Hierarchie-Ebenen im Entwurf zu erhöhen.

Jobangebote+ passend zum Thema

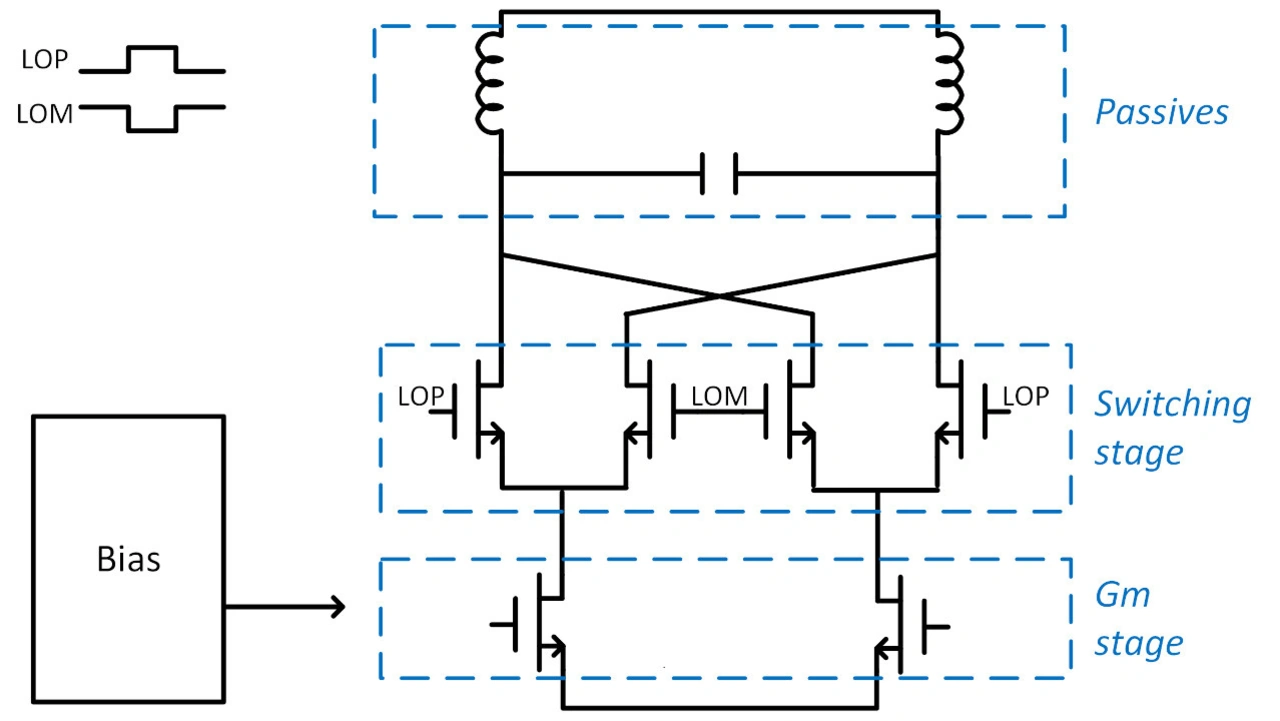

Bild 4 schlägt eine besser strukturierte Hierarchie für einen Mischer mit einer Gilbert-Zelle vor. Aufgrund der begrenzten Zahl von Bauteilen könnte die gesamte Schaltung mit einem flachen Schaltkreis-Layout versehen werden. Nach der Extraktion führt diese Wahl jedoch zu einer großen flachen Netzliste mit eingeschränkten Simulations- und Debugging-Optionen.

Andererseits trennt eine detailliertere Hierarchie, wie in Bild 4 vorgeschlagen, die verschiedenen Abschnitte des Entwurfs anhand ihrer Funktion. Abhängig von der Simulation gibt dies dem Entwickler die Flexibilität, genaue – also vollständig extrahierte – Ansichten für kritische Teilblöcke zu verwenden, wogegen für die anderen Abschnitte gröbere Modelle verwendet werden.

Als Faustregel sollten Entwickler die meisten Simulationszeiten auf Blockebene unter einer Stunde halten und erst in der letzten Verifikationsphase auf Brute-Force-Tests zurückgreifen.

- Sieben Punkte, die Analog-Entwickler beachten müssen

- 1. Keine Bauelemente mit unterschiedlichen Abmessungen mischen

- 2. Wiederholbare Muster verwenden

- 3. Parasitärer Anteile auf den Verbindungen von Beginn an abschätzen

- 4. Analogfehler per digitaler Kalibrierung korrigieren

- 5. Die Stromdichte begrenzt die Ausgangsleistung des Senders

- 6. Hohe Funkelrausch-Grenzfrequenz

- 7. Simulationen strukturieren und aufteilen