Engpass Speicher

High Bandwidth Memory mit FPGAs optimal nutzen

Während einer FPGA-Entwicklung können Entscheidungen getroffen werden, die sich negativ auf die Leistungsfähigkeit der Speicherschnittstelle und deren Datenübertragungsrate auswirken. Dem Entwickler stehen mehrere Optionen zur Verfügung, um die Datenübertragung zum Speicher zu maximieren.

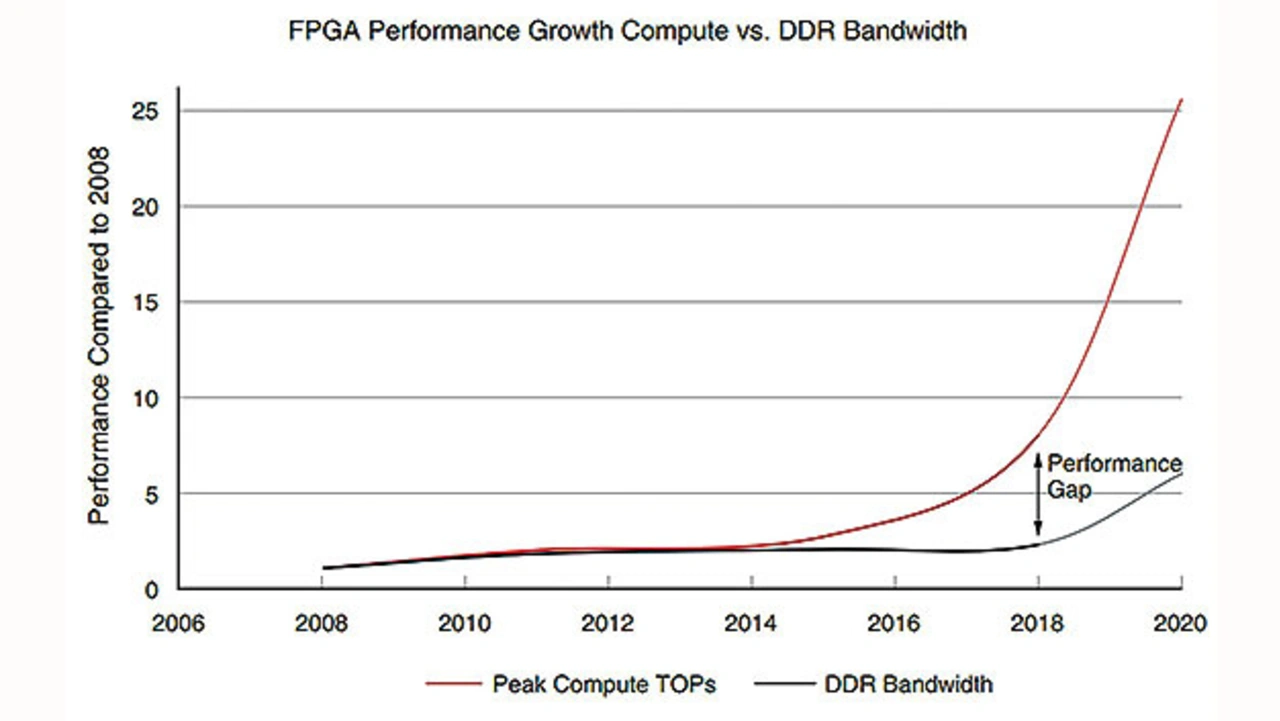

Viele aktuelle Applikationen wie künstliche Intelligenz (KI), Datenanalysen, das Transcodieren von Videosignalen und Genom-Analysen erfordern Speicher, die schnell große Datenmengen aufnehmen und ausgeben können. Traditionelle DDR-Speicher können mit diesen wachsenden Anforderungen nicht Schritt halten. Das sorgt für Datenengpässe. Bild 1 zeigt die wachsende Lücke zwischen Rechenleistung und der Datenübertragungsrate von DDR-Speichern.

Jobangebote+ passend zum Thema

Glücklicherweise können Speicher mit hoher Datenrate (HBM, High Bandwidth Memory) diese Engpässe verringern. Sie bieten mehr Speicherkapazität und größere Datenübertragungsraten, indem sie als SiP (System in Package) aufgebaut werden, mit vertikal gestapelten DRAM-Chips und einer breiten (1024 bit) Schnittstelle.

Was beeinflusst die Datenübertragung zum Speicher?

Jeder Entwickler, der sich mit externen DRAM-Schnittstellen befasst hat, weiß, dass deren theoretisch mögliche Datenübertragungsrate in der Praxis nicht erreichbar ist. Bedingt durch mehrere unterschiedliche Faktoren kann es sogar schwierig werden, auch nur in deren Nähe zu kommen.

Die Struktur der Datenströme ist oft der Grund für geringe Datenübertragungsraten. Das liegt daran, dass ein DRAM gewisse Opening- (ACT, activate) und Closing- (PRE, precharge) Zeilen innerhalb einer Speicherbank bedingt, und dass zufällige Zugriffe mehr Aufwand zu ihrer Unterstützung erfordern, was den Datentransfer in dieser Zeitspanne verhindert. Außerdem haben manche DRAMs, wie DDR4, HBM, einen »Overhead« wenn Daten mit aufeinander folgenden Adressen derselben Bank-Gruppe angefordert werden. Und Daten, die im Burst-Modus oder abwechselndem Read/Write-Status übertragen werden, bedeuten, dass die Datenleitungen (DQ-Bits) im schnellen Wechsel bi-direktional genutzt werden müssen. Dennoch muss eine gewisse Zeitspanne bei der Richtungsumkehr eingehalten werden, damit die Signale auf dem Bus den gewünschten Pegel erreichen können.

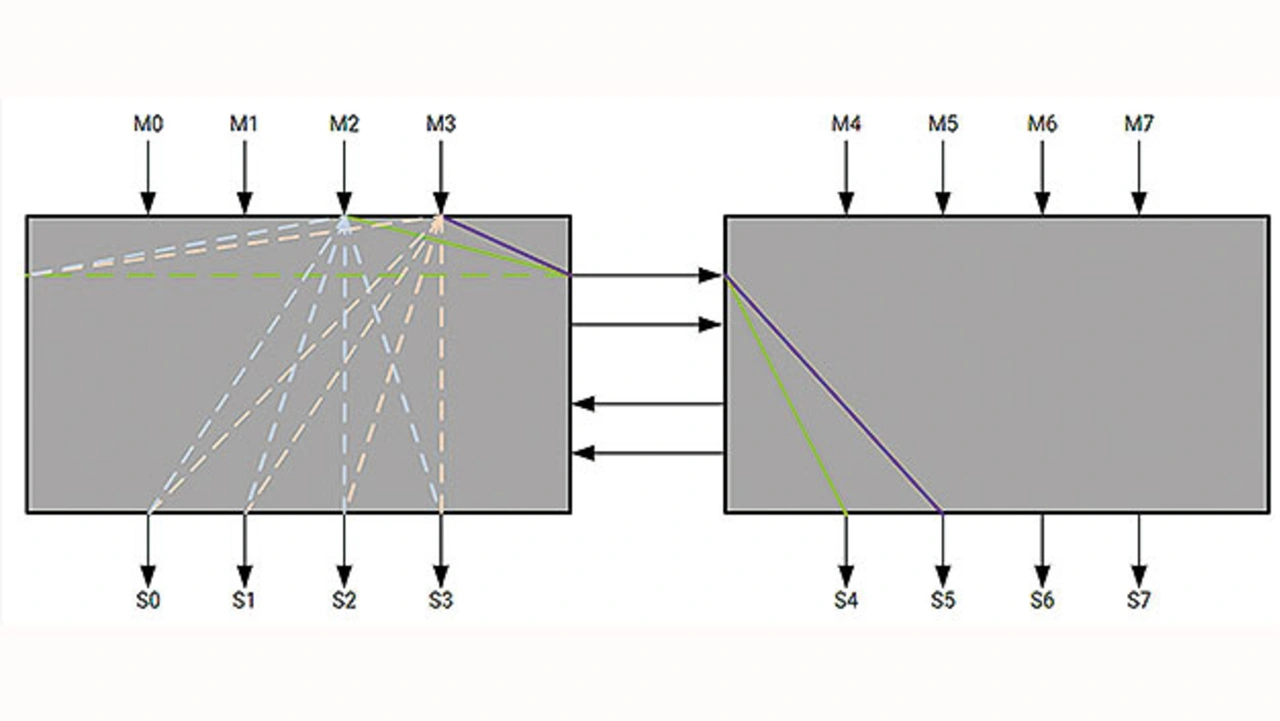

Im FPGA Virtex UltraScale+ (US+) von Xilinx mit HBM ist ein Hardware-Switch integriert, der den Zugriff von jedem der 32 AXI-Kanäle auf jeden der HBM-Pseudokanäle und den adressierbaren Speicher ermöglicht. Der fest im Silizium verdrahtete Switch reduziert die Komplexität bei der FPGA-Schaltungsentwicklung, verringert Routing-Probleme bei hohem Datenverkehr und erlaubt eine flexible Adressierung.

Für die flexible Adressierung über alle HBM-Stacks hinweg enthält der AXI-Switch Schaltelemente, die für jeweils vier Master und vier Slaves zuständig sind (Bild 2). Diese Schaltung erleichtert die flexible Adressierung. Doch es gibt einen Grenzwert, der die Datenübertragungsrate zum Speicher beeinflusst. Da nur vier horizontale Pfade verfügbar sind, kann der HBM-Stack die erzielbare Datenübertragungsrate durch Arbitrierung begrenzen.

Maximieren der Datenübertragungsrate zum Speicher

Wenn es um die Maximierung der Datenübertragungsrate für den Speicherzugriff geht, sollten Entwickler eine Änderung der Befehls- und Adressierungsmuster in Betracht ziehen. Da zufällige Speicherzugriffe und kurze Bursts von Read/Write-Transaktionen die schlechteste Datenübertragungsrate ergeben, sollten Entwickler überlegen, ob und wie sie diese abändern können. Damit lässt sich die größtmögliche Wirkung erzielen.

Wenn ein Entwickler den Datenabruf nicht ändern kann, bietet die HBM-Memory-Controller-IP mehrere Optionen, die hilfreich sein können:

- Custom Address Mapping: Wie bereits erwähnt, erfordern Zufallszugriffe höhere Raten von ACT- und PRE-Befehlen. Mit einer maßgeschneiderten Adressenbelegung lassen sich die AXI-Adressen auf HBM-Speicheradressen beziehen. Das kann die Zahl der Seitenaufrufe erhöhen und die Datenübertragungsrate vergrößern.

- Bank Group Interleave: Sie ermöglicht sequenzielle Adressen, um zwischen geraden und ungeraden Bank-Gruppen umzuschalten, und damit die Datenübertragungsrate zu maximieren.

- Enable Request Re-Ordering: Damit kann der Controller die Befehlsfolge anders anordnen, z.B. kann er Befehle verschmelzen, um die Reaktionszeiten des Bus (Turnaround Time) zu reduzieren.

- Enable Close Page Reorder: Aktiviert, kann der Controller eine Seite schließen, nachdem der Befehl abgeschlossen wurde. Falls ausgeschaltet, bleibt die Seite offen, bis eine Operation mit höherer Priorität für eine andere Seite derselben Bank angefordert wird. Das kann sich vorteilhaft auswirken, je nachdem, ob ein lineares, spezifisches oder zufälliges Adressiermuster benutzt wird.

- Enable Look Ahead Pre-Charge: Der Controller kann Befehle umordnen, um PRE-Befehle zu minimieren.

- Enable Look Ahead Activate: Der Controller kann Befehle umordnen, um ACT-Befehle zu minimieren.

- Enable Lookahead Single Bank Refresh: Damit wird dem Controller ermöglicht, Refresh-Zyklen einzufügen, je nach den anstehenden Operationen zur Maximierung der Effizienz.

- Single Bank Refresh: Der Controller aktualisiert eine Bank individuell, statt alle gleichzeitig.

- Enable Refresh Period Temperature Compensation: Diese Option erlaubt es dem Controller die Refresh-Rate dynamisch anzupassen, anhängig von der Temperatur der gestapelten Speicherchips.

- Hold Off Refresh for Read/Write: Sie erlaubt dem Controller einen Refresh zu verzögern, um zunächst die laufenden Operationen abzuschließen.

HBM-Monitor im Entwicklungswerkzeug

Seine Software Vivado zur Analyse und Snythese von HDL-Entwürfen hat Xilinx um einen HBM-Monitor ergänzt, der ähnlich wie SysMon die Die-Temperatur jedes HBM2-Die-Stapels einzeln anzeigen kann. Er kann außerdem die Datenübertragungsrate auf MC (Multi Channel)- oder PC (Pseudo Channel)-Basis anzeigen.

Damit Entwickler die HBM-Konfiguration angemessen umsetzen können, sollten sie mit den standardmäßigen HBM-Einstellungen beginnen und den Read/Write-Durchsatz als ihre Basisgröße ansetzen. Dann generieren sie neue .bit-Dateien mit Hilfe der weiter oben erwähnten HBM-Memory-Controller-Optionen, um zu bestimmen, welche Kombination von Optionen den größten Durchsatz erzielt. Zu beachten ist, dass die Art der Konfigurierung des AXI Switch auch die HBM-Datenübertragungsrate und den Durchsatz beeinflussen kann und ebenfalls in die Betrachtung einbezogen werden sollte.

Wenn Entwickler einen bereits vorhandenen Entwurf mit dem Vitis-Tool benutzen, müssen sie den Schaltungsentwurf unter Einsatz eines spezifischen DSA-Durchlaufs (Device Support Archive) modifizieren. Vitis ist ein von Xilinx entwickeltes Programm, das als Framework zur Entwicklung von FPGAs mit Standardprogrammiersprachen dient, die als Beschleuniger in Rechenzentren eingesetzt werden, und mit dem Software für eingebettete Prozessoren entwickelt werden kann.

Anforderungen an den Entwurf

Für unterschiedliche HBM-Konfigurationen brauchen Entwickler den Zugriff auf den Schaltungsentwurf, um den HBM-IP-Kern zu modifizieren und anschließend neue Bit-Ströme und neue .xsa/.dsa-Dateien zu generieren, die vom Vitis-Tool zur Softwareentwicklung verwendet werden.

Für bestehende Entwürfe finden Entwickler Informationen auf den Github-Webseiten, in den SDAccel-Beispielsammlungen, der Internetseite zur Beschleunigerkarte Alveo U280 oder auch der Internetseite zum FPGA VCU128 von Xilinx, die praktische Referenzdesigns (Targeted Reference Design, TRD) enthält.

Warum muss man eine individuelle Schaltung für Alveo U280 erstellen, wenn die DSAs bereits existieren? Angesichts der Weiterentwicklung der Algorithmen ermöglicht eine rekonfigurierbare Schaltung eine schnellere Adaption, als es die Produktzyklen von Beschleunigerkarten mit festverdrahteter Funktion ermöglichen.

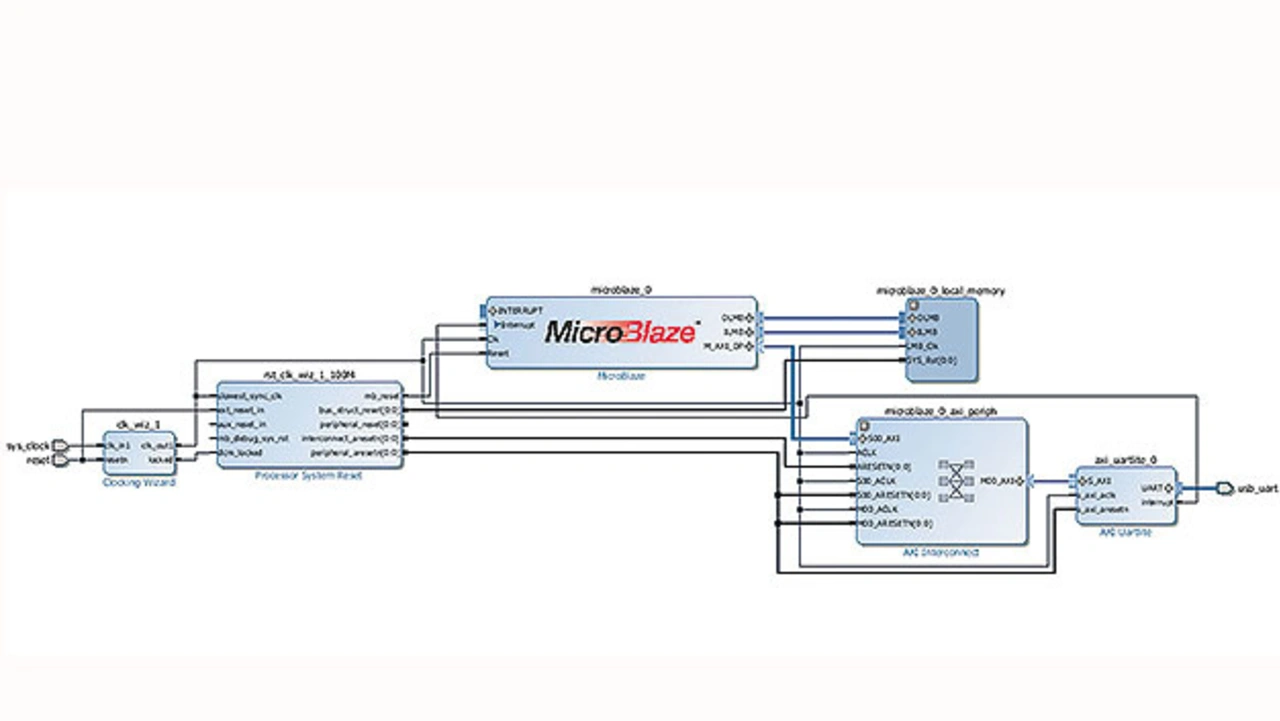

Es gibt mehrere Möglichkeiten eine individuelle Schaltung zu entwerfen. Die schnellste ist der Einsatz des Vivado IP Integrator (IPI). Das Beispiel in Bild 3 zeigt einen Weg mit Verwendung des FPGAs MicroBlaze, um den HBM-Datenverkehr per Software zu generieren. Dies könnte auch in HLS, SDAccel oder im Vitis-Tool mit Hardware-beschleunigtem Speicherdatenverkehr geschehen. Der Einsatz des MicroBlaze als Generator für den Datenverkehr macht es jedoch einfach, die Datenmuster einschließlich der Speicheradressen zu steuern. Außerdem können Entwickler so eine Standardvorlage für den Speichertest verwenden, um Schleifen und diverse Muster zu modifizieren und zu erstellen, um die optimale HBM-Datenübertragungsrate zu wählen.

Die Schritte zur Ausführung eines Entwurfs mit dem Vitis-Tool oder dem SDK (Software Development Kit) sind ähnlich. Sie umfassen Punkte wie die folgenden:

- Öffnen von Vivado

File=>Project=>New

Erstellen oder Öffnen eines existierenden Vivado-Entwurfs

Auswahl von U280, VCU128 oder des eingesetzten US+- HBM-Bausteins - Erstellen der Blockschaltung

Hinzufügen des HBM-IP-Kerns - Hinzufügen von MicroBlaze, UART und etwaigen benötigten Peripherie-IPs

- Validieren des Entwurfs und Generieren der Ausgangsprodukte

validate_bd_design

generate_target all [get_files <>.bd] - Erstellen des HDL Wrapper für .bd

make_wrapper -files [get_files <>.bd] -top - Ausführen der Synthese

- Ausführen der Implementierung

- Generieren des Bitstroms

- Exportieren der Schaltung

File=>Export Hardware

Wird das Vitis-Tool eingesetzt, müssen eventuell folgende Befehle ausgeführt werden:

(If using 2019.2) write_hw_platform -fixed <>/xsa

(If using 2019.1) write_dsa -fixed <>.dsa - Öffnen des Vitis-Tools

- Arbeitsbereich auswählen

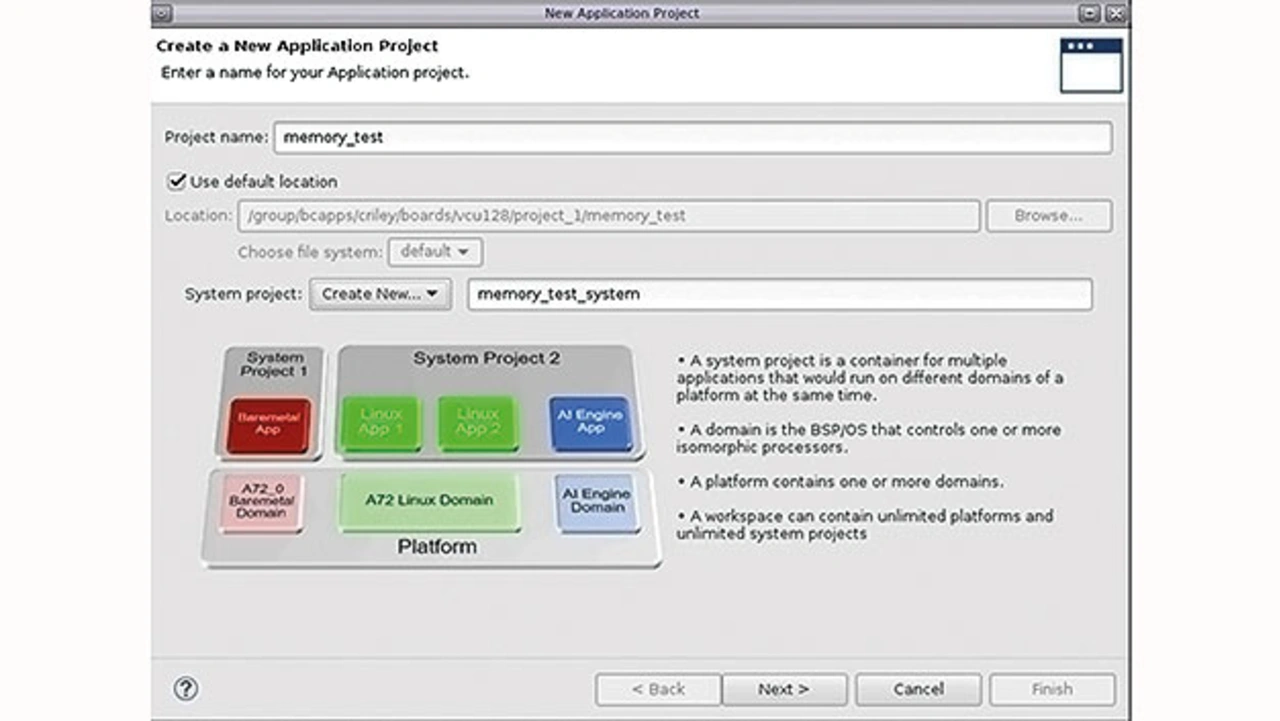

- Erstellen eines neuen Applikationsprojekts und eines neuen Board Support Package (Bild 4)

- Klicken auf »Next«, Auswahl von »Create from Hardware«, klicken auf »+« mit Auswahl der Dateiendung .xsa

- Klicken auf »Next«, Auswahl »CPU MicroBlaze«, »Language C«

- Klicken auf »Next«, Auswahl »Memory Tests« und klicken auf »Finish«

- Erstellen und Ausführen des Speichertests auf dem Zielbaustein

Anmerkung: Das Projekt muss eine IP-Integrator-Blockschaltung mit HBM und MicroBlaze enthalten. Auf diese Blockschaltung bezieht sich der Schaltungsentwurf, um nahezu die maximale theoretische Datenübertragungsrate von 460 GByte/s für beide HBM2-Stapel zu erreichen. Dafür ist ein kontinuierlicher Datenstrom auf alle 16 verfügbaren Speicher-Controller (MC) über die AXI-Kanäle zu leiten.

Der Einsatz von Vitis zur Erstellung und Beschleunigung des HBM-Datenverkehrs ist eine schnelle und einfache Methode zur Verifizierung der Anforderungen an die Datenübertragungsrate zum Speicher und zur Sicherstellung, dass diese erfüllt werden. Daneben ermöglicht es Vitis, auch HBM-Konfigurationen zu erstellen, um zu bestimmen, welche für ein System optimal ist.

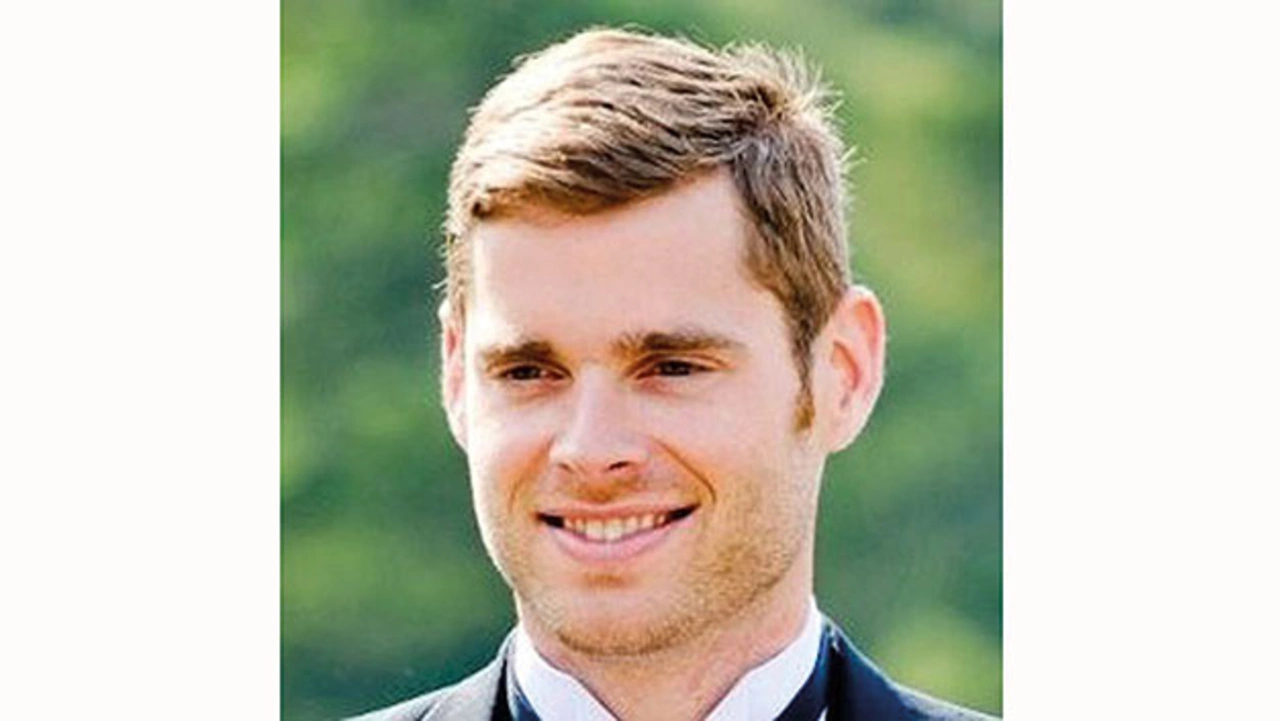

Der Autor

Chris Reley

ist Applikationsingenieur bei Xilinx, mit Sitz in Colorado und besonderer Experte in allen speicherbezogenen Dingen. Er hat seine gesamte Karriere bei Xilinx damit verbracht, technische Probleme für Kunden zu beheben und hat immer noch Spaß daran. Bevor er bei Xilinx zu arbeiten begann, studierte er an der Colorado State University Elektrotechnik und Mathematik.