Optimierung parasitärer Effekte

Evaluierungsboard reduziert Streuinduktivität mit SiC-MOSFETs

Parasitäre Elemente auf dem Strompfad sind zentrale Aspekte der elektronischen Entwicklung, da sie Effizienz, Leistung und Zuverlässigkeit maßgeblich beeinflussen.

Eine sorgfältige Auswahl der Bauteile sowie durchdachte Konstruktionsprinzipien sind entscheidend, um diese Aspekte zu kontrollieren und eine optimale Systemfunktionalität zu ermöglichen.

Auch wenn parasitäre Effekte nie vollständig eliminiert werden können, sind kontinuierliche Verbesserungen stets möglich – sei es durch die Verwendung hochwertiger Bauteile, optimiertes Design oder eine Kombination aus beidem.

Materialien mit großer Bandlücke (Wide Bandgap; WBG) wie Siliziumkarbid (SiC) können hierbei aufgrund ihrer spezifischen Eigenschaften einen wichtigen Beitrag leisten. Obwohl zahlreiche Ansätze existieren, konzentrieren sich die in diesem Artikel beschriebenen Methoden auf die Reduzierung der Leistungsschleifeninduktivität, um die Leiterplattenauslegung weiter zu optimieren. Die Optimierung für die Leistungsschleifeninduktivität wird sowohl durch Messungen als auch durch Simulationen bewertet – wobei die Differenz zwischen beiden weniger als 10 Prozent beträgt.

Infineon CoolSiC MOSFETs

Basierend auf umfangreichen Voruntersuchungen zu den Auswirkungen von Streuinduktivität von Leistungsschleifen hat Infineon ein Evaluierungsboard, das EVAL_QDPAK_FB_V2_1, entwickelt, das speziell auf die vielversprechende Lösung ausgerichtet ist, die oberflächenmontierte (SMT) Gehäuse mit Oberseitenkühlung (Top-Side-Cooled, TSC) bieten. Das Board verwendet vier AEC-Q101-zertifizierte SiC-Leistungs-MOSFETs (AIMDQ75R016M2H) mit einem Kanal-Widerstand von 16 mΩ und einer Nennspannung von 750 V. Das Bauteil der zweiten Generation mit marktführenden Figure-of-Merits (FoM) lässt sich bei 0 V sicher abschalten und bietet die meisten Vorteile bei Verwendung in Umgebungen mit geringen parasitären Einflüssen.

Trotz eines optimierten Bauteildesigns kann ein hoher dv/dt vom Drain-Source-Knoten über die Kopplungskapazitäten der Leiterplatte den Gate-Knoten modulieren und auf diese Weise parasitäre Effekte verursachen. Dadurch verursachte Ein- und Ausschaltvorgänge lassen sich durch die Analyse der Vds-Wellenformen identifizieren, da die Spannung am MOSFET in einem gut konzipierten Stromrichter einen monotonen Übergang aufweist.

Jobangebote+ passend zum Thema

Evaluierungsboard

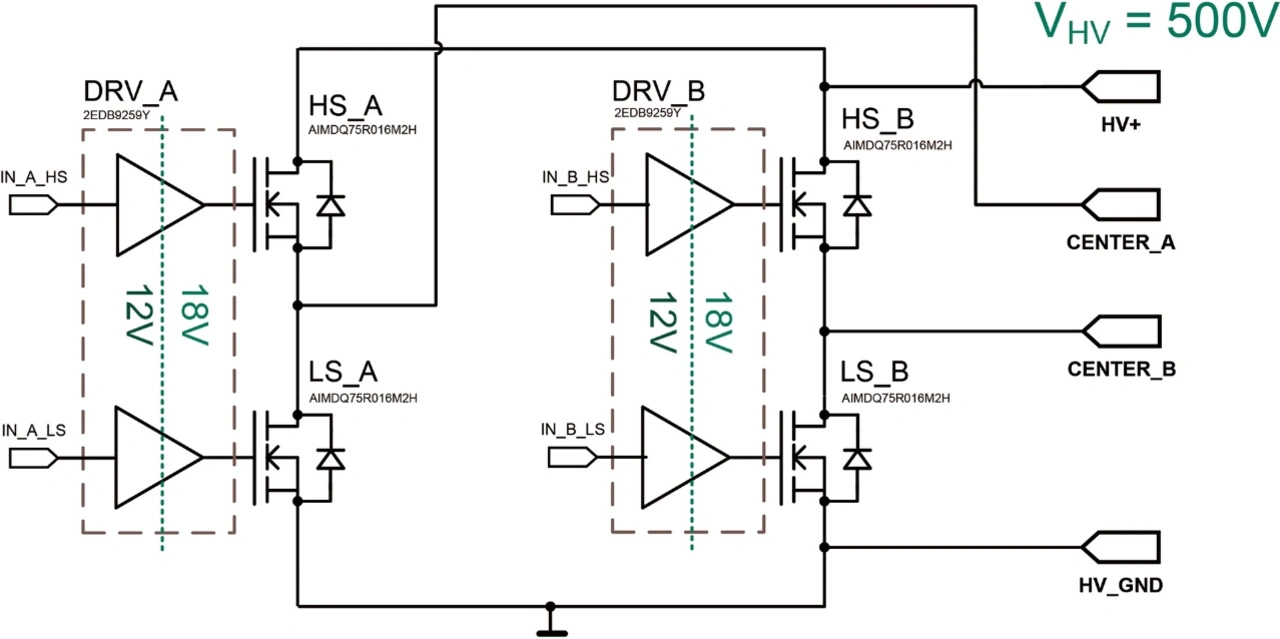

Das Evaluierungsboard umfasst eine Vollbrücke, wobei jede Halbbrücke über einen eigenen MOSFET-Treiber auf der Unterseite der Leiterplatte verfügt (Bild 2). Mit den ausgewählten MOSFETs ist eine Abschaltung bei 0 V möglich, sodass über den Zweikanal-Treiber 2EDB9259Y eine Gate-Ansteuerspannung von +18 V und 0 V verwendet wurde. Zudem bietet der Treiber eine Unterspannungsabschaltung (Undervoltage Lockout; UVLO) von 15 V, zwei vollständig isolierte Kanäle mit kurzen Ausbreitungsverzögerungen, einen Durchschlussschutz und ein hohes Gleichtaktunterdrückungsverhältnis (Common-mode Rejection Ratio; CMMR), was für die schnelle dv/dt dieser WBG-Bauteile von Vorteil ist.

Oberseitig gekühltes (TSC) Bauteil

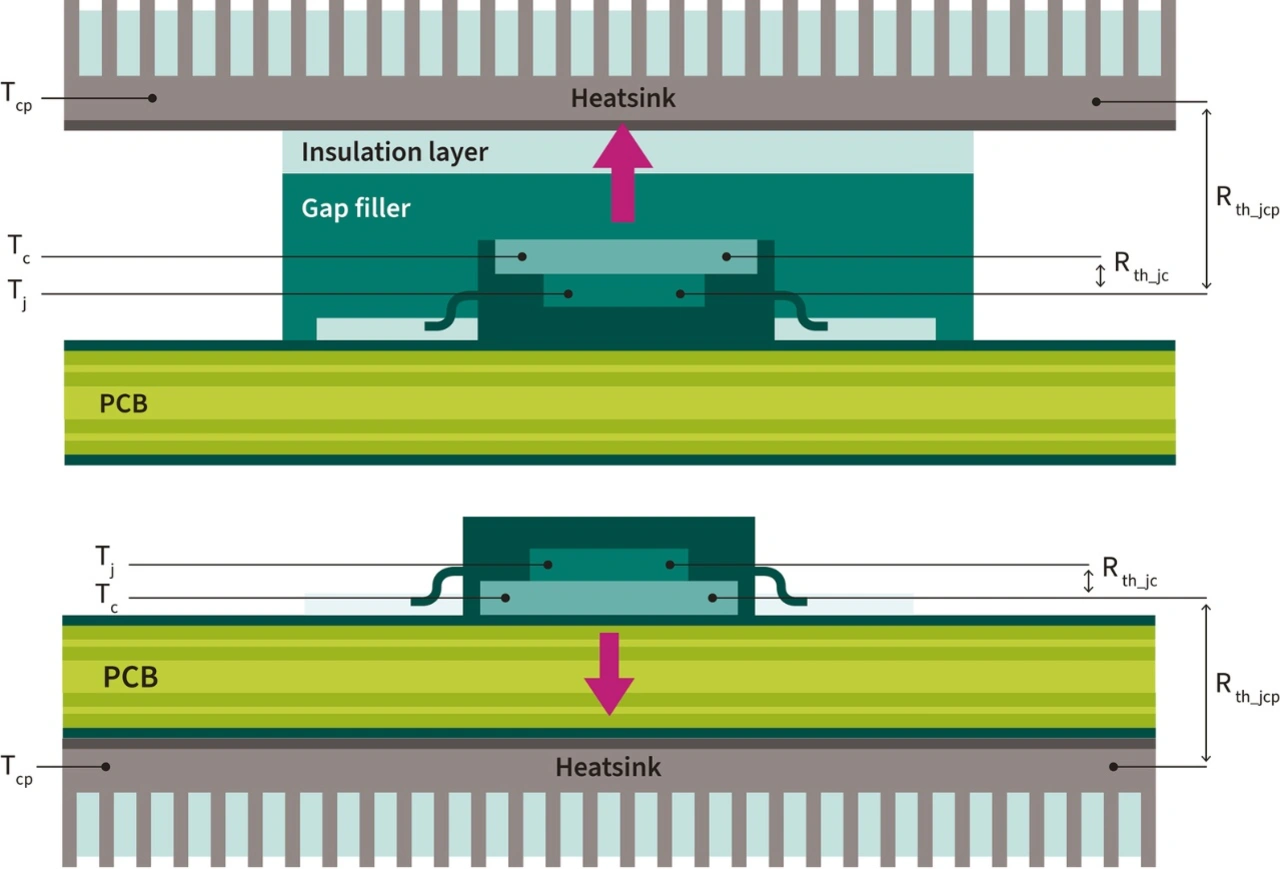

Das Evaluierungsboard verwendet ein oberseitig gekühltes SMT-Gehäuse (Q-DPAK) auf einer standardmäßigen vierlagigen Leiterplatte. Bei TSC-Gehäusen befindet sich das Kühlpad – im Gegensatz zu den branchenüblichen, unterseitig gekühlten (Bottom-Side-Cooled; BSC) Gehäusen – auf der Oberseite des Bauteils. TSC-Gehäuse bieten gegenüber BSC-Gehäusen mehrere Vorteile: Sie sind mit automatisierten Montagen kompatibel, wodurch manuelle Arbeitsschritte, die bei Durchsteckgehäusen erforderlich sind, entfallen. Zudem trennen TSC-Bauteile thermische und elektrische Pfade, was eine effiziente Wärmeableitung über die Oberseite ermöglicht, den Wärmewiderstand des Systems reduziert und das Risiko eines thermischen Durchgehens minimiert – und das ohne die elektrische Leistungsfähigkeit zu beeinträchtigen.

Überlegungen beim Einsatz von TSC-Gehäusen

Eine sorgfältige Konstruktion ist erforderlich, um eine angemessene Isolierung zwischen den Hochvoltbauteilen und den Kühlsystemen zu erreichen, ohne die thermische Leistung zu beeinträchtigen. Dazu müssen die Platzierung der Bauteile, das Leiterplattenlayout, das Design der Stromversorgungsebene, die Auswahl der thermischen Schnittstellenmaterialien (Thermal Interface Materials; TIM) und das Design des Kühlsystems sorgfältig geplant werden.

Für den Dauerbetrieb mit hoher Leistung ist ein Kühlkörper oder eine Kühlplatte erforderlich, wobei mechanische Einschränkungen berücksichtigt werden müssen. Um die mechanische Belastung auf die Leiterplatte zu minimieren, wurde eine quadratische Anordnung der Leistungsschalter innerhalb einer Kühlkörper-Halterungsstruktur gewählt. Diese Konstruktion erleichtert die Montage des Kühlkörpers und ermöglicht eine effiziente Kühlung der Leistungshalbleiter. Als thermische Schnittstelle zwischen den freiliegenden Metallpads des Q-DPAK und dem Kühlkörper kommt ein Spaltpad oder ein flüssiger Spaltfüller zum Einsatz.

Dabei muss bedacht werden, dass Spaltpads eine hohe Kompression erfordern, um eine optimale Wärmeleistung zu erzielen, wodurch erhebliche Kräfte in das System eingebracht werden. Die gleichmäßig verteilten Montagelöcher minimieren die mechanische Belastung der Leiterplatte und reduzieren die Verformung des Boards, insbesondere wenn keine zusätzlichen mechanischen Gegenstützen vorhanden sind.

Prinzip zur Minimierung der Streuinduktivität von Leistungsschleifen

Das Designziel für effiziente Stromrichter ist eine schnelle Kommutierung (hohe du/dt und di/dt) bei gleichzeitiger Minimierung von Ringing und Überspannungsbelastung der Leistungs-MOSFETs. Materialien mit großer Bandlücke weisen unter optimalen Umgebungsbedingungen eine hervorragende Leistung auf. Dabei ist die Reduzierung parasitärer Streuinduktivitäten in den Strompfaden, der Mittelpunktkapazität sowie der Koppelkapazitäten zwischen Spannungsbereichen von entscheidender Bedeutung.

Für eine optimale Leistung der Leistungsschleife sollten Entkopplungskondensatoren eine niedrige Impedanzverbindung zu Leistungs-MOSFETs aufrechterhalten. Idealerweise sollten sie in der Nähe der Halbbrückenschalter positioniert werden, um die Länge der Leistungsschleife zu verkürzen.

Die Leistungsschleife besteht aus SiC-MOSFETs und Keramikkondensatoren, die auf der Leiterplatte angeordnet sind. Durch die Magnetfeldkompensation wird die Gegeninduktion minimiert, da sich die durch Vorwärts- und Rückwärtsströme erzeugten Magnetfelder je nach Leitergeometrie gegenseitig aufheben können. Die effektive Streuinduktivität wird hauptsächlich durch die geometrische Anordnung beeinflusst.

Die Magnetfeldenergie steht auch in direktem Zusammenhang mit dem PCB-Design, wodurch eine enge Anordnung von Vorwärts- und Rückwärtsleitern erforderlich ist. Diese Studie konzentriert sich auf ein vertikales Leistungsschleifenkonzept, das die Platzausnutzung auf der Leiterplatte optimiert und eine flexible Höhe der Entkopplungskondensatoren ermöglicht.

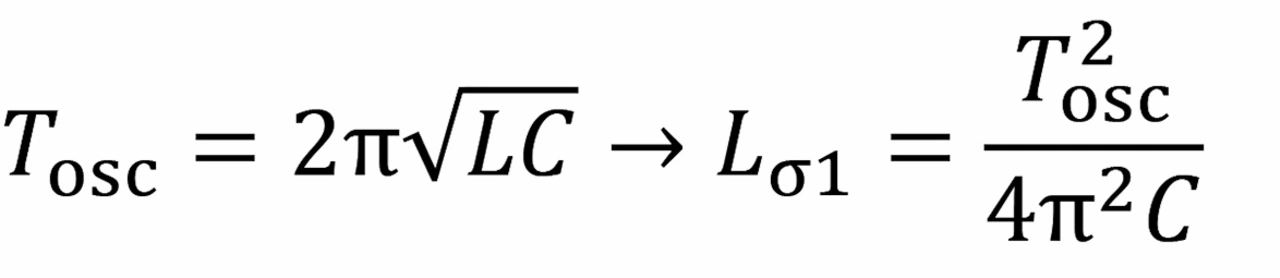

Experimentelle Messungen der Induktivität von Leistungsschleifen

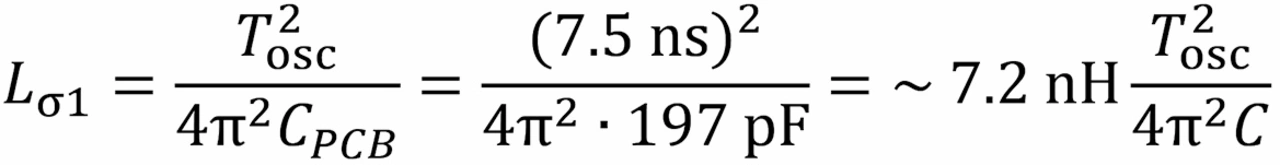

Nach dem Abschalten des MOSFET zeigen die Vds-Wellenformen gedämpfte Schwingungen aufgrund von Wechselwirkungen zwischen der parasitären Induktivität und Kapazität der Schalt. Die parasitären kapazitiven Schwingungen, gekoppelt mit der Streuinduktivität, werden durch Widerstandskomponenten in ihrer Stärke gedämpft. Ein solches Szenario kann als Serienresonanznetzwerk (R, Lσ und C) modelliert werden, wobei die Schwingungsdauer (Tosc) wie folgt ausgedrückt wird:

In den Experimenten wird die Schwingungsdauer mit 7,5 ns gemessen.

Das vollständige Doppelimpulsexperiment zeigt, dass der Strom durch einen Induktor nach 45 µs bei Verwendung einer 200-µH-Luftspulenlast etwa 100 A erreicht. Die Messung von Vds über dem Low-Side-MOSFET zeigt einen schnellen Spannungsanstieg in etwa 4,6 ns ohne parasitäres Wiedereinschalten. Die Schwingungsdauer hilft bei der Bewertung der Streuinduktivität der Leistungsschleife, wobei die Ausgangskapazität (Coss) bei 500 V etwa 195 pF beträgt. Die parasitäre PCB-Kapazität beträgt rund 2 pF, was zu folgender Berechnung der Streuinduktivität führt:

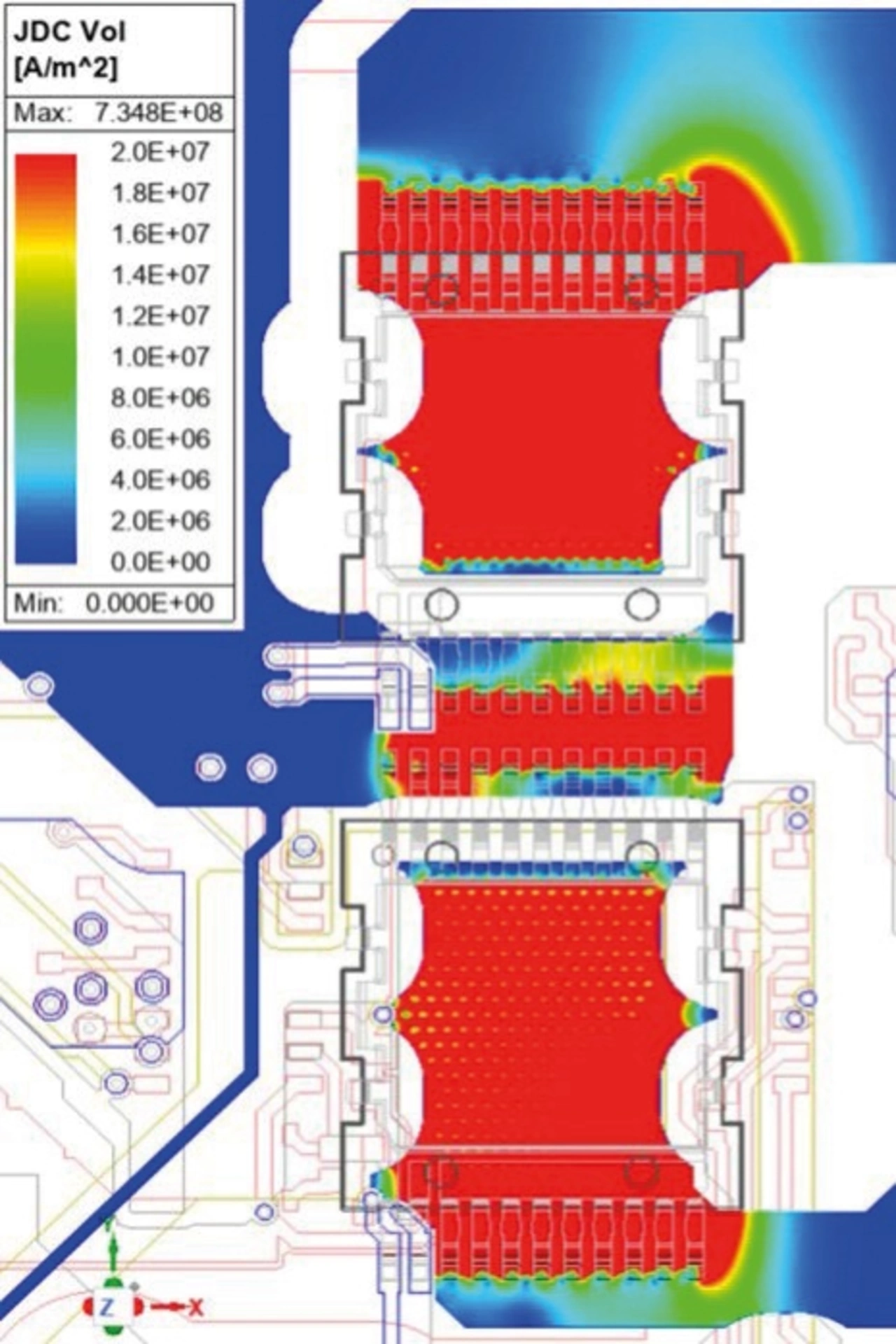

Abschätzung der Streuinduktivität mittels 3D-FEM-Simulation

Zusätzlich zu den experimentellen Ansätzen wurden die parasitären Induktivitäten der Leistungsschleife mithilfe eines Modells der Leiterplatte aus einem 3D-FEM-Multiphysik-Tool extrahiert. Das zugrunde liegende Modell geht davon aus, dass ein Kommutierungsstrom von den Anschlüssen der Entkopplungskondensatoren über die Kupferbahnen der Leiterplatte zu den Leistungs-MOSFETs und zurück zu den Entkopplungskondensatoren fließt, wobei die tatsächliche Schichtanordnung berücksichtigt wird. Auf diese Weise kann die konzentrierte Streuinduktivität der Leistungsschleifen extrahiert werden. Jede Halbbrücke wurde einzeln analysiert, um eine unbeabsichtigte Kreuzkopplung zwischen den verschiedenen Domänen zu vermeiden. Die extrahierten Ergebnisse sind in Tabelle 1 dargestellt.

| PCB-Bereich | Simulierte Streuinduktivität bei 100 MHz |

|---|---|

| Leistungsschleife der Halbbrücke A | 6.84 nH |

| Leistungsschleife der Halbbrücke B |

7.09 nH |

Tabelle 1: Simulationsergebnisse für die Streuinduktivität

Minimierung der parasitären Kapazität

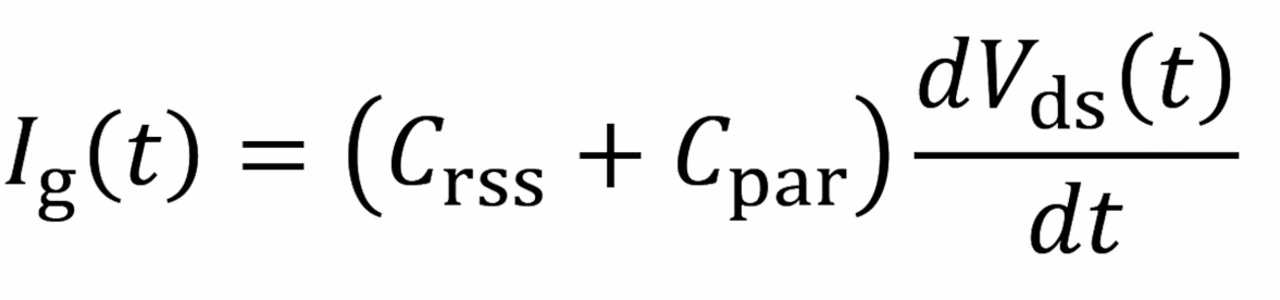

Große Kopplungskapazitäten zwischen schnell schaltenden Knoten (mit hohem du/dt und di/dt) und der Gate-Treiberschaltung führen zu erhöhten Verschiebungsströmen am Gate-Knoten. Dieser Effekt wird durch folgende Gleichung beschrieben:

Hierbei steht I_g (t) für den transienten Gate-Strom, C_rss für die Rückkopplungskapazität des Leistungs-MOSFETs und C_par für die gesamte parasitäre Kapazität. Dieses Problem lässt sich durch die Verwendung eines Gate-Treibers mindern, der über niederimpedante Pfade mit dem Gate des MOSFETs verbunden ist – beispielsweise durch niedrige externe Gate-Widerstände, optimierte Gate-Schleifen und eine möglichst nahe Platzierung des Treibers am MOSFET. Wenn eine niedrige parasitäre Kapazität nicht möglich ist, können unerwünschte parasitäre Einschaltvorgänge auftreten, da transiente Gate-Spannungen den Schwellwert des MOSFETs überschreiten können. Dadurch wird die Effizienz von Schaltwandlern reduziert, da zusätzliche Verluste durch gespeicherte Energie entstehen.

Um Abhilfe zu schaffen, sollte beim PCB-Design der Schwerpunkt auf die Reduzierung von Kopplungsflächen und die Maximierung der Abstände zwischen kritischen Knotenpunkten gelegt werden. High-Side- und Low-Side-MOSFETs sollten dicht beieinander platziert werden, und die Überkreuzungen kritischer Signale sollten minimiert werden. Durch die Verwendung dünner Leiterbahnen auf den äußeren Lagen oder rechtwinklig angeordneter SMT-Bauteile können überlappende Kupferbereiche reduziert werden.

Für die mechanische Integrität können Kühlkörperbefestigungen jedoch Kräfte verursachen, die zu einer Verformung der Leiterplatte führen können. Obwohl das Evaluierungsboard keinen Kühlkörper verwendet, ist es für die Montage eines solchen ausgelegt, wobei eine quadratische Anordnung für eine gleichmäßige Kraftverteilung sorgt, um Verformungen zu minimieren. Wenn eine Kompression der Spaltpads erforderlich ist, kann eine mechanische Halterung dazu beitragen, den durch Schrauben verursachten Kräften entgegenzuwirken. Alternativ kann ein flüssiger Spaltfüller die thermische Leistung verbessern und gleichzeitig die mechanischen Einschränkungen im Vergleich zu herkömmlichen Spaltpads verringern.