Energieeffizientes KI-System

AI goes Ultra-Low-Power – Teil 1

Fortsetzung des Artikels von Teil 1

Zweiteilung spart Energie

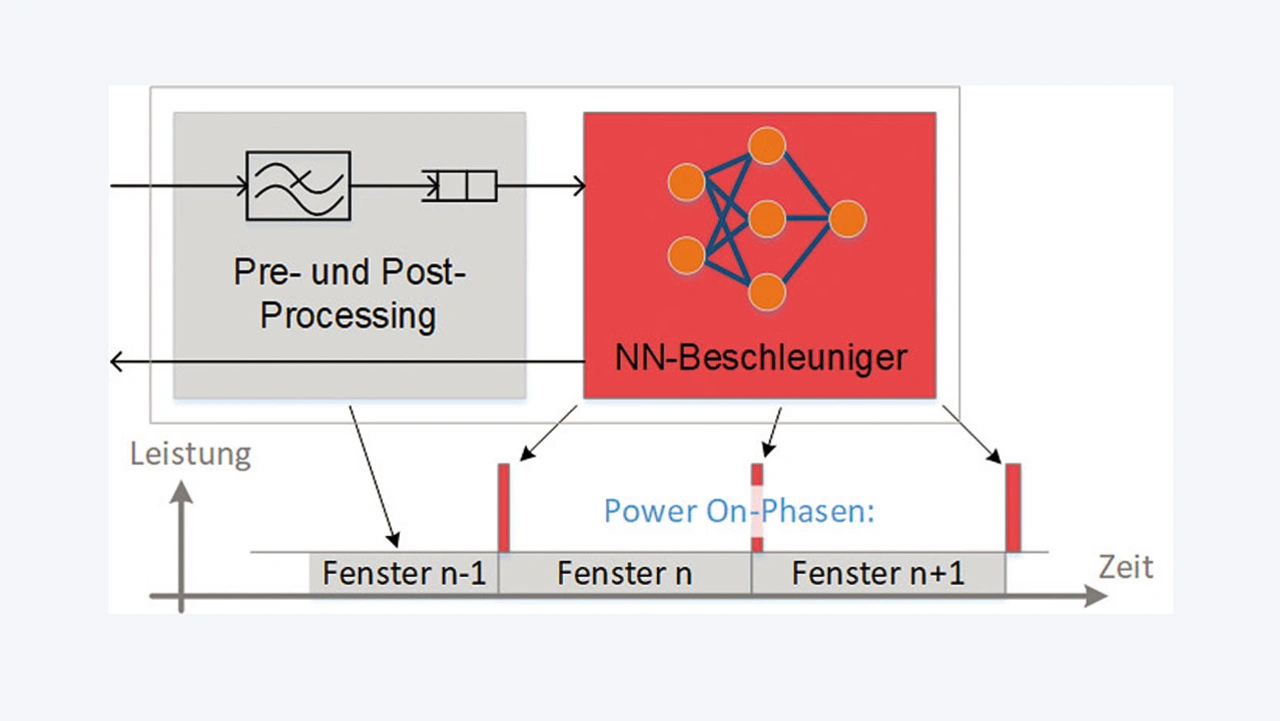

Wie Bild 2 zeigt, besteht das gesamte KI-System zur EKG-Analyse aus einer Hauptschaltung, die u.a. ein Preprocessing der Eingangsdaten enthält, und einem NN-Beschleuniger samt RRAM-Speicherblöcken, der dank einer eigenen Stromversorgung abgeschaltet werden kann. Preprocessing und Beschleuniger sind über einen doppelten Datenpuffer gekoppelt.

Jobangebote+ passend zum Thema

Zur Analyse von EKG-Daten ist die Betrachtung von Signalen ausreichender Länge erforderlich, weshalb jede zweiminütige EKG-Aufnahme in neun Fenster zu je 12,7 s unterteilt wird. Zunächst reduziert eine Bandpass-Filterung mit Down-Sampling die Datenrate im Preprocessing. Die neuronale Verarbeitung kann entsprechend dieser Datenratenreduktion deutlich langsamer erfolgen als die Eingabe. Dies wird zum Energiesparen genutzt, indem der NN-Beschleuniger zeitweise schlafengelegt wird.

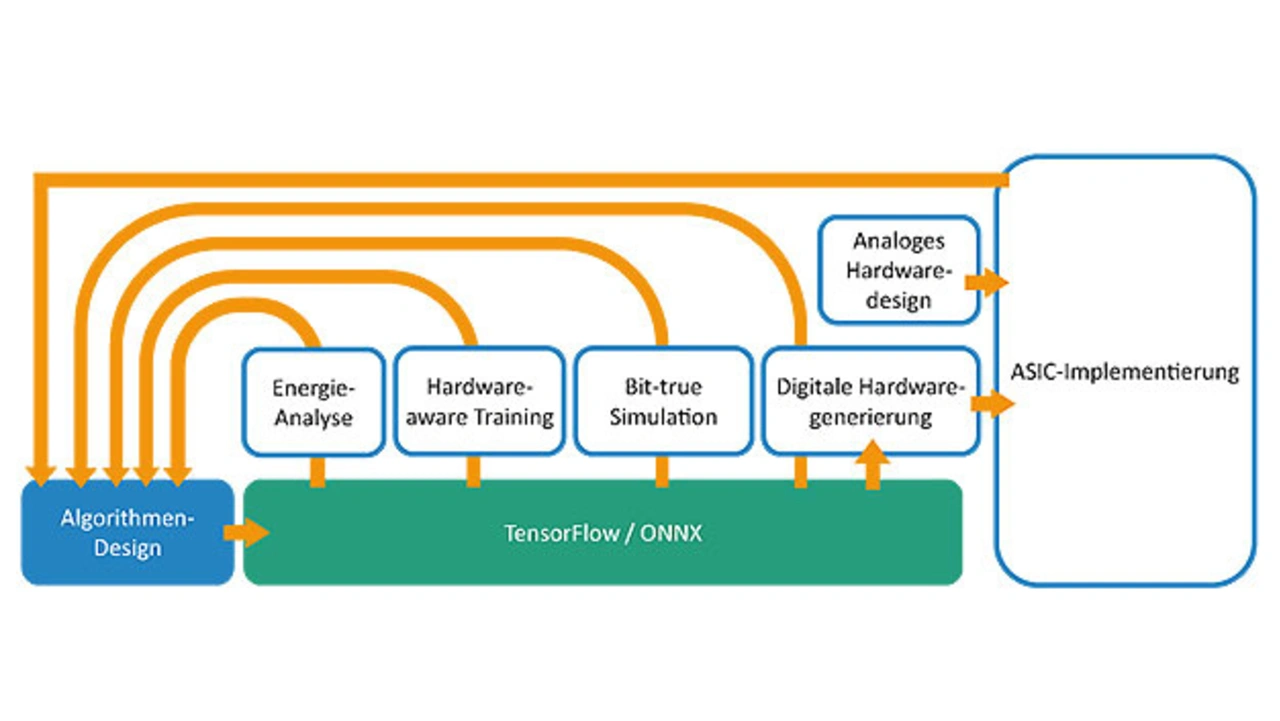

Entwurfsablauf Ein wichtiger Aspekt des Projekts war der in Bild 3 dargestellte, teilautomatisierte Entwurfsablauf. Dieser erlaubt eine frühzeitige Evaluierung des Energiebedarfs und die Berücksichtigung von HW-Eigenschaften wie z.B. der sehr kleinen Wortbreiten. Bereits bei der Spezifikation der NN-Hyperparameter – u. a. Schichttypen und -größen – wird ein grober Kompromiss der benötigten Energie anhand von simulierten Energiebedarfen für die benötigten Additions- und Multiplikationsoperationen für verschiedene Quantisierungsoptionen durchgeführt. Weiterhin wird die sehr starke Quantisierung von Gewichten (ternär) und Aktivierungen bereits im Trainingsalgorithmus berücksichtigt, wofür spezielle Bibliotheken zur Anbindung an TensorFlow geschaffen wurden.

Das gewählte und optimierte NN wird im ONNX-Format ausgegeben. Zum einen wird daraus automatisch – auf der Basis vorher entwickelter HW-Komponenten – die RTL-Schaltung in VHDL erstellt. Zum anderen wird die ONNX-Datei auch von einer Bit-True-Simulation in Python mit quantisierten Datentypen gelesen, die eine sehr schnelle und zu hundert Prozent genaue Simulation der Schaltung erlaubt, z.B. für automatisierte Rastersuchen (Grid Searches). Sämtliche Quantisierungseffekte können damit frühzeitig und vollständig erfasst werden und in die NN-Spezifikation zurückfließen. Zusätzlich dient die Bit-True-Simulation auch zur Verifikation der implementierten Schaltung.

Mit diesem Ansatz konnte sogar auf einem kostengünstigen 130-nm-Halbleiter-Prozess ein Beschleuniger mit 578 GOPS/W und 42 MOPS/mm2 realisiert werden.

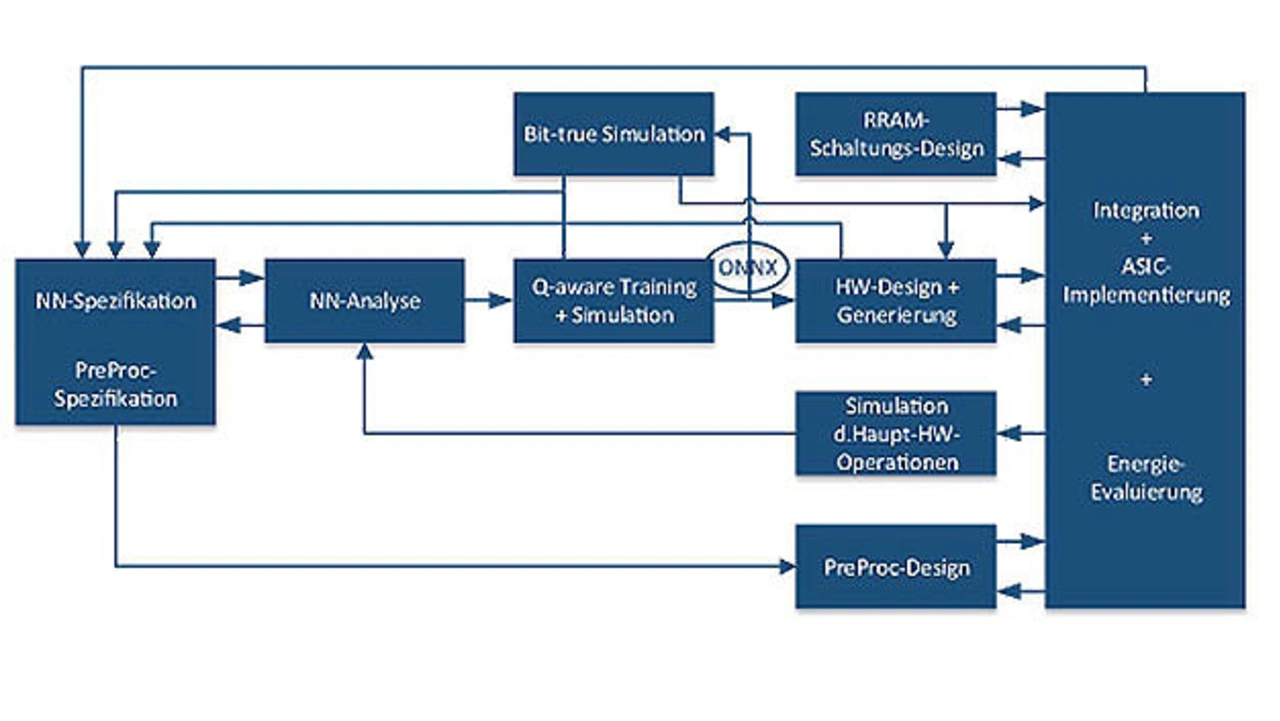

Wie die verschiedenen Aspekte, Entwurfsschritte und Aufgaben im Entwurfsablauf (siehe Bild 3) ineinandergreifen, ist in Bild 4 dargestellt. Genau deshalb wurde ein hochgradig iterativer Prozess gewählt. So wurden zur Vorbereitung des Entwicklungsprozesses erste NNs und ASICs als »Pipe-Cleaner« erstellt, diese genau auf ihre Schwachpunkte u.a. hinsichtlich ihrer Energieaufnahme untersucht und damit gezielt Verbesserungen eingebracht.

Einsatzmöglichkeiten für energieeffiziente KI-Chips

Der beschriebene KI-Beschleuniger wurde besonders für Zeitreihensignale und den Einsatz in batteriebetriebenen Geräten entwickelt. Ein Beispiel dafür sind Wearables zur Gesundheitsüberwachung wie das Fitness-Shirt [4]. Dabei erlaubt die Aufteilung des Beschleunigers auf zwei Blöcke neben dem gezielten Abschalten des NN-Beschleunigers auch eine getrennte Wahl und Optimierung der Taktfrequenzen von beiden Blöcken für maximale Energieeffizienz abhängig von der jeweiligen Eingangsabtastrate und der tolerierbaren Latenz der Anwendung. Auch bei einer Verarbeitung vieler Sensorsignale auf einem Server kann eine solche sensornahe NN-Berechnung als Vorverarbeitung genutzt werden, um die zum Server zu übertragende Datenmenge massiv zu senken.

Nachdem im 1. Teil die grundsätzlichen Überlegungen und Entscheidungen dargestellt wurden, geht es in einer folgenden Elektronik-Ausgabe im 2. Teil in die Details der Umsetzung.

Literatur

[1] Chen, Y.; Yang, T.; Emer J. und Sze, V.: Eyeriss v2: A Flexible Accelerator for Emerging Deep Neural Networks on Mobile Devices. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2019, Nr. 2, S. 292–308, DOI: 10.1109/JETCAS.2019.2910232.

[2] Su, F.; Ma, K.; Li, X.; Wu, T.; Liu, Y. und Narayanan, V.: Nonvolatile processors: Why is it trending? Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, S. 966–971, DOI: 10.23919/DATE.2017.7927131.

[3] Li, F.; Zhang, B. und Liu, B.: Ternary weight networks. arXiv, 1605.04711, 16. Mai 2016, https://arxiv.org/abs/1605.04711v1.

[4] CardioTEXTIL – Textiles Mehrkanal-EKG für den mobile Einsatz. Fraunhofer-Institut für Integrierte Schaltungen IIS, Website, www.iis.fraunhofer.de/de/ff/sse/health/medical-sensors-and-analytics/prod/cardiotextil.html.

Die Autoren

Dr. Marco Breiling

studierte Elektrotechnik in Karlsruhe, Trondheim, Paris und Southampton und promovierte in Erlangen. Er ist seit 2001 am Fraunhofer-Institut für Integrierte Schaltungen IIS in Erlangen tätig. Dort arbeitet er als Chief Scientist an den neuromorphen Hardwareentwicklungen.

marco.breiling@iis.fraunhofer.de

Dr. Peter Reichel

studierte in Dresden Informationssystemtechnik und promovierte in technischer Informatik. Er ist seit 2011 am Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS in Dresden, tätig und arbeitet als wissenschaftlicher Mitarbeiter im Bereich intelligenter Sensorik.

peter.reichel@eas.iis.fraunhofer.de

Dr. Marc Reichenbach

studierte Informatik in Jena und promovierte in Erlangen. Seit 2010 ist er an der Friedrich-Alexander-Universität (FAU) am Lehrstuhl Rechnerarchitektur tätig. Als Post-Doktorand forscht er dort an neuen energieeffizienten Rechnerarchitekturen u.a. für Anwendungen aus dem Bereich der künstlichen Intelligenz.

marc.reichenbach@fau.de

- AI goes Ultra-Low-Power – Teil 1

- Zweiteilung spart Energie