Imec

Das Wärmeproblem beim Interconnect verringern

Mit der fortschreitenden Skalierung wird die Erwärmung der Interconnects im Back-End-of-Line (BEOL) immer kritischer, da sie die Zuverlässigkeit des Chips gefährden kann. Abhilfe könnte ein Modell-Framework schaffen, das die Wärmeableitung genau vorhersagt.

Im Back-End-of-Line (BEOL) wird ein komplexes Verdrahtungsschema erstellt, mit dem Takt- und andere Signale verteilt, Strom und Masse bereitgestellt und elektrische Signale von einem Transistor zum anderen übertragen werden. Das Verdrahtungsschema basiert auf verschiedenen Metallisierungslagen, die lokale (Mx), mittlere (My) und (halb-)globale Verbindungsleitungen (Mz) enthalten. Mittlerweile werden bis zu 15 Lagen realisiert, wobei die typische Anzahl der Mx-Layer zwischen 3 und 6 liegt. Jede Lage enthält unidirektionale Metallleitungen, die in regelmäßigen Bahnen angeordnet und von intermetallischen Dielektrika umgeben sind. Sie sind vertikal über Via-Strukturen verbunden, die mit Metall gefüllt sind.

Mit der fortschreitenden Skalierung im Front-End-of-Line-Bereich (FEOL) werden auch die Abmessungen im BEOL reduziert, was zu immer kleineren Metall-Pitches und immer geringeren Querschnittsflächen der Leitungen führt. Routing-Staus und eine wachsende RC-Verzögerung (die Folge des steigenden Produkts aus Widerstand und Kapazität) sind zu wohlbekannten Engpässen bei der weiteren Skalierung von Interconnects geworden.

Seit einiger Zeit ist die Chipindustrie jedoch über ein anderes Phänomen besorgt: der Anstieg des thermischen Widerstands im BEOL und damit die Erwärmung der Metallleitungen. Dieser Temperaturanstieg kann sich dramatisch auf die Zuverlässigkeit der integrierten Schaltungen auswirken, da die Lebensdauer sowohl der BEOL- (in Verbindung mit Elektromigration und Stressmigration) als auch der FEOL-Strukturen ( z.B. im Zusammenhang mit einer negativen Bias-Temperaturinstabilität) bei hohen Temperaturen beschleunigt reduziert werden.

Die Hauptquellen für die Erwärmung sind die aktiven Teile im FEOL, sprich die Transistoren, die während ihres Betriebs Energie abgeben. Heutzutage haben Logikzellen eine Verlustleistung von etwa 10 W/mm², und ein Teil der erzeugten Wärme wird an die benachbarten BEOL-Strukturen abgeleitet. Darüber hinaus erwärmen die Ströme, die durch die Verbindungen fließen (um entweder Strom zu liefern oder Signale zu verteilen) ebenfalls die Leiter. Dieses Phänomen wird als Joule'sche Erwärmung bezeichnet und verschärft sich mit jedem neuen Technologieknoten, da der elektrische Widerstand der Metallleitungen und Vias mit der Skalierung zunimmt. Die Anforderungen an immer höhere Stromdichten und die schlechte Wärmeleitfähigkeit der Low-k-Dielektrika verschlimmern das Problem noch.

Genaue Prognosen sind gefragt

Üblicherweise wird die thermische Analyse von FEOL und BEOL getrennt mit simplifizierenden Modellen durchgeführt, wobei nur die Auswirkungen des Transistors auf den ersten Metall-Layer (M1) berücksichtigt werden. Aber dieser Ansatz greift zu kurz. Die Bedenken werden noch durch künftige Innovationen verstärkt, die der thermischen Optimierung entgegenwirken dürften. So ist beispielsweise die Verwendung von Air Gaps als alternatives Dielektrikum zur Verbesserung der RC-Verzögerung oder eine noch höhere Anzahl von BEOL-Layern denkbar. Außerdem könnte bei 3D-Technologien die BEOL der wichtigste Faktor für den Gesamtwärmewiderstand in modernen Packages werden. Die Verwendung von »Backside Power Delivery«-Schemata (Verlagerung des gesamten Stromversorgungsnetzes auf die Chiprückseite) und neuartige Transistorarchitekturen (wie z.B. »Gate-all-around«-Nanosheets) in der Logik-Roadmap können sich ebenfalls auf die Temperatur der Metallleitungen auswirken - positiv oder negativ.

Also ist ein umfangreicherer Modellierungsansatz erforderlich, um die Auswirkungen dieser Entwicklungen auf die Wärmeausbreitung zu erfassen und unser grundsätzliches Verständnis der Wärmeausbreitung in schmalen BEOL-Strukturen zu verbessern. Der Modellierungsansatz sollte es uns erlauben, zu erkennen, was am stärksten zur Erwärmung beiträgt, vorherzusagen, wie sich der Wärmewiderstand von BEOLs mit neueren Technologieknoten entwickelt, und Empfehlungen für ein wärmegerechtes Interconnect-Design zu geben.

Ein mehrstufiger Ansatz mit kalibrierten Modellen

Die Imec-Forscher verfolgen einen modularen Ansatz, um die thermischen Eigenschaften des BEOL zu bewerten. Sie haben verschiedene Arten von Modellen entwickelt, die die thermischen Eigenschaften der Materialien in verschiedenen Maßstäben und Detailstufen erfassen. Jedes Modell kann für sich allein verwendet werden, je nachdem, welcher Anwendungsfall von Interesse ist. Die Ergebnisse der einzelnen Modelle können auch als Input für das nächste Modell verwendet werden, so dass eine vollständige Analyse eines kompletten BEOL-Stacks möglich ist. Die Modellierungsarbeit wird mit experimentellen Daten kombiniert, die an Versuchsträgern mit industrierelevanten Materialien und Abmessungen gewonnen wurden. Die gemessenen Daten werden in die Modelle eingespeist und ermöglichen so eine genaue Kalibrierung und Vorhersage zukünftiger Szenarien.

Ein Überblick über die diversen (Unter-)Modelle

In einem ersten Schritt untersuchen die Forscher die Materialien auf atomarer Ebene mithilfe der Dichtefunktionaltheorie (DFT). Mit diesem Modell leiten sie die grundlegenden Eigenschaften von Elektronen und Phononen ab, d.h. den Wärmeträgern, die die Energie innerhalb des Materials bewegen.

Im nächsten Schritt wird die Wärmeleitung innerhalb der Materialien für unterschiedliche Materialdimensionen modelliert, von der µm- bis zur nm-Skala. Dazu wird ein intern entwickeltes Modellierungstool verwendet, das auf der Boltzmann-Transportgleichung (BTE) basiert. Das Modell erfasst zusätzlich die thermischen Effekte auf der Nanoskala. Die Materialeigenschaften von Metallen und Dielektrika, die an speziellen Teststrukturen charakterisiert wurden, dienen als Eingabe für das Modell. Für die Dielektrika wurde beispielsweise die so genannte 3Omega-Methode verwendet, um die Wärmeleitfähigkeit relevanter dielektrischer Materialien experimentell sehr genau zu extrahieren. Dabei ergab sich ein Wert von 1,15 W/mK für SiO2 und 0,3 W/mK für OSG3.0 (ein Organosilikat-Glas mit einer Dielektrizitätskonstante von 3,0).

Im dritten Schritt gehen die Forscher auf einen größeren Bereich des BEOL-Layouts über. Die thermischen Eigenschaften eines vollständigen BEOL-Stacks werden mithilfe eines 3D-FEM-Ansatzes (Finite-Elemente-Modellierung) modelliert und mit Selbsterhitzungsmessungen kalibriert. Dieser letzte Schritt liefert eine Wärmeleitfähigkeits-/Widerstandsabbildung des BEOL-Stapels und seiner einzelnen Schichten und ermöglicht eine schnelle Bewertung des Temperaturanstiegs in der Verbindungsstruktur.

Jobangebote+ passend zum Thema

Um vollständig abschätzen zu können, wie sich die Wärme in der BEOL ausbreitet, muss das Modell auch den Wärmeaustausch zwischen FEOL und BEOL genau berücksichtigen. Die Imec-Forscher haben eine Methode zur Schätzung dieses Wärmeaustauschs entwickelt. Diese thermische Kopplung wird als zusätzliche »Schicht« zum FEM-Modell hinzugefügt.

Anwendung der Modelle auf verschiedene Anwendungsfälle: Trends und nützliche Erkenntnisse

Die Wärmeleitfähigkeit elementarer Metalle sinkt bei Strukturbreiten von weniger als 10 nm

Ein typisches Ergebnis der BTE-Modellierung ist die Entwicklung der Wärmeleitfähigkeit der Materialien bei abnehmenden Strukturbreiten. Bei allen untersuchten elementaren Metallen nimmt die Wärmeleitfähigkeit deutlich ab, wenn die Leitungsbreiten in den 10-nm-Bereich reichen - was für die lokale Ebene von Verbindungen bei fortgeschrittenen Technologieknoten relevant ist. Dies wird in der Grafik in Abbildung 1 (Mitte) veranschaulicht.

Low-k-Dielektrika, Via-Layer und der My-Stack dominieren das thermische Verhalten eines 14-lagigen BEOL-Stacks

Der mehrstufige Modellierungsansatz wurde verwendet, um das thermische Verhalten eines kompletten, 14-lagigen BEOL-Stacks in einem modernen Technologieknoten zu bewerten. Die Arbeit ergab interessante Einblicke in die Art und Weise, wie sich die Design- und Technologieoptionen für den BEOL auf den Temperaturanstieg auswirken.

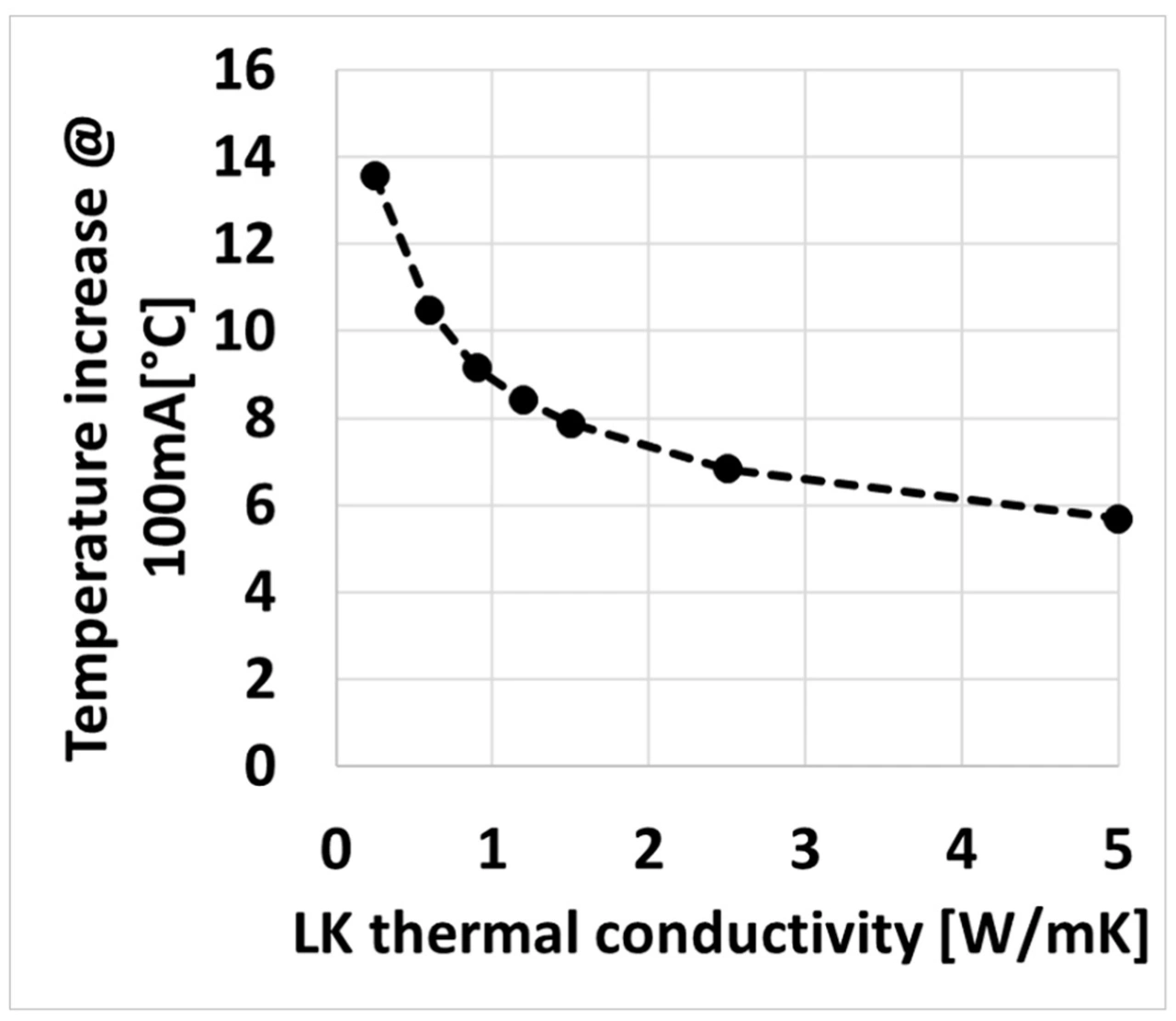

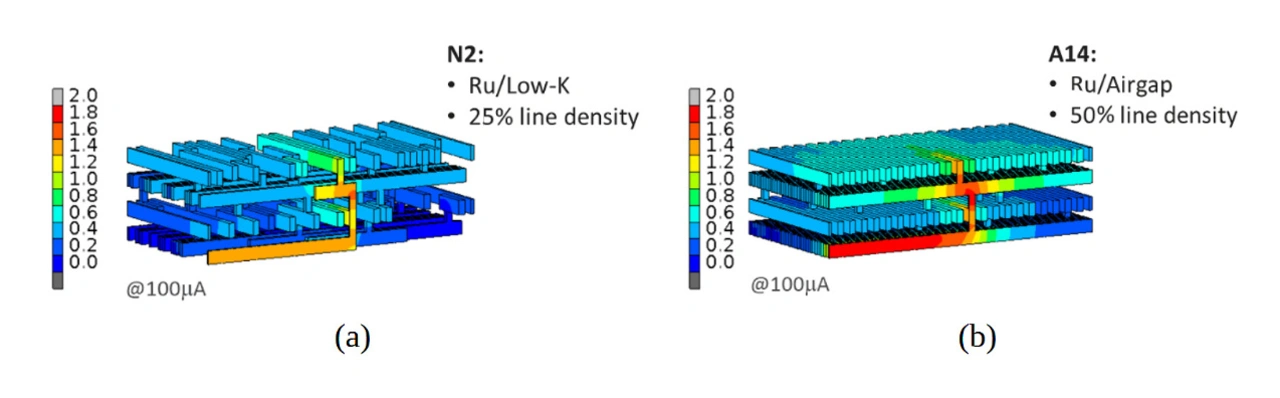

Der Beitrag des intermetallischen Dielektrikums ist signifikant. Ein schneller Temperaturanstieg im BEOL wird beobachtet, wenn die Wärmeleitfähigkeit des intermetallischen Dielektrikums unter 1 W/mK fällt. Dies entspricht dem Wärmeleitfähigkeitsbereich der meisten derzeit verwendeten dielektrischen Materialien wie OSG3.0. Die Auswirkungen verschärfen sich, wenn Air Gaps eingeführt werden (z.B. im Technologieknoten A14), da die Wärmeleitfähigkeit des Air Gaps sehr schlecht ist: Simulationen zeigen einen Anstieg der Selbsterhitzung der Metallleitung um 30 Prozent. Die Metallauswahl hingegen hat nur einen minimalen Einfluss auf die Wärmeabgabe.

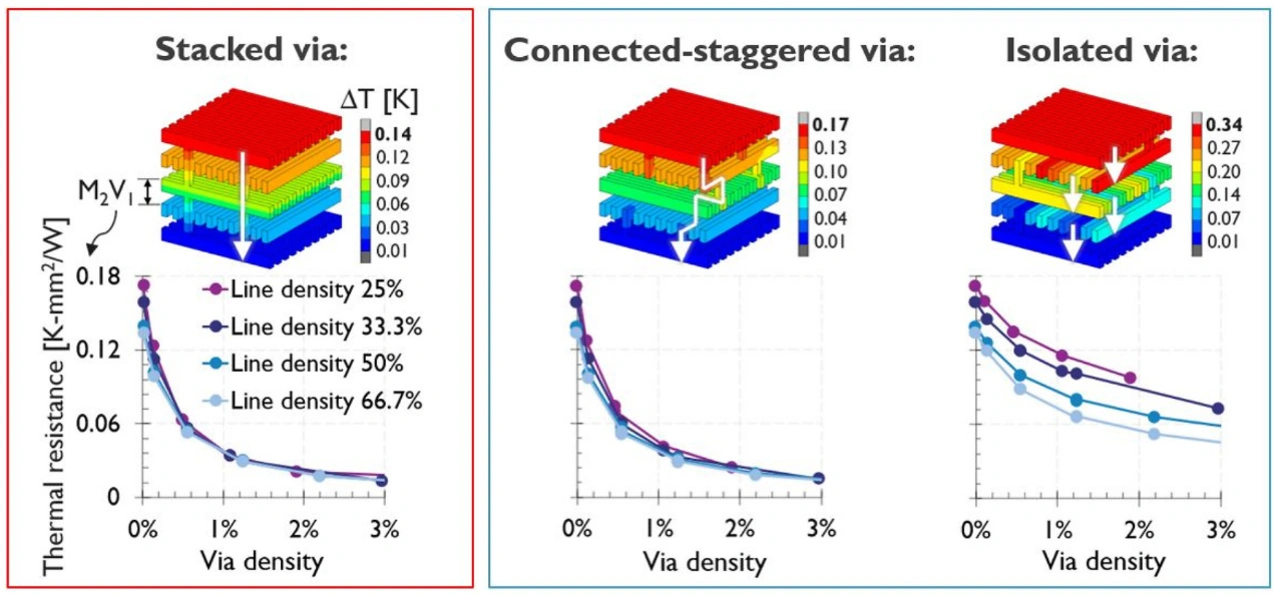

Der Einfluss der Via-Dichte und -Konfiguration wird deutlich spürbar. Eine höhere Via-Dichte begünstigt die Wärmeableitung zwischen den Verbindungslagen. Gleiches gilt für eine gestapelte Via-Konfiguration, bei der die Durchkontaktierungen zwischen den einzelnen Lagen gut aufeinander abgestimmt sind. Eine solche Konfiguration wird typischerweise in den globalen Verbindungslagen (Mz) angewendet, die für die Stromzufuhr verwendet werden. Eine eher regellose Konfiguration, die üblicherweise für das Signal-Routing in Mx- und My-Layern verwendet wird, trägt zu einer stärkeren Erwärmung der Interconnect-Layer bei.

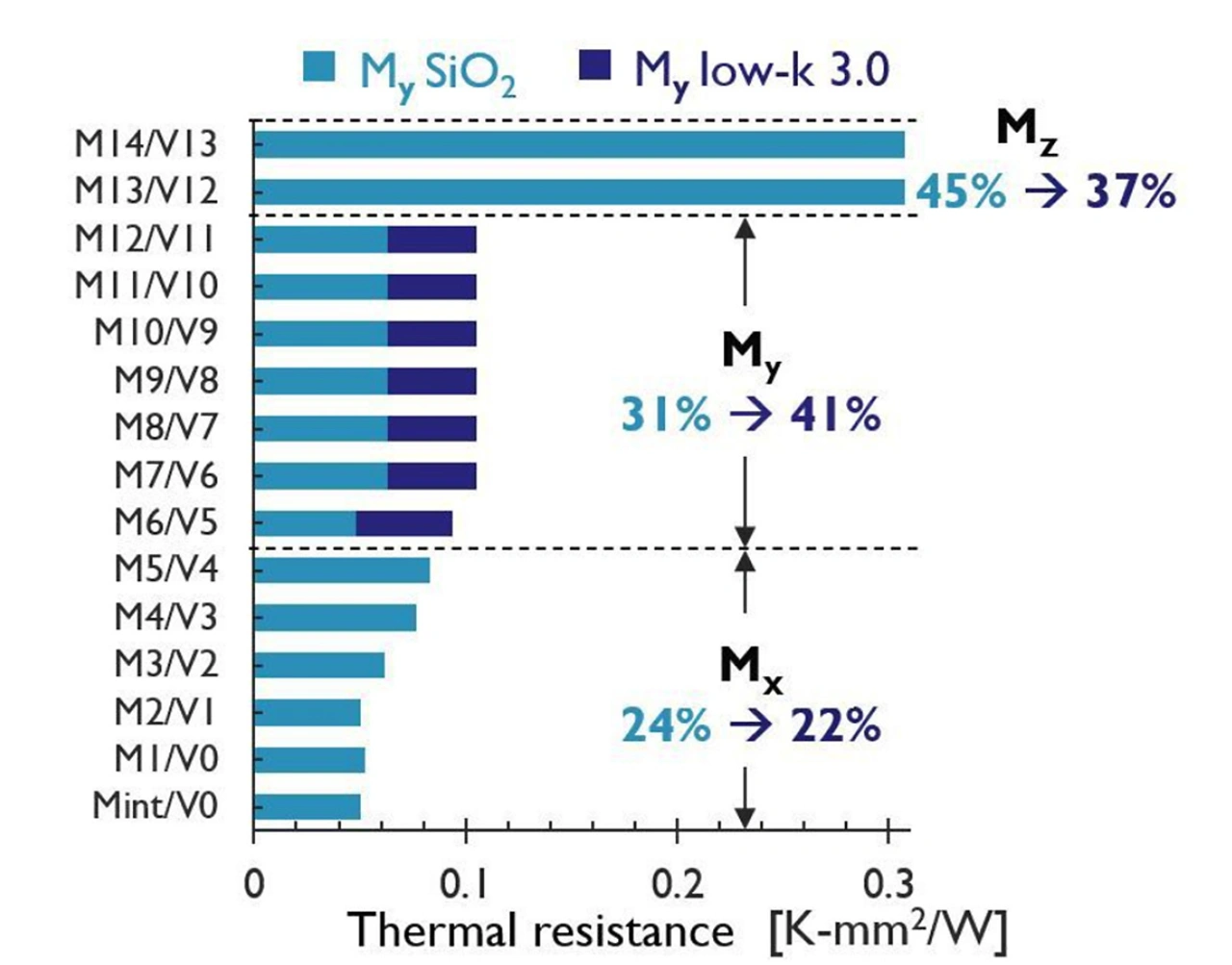

Wenn Low-k-Materialien als intermetallische Dielektrika in den My-Schichten verwendet werden, dominiert der My-Stack den thermischen Widerstand des gesamten BEOL-Stacks. Folglich bietet der My-Teil des BEOL-Stacks auch die größte Chance zur thermischen Optimierung. Die Analyse bestätigt auch den Einfluss der Via-Lagen: Bei einem 14-Layer-Stack tragen sie zu 86 Prozent des gesamten Wärmewiderstands des BEOL-Stacks bei, während die Leitungslagen nur 14 Prozent ausmachen. Man beachte, dass der Wärmewiderstand einer Lage als ihre Dicke geteilt durch die Wärmeleitfähigkeit definiert ist.

Die Wärmeübertragung zwischen FEOL und BEOL hängt stark vom Packaging und dem gewählten Kühlungsansatz ab

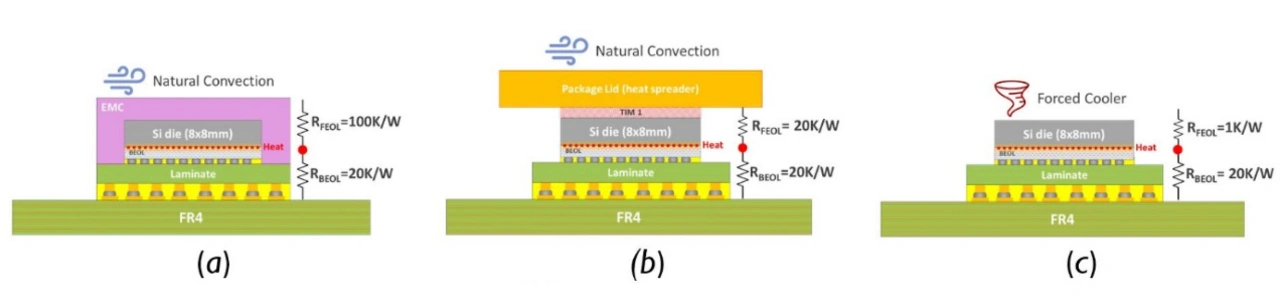

Die Temperatur der Metallleitungen ergibt sich aus der Kombination der Leitungseigenerwärmung im BEOL-Stapel und der Erwärmung im FEOL. Die zwischen FEOL und BEOL ausgetauschte Wärme hängt stark davon ab, wie der Chip gehäust ist und welche Lösung für die Kühlung des Packages vorgesehen ist - also von der Anwendung. Unser Modell wurde an drei Flip-Chip-Gehäusen mit unterschiedlichen Kühlszenarien evaluiert.

Im ersten Szenario wird ein gespritztes Flip-Chip-Gehäuse durch natürliche Konvektion von der Oberseite des Gehäuses gekühlt, die der FEOL am nächsten ist. Im zweiten Szenario wird ein Metalldeckel benutzt, um die Wärmeableitung zum oberen Teil zu verbessern. In einem dritten Fall wird die Oberseite zwangsgekühlt. Während das erste und zweite Szenario einer mobilen Anwendung ähneln, wird eine Zwangskühlung typischerweise bei Hochleistungscomputern eingesetzt.

Beim ersten Szenario wird der größte Teil der im FEOL erzeugten Wärme über das BEOL in Richtung des Laminats abgeführt, auf dem das Flip-Chip-Gehäuse montiert ist. Mit anderen Worten: Dieser Kühlungsansatz führt zu einem großen Wärmewiderstand für die FEOL und zur Selbsterhitzung der BEOL. Das zweite und das dritte Szenario verbessern den thermischen Pfad zur Oberseite, was zu einer 40-prozentigen bzw. 90-prozentigen Temperatursenkung bei gleicher FEOL-Leistung führt, während die BEOL-Eigenerwärmung nur leicht abnimmt.

Ein wertvolles Tool für STCO

Wie oben beschrieben, kann jedes der vorgestellten Modelle für bestimmte Anwendungsfälle eingesetzt werden, je nachdem, wo das Interesse liegt. So kann das FEM-Modell beispielsweise auf vereinfachte BEOL-Stapel angewendet werden, um die thermischen Aspekte fortschrittlicherer Metallisierungsschemata auf lokaler Ebene zu untersuchen, wie z.B. Semi-Damascene. Auch alternative Routing- und Stromversorgungsschemata - wie z.B. die Stromversorgung auf der Rückseite - können bewertet werden, indem verschiedene Package-Konfigurationen in das Package-Modell eingespeist werden.

Letztendlich wird die Reduzierung des thermischen Engpasses im BEOL des Chips zu Vorteilen bei der Systemleistung für die angestrebten Anwendungen führen. Die vorgeschlagenen Modelle werden dazu beitragen, die richtigen technologischen Komponenten zu identifizieren, die wichtige System-Engpässe bei der Skalierung beheben können. Sie werden wertvollen Input für die 3D- und Design-Technologie-Co-Optimierung (DTCO) von imec liefern und schließlich auch für die System-Technologie-Co-Optimierung (STCO), die von den Anforderungen der Systemanwendungen ausgeht.

Die Autoren:

Melina Lofrano ist Forschungsingenieurin in der Abteilung für thermische Modellierung und Charakterisierung beim imec. Sie erwarb einen M.Sc. in Maschinenbau an der Universität von São Paulo, Brasilien. Seit 2008 arbeitet sie beim imec in Belgien, wo sie sich mit thermischen und mechanischen Analysen für die Zuverlässigkeit von Mikro- und Nanoelektronik beschäftigt. Ihre Arbeitsgebiete umfassen mehrere Themen, darunter die thermische und thermomechanische Analyse von BEOL-Verbindungen, die 3D-IC-Montage, die Interaktion von Chipgehäusen, MEMS-Resonatoren, GaN-Resonatoren und die Charakterisierung nichtlinearer Materialien. Derzeit arbeitet sie an der thermischen Analyse für 3D-Systeme und ist für die thermische Modellierung und Charakterisierung von Nano-ICs verantwortlich.

Xinyue Chang ist Doktorantin beim imec und der KU Leuven und arbeitet an der thermischen Modellierung und experimentellen Charakterisierung von fortschrittlichen BEOL-Strukturen. Sie erhielt 2019 ihren Master-Abschluss in Elektronik und Kommunikationstechnik von der Shanghai Jiao Tong University in Shanghai, China. Kurz darauf trat sie dem Team für thermische Modellierung und Charakterisierung vom imec bei und promoviert derzeit an der KU Leuven.

Herman Oprins ist leitender technischer Mitarbeiter und Forschungsgruppenleiter beim imec, wo er dem Team für thermische Modellierung und Charakterisierung vorsteht. Er erwarb einen M.Sc. und einen Ph.D. in Maschinenbau an der KU Leuven, Belgien. Oprins kam 2003 zum imec, wo er an der experimentellen thermischen Charakterisierung, der thermischen Modellierung und an Lösungen für das Wärmemanagement von der Bauelementebene über die Chipebene bis hin zur Systemebene beteiligt war. Seine Arbeitsgebiete umfassen ein breites Spektrum elektronischer Anwendungen, darunter modernste Chip-Packages, 3D-Systemintegration, Si-Photonik, CMOS-Skalierung, BEOL-Verbindungen, GaN-Leistungstransistoren, Photovoltaikmodule und Mikrofluidik.

Zsolt Tőkei ist imec-Fellow und Programmdirektor für Nano-Verbindungen beim imec. Er kam 1999 zum imec und hat seither verschiedene technische Positionen in der Organisation bekleidet. Zunächst als Prozessingenieur und Forscher für Low-k-Kupferverbindungen, dann als Leiter der Metallsektion. Später wurde er Principal Scientist und Programmdirektor für Nano-Verbindungen. Zsolt erwarb einen M.S. (1994) in Physik an der Universität Kossuth in Debrecen, Ungarn. Im Rahmen einer gemeinsam von der ungarischen Universität Kossuth und der französischen Universität Aix Marseille-III betreuten Dissertation erwarb er seinen Doktortitel (1997) in Physik und Materialwissenschaften. Ab 1998 arbeitete er als Post-Doc am Max-Planck-Institut in Düsseldorf, Deutschland. Beim imec arbeitete er weiter an einer Reihe von Fragen der Verbindungstechnik, darunter Skalierung, Metallisierung, elektrische Charakterisierung, Modulintegration, Zuverlässigkeit und Systemaspekte.