EM-Verträglichkeit simulieren

Werkzeuge zur Simulation von Signalintegrität und elektromagnetischer Verträglichkeit

Fortsetzung des Artikels von Teil 3

EMV-Untersuchung eines Steuergeräts

Bei der untersuchten Leiterplatte handelte es sich um Varianten eines Motorsteuergerätes. Die beiden für dieses Projekt verwendeten Platinen waren bis auf eine minimale Layout- und Netzlisten-Änderung identisch. Auf ihnen sind jeweils zwei PowerPC MPC5554 zusammen mit zwei asynchronen Speichern und einem asynchronen Flash-Speicher verbaut. Sie arbeiten mit einer Taktrate von 132 MHz, während die Speicheranbindung mit maximal 20 MHz getaktet ist. Die Spannungsversorgung kommt aus dem 24-V-Bordnetz, aus ihr werden mit Hilfe von drei Spannungsreglern die für die ICs notwendigen Spannungen 1,5, 3,3 und 5 V generiert. Die Schaltregler arbeiten mit Frequenzen zwischen 400 und 750 kHz. Zudem ist ein ASIC für die Weggeber-Logik verbaut, dessen 4-MHz-Takt von einem der beiden Prozessoren zugeführt wird.

Ein Bus mit ähnlicher Taktrate ist für die Kommunikation mit dem PowerPC zuständig. Darüber hinaus ist auf der Platine eine große Anzahl an Endstufen untergebracht, die aber nur mit einer Taktrate von maximal 100 Hz betrieben werden. Die Platine besteht aus vier elektrischen Lagen. Auf der obersten Lage sind die Bauteile angebracht und gleichzeitig einige Signalpfade geführt. Auf der zweiten Lage finden sich weitere Signalleitungen, auf der dritten Lage befindet sich die komplette Spannungsversorgung der Platine, allerdings mussten aus Platzgründen noch einige Signalleitungen auf dieser Lage verlegt werden. Die unterste Lage ist eine Ground-Lage. Die sehr dünne Platine ist zur Wärmeabfuhr auf eine 3 mm dicke Aluminiumplatte geklebt. Dies ist notwendig, da die Platine für eine Umgebungstemperatur bis 110 °C ausgelegt sein soll.

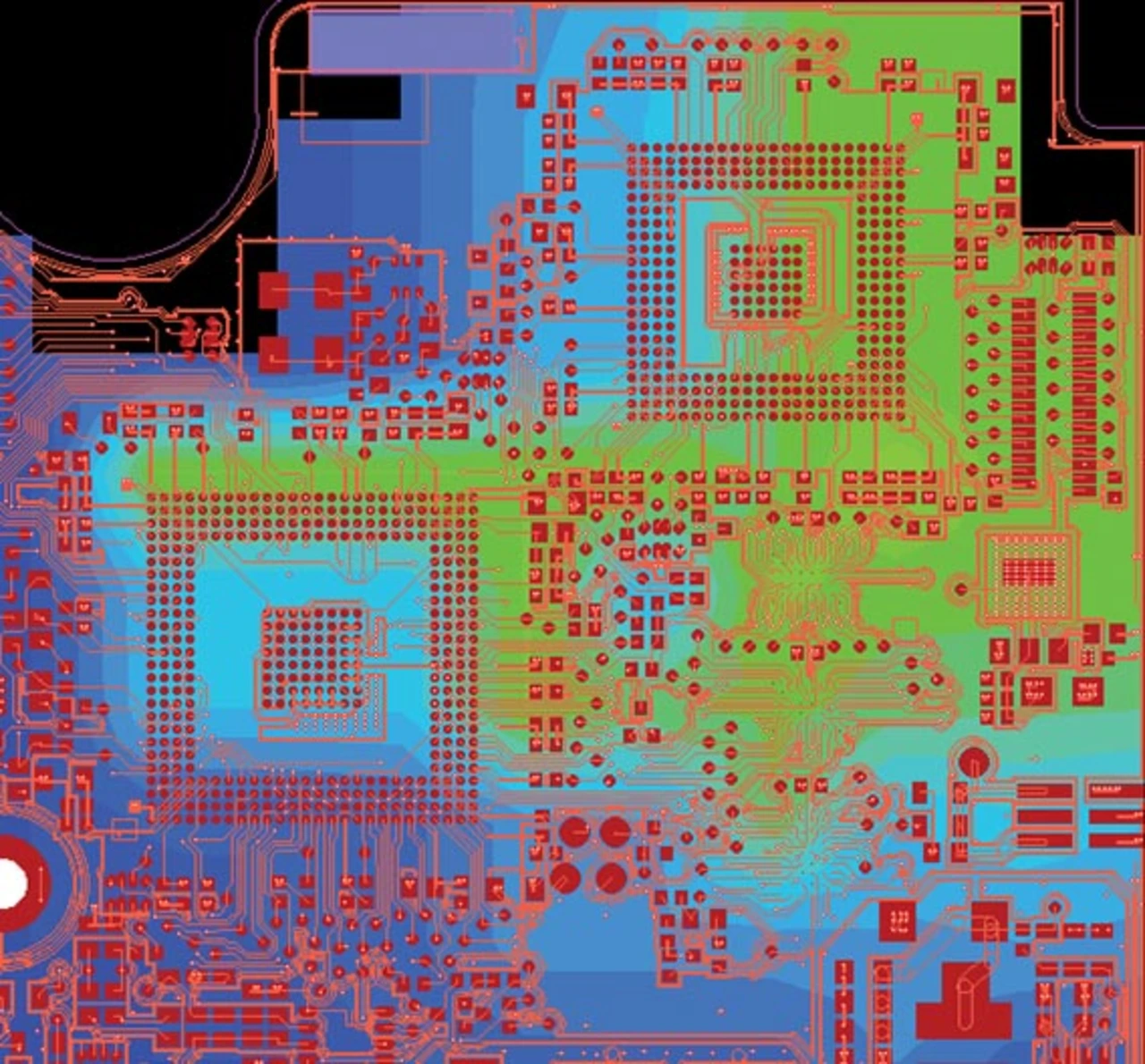

Für die EMV-Simulation wurde nach der Datenübergabe in das EMV-Simulationswerkzeug zuerst die Simulationsbibliothek hinsichtlich der auf der Platine angeschlossenen Bauteile erweitert. Für den PowerPC und für die Speicher konnte auf IBIS-Modelle der Bauteilhersteller zurückgegriffen werden. Die Bauteile, für die keine vorgefertigten Modelle existierten, wurden anhand der Datenblätter durch eigene Modelle nachgebildet (Bild 2).

Die auf der Platine verbauten Stecker X7 und X8 sind nur für die Programmierung der beiden Power PCs zuständig, für die Simulation wurden sie als inaktiv modelliert. Die in der Simulation als starke potentielle Strahler detektierten Netze sind die Anbindungen der Speicherbausteine. Dies ist mit einer theoretischen Betrachtung plausibel zu erklären: Hier treten nicht nur mit 20 MHz die höchsten Frequenzen der Platine auf, sondern auch die Flanken-Anstiegs-/Abfallzeiten, die der MPC-5554 aufweist, sind hier mit 0,33 ns sehr kurz. Zudem kommt hinzu, dass bei der Speicheranbindung sehr viele Leiterbahnen eng zusammenliegen, wodurch starkes Übersprechen auftritt und die Störungen noch verstärkt werden. Die niedrigeren Linien, die im Spektrum bis etwa 600 MHz zu erkennen sind, haben einen Abstand von 4 MHz. Sie werden von der Kommunikation mit dem ASIC verursacht.

- Werkzeuge zur Simulation von Signalintegrität und elektromagnetischer Verträglichkeit

- Störungsanalyse von Leiterplatten

- Stromversorgungen als parasitäre Antennen

- EMV-Untersuchung eines Steuergeräts

- Übersprecheffekte und Stecker, Simulation und messtechnische Verifikation

- Untersuchung der Stromversorgungssysteme

- Optimiertes Versorgungskonzept und Einsparung von Abblockkondensatoren

- Aussagekräftige Ergebnisse innerhalb von Stunden