Elektromobilität

Chips für Ladestationen

Fortsetzung des Artikels von Teil 2

Systemsicherheit erhöhen

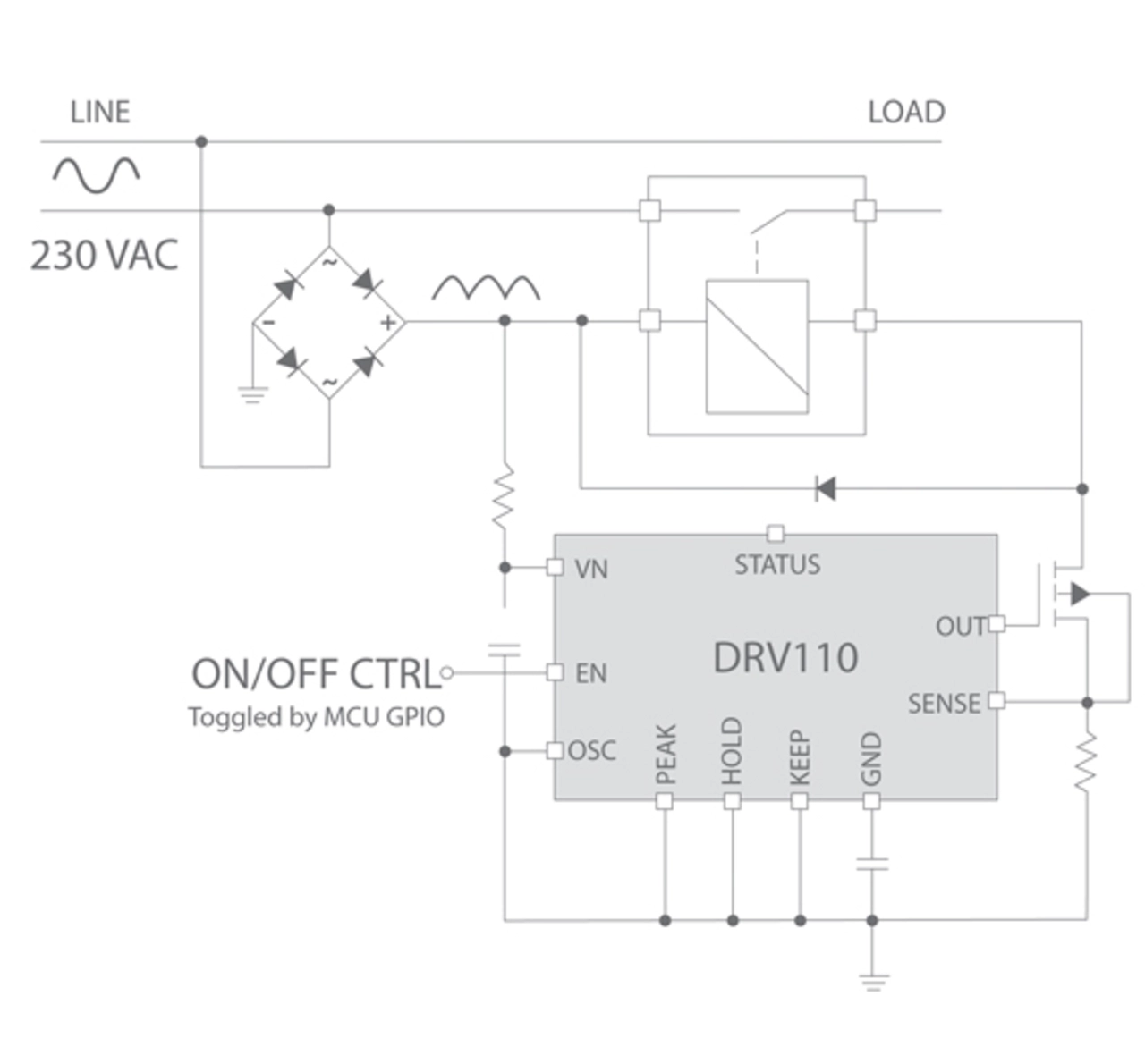

Die Systemsicherheit lässt sich durch ein Überstromschutzkonzept erhöhen. Dazu nutzt man die integrierten analogen Komparatoren des Mikrocontrollers, deren Ausgänge mit einem Standard-GPIO verbunden werden, so lässt sich im Verbund mit dem Relaistreiber »DRV110« und einem mechanischen Relais der Haupt-Ladebus im Fehlerfall trennen (Bild 3). Gleichzeitig wird die stromsparende Architektur beibehalten und die Zahl der benötigten externen Bauelemente reduziert.

In der Architektur des Mikrocontrollers findet sich darüber hinaus eine Reihe weiterer Elemente, mit denen sich die allgemeine Systemsicherheit weiter verbessern lässt. Da der Baustein aus zwei unabhängigen CPUs besteht, kann jeweils einer der beiden nach einem bestimmten Plan die korrekte Funktion des jeweils anderen überprüfen. Darüber hinaus lassen sich kritische Berechnungen von beiden Prozessoren parallel ausführen und auf Korrektheit überprüfen, bevor das System dieses Ergebnis weiterverwendet. Eine ähnliche Prüfmethode kommt auch für die digitalen und analogen I/O-Module des Mikrocontrollers infrage. Kritische Systemsignale lassen sich an mehrere I/O-Module des Mikrocontrollers richten, um die Resultate der einzelnen Module anschließend auf Richtigkeit zu überprüfen.

Weitere Methoden, die Systemsicherheit zu steigern, sind beispielsweise die Aktivierung der integrierten, hardwaremäßigen Speicherprüfmechanismen wie zum Beispiel ECC (Error Correcting Code). Viele hardwaremäßige ECC-Implementierungen können Einzelbitfehler im Speicher automatisch erkennen und korrigieren. Darüber hinaus können sie Doppelbitfehler detektieren und melden.

Überaus kritisch für den korrekten Betrieb von Mikrocontrollern sind auch die Taktsignale. Eine integrierte Logik kann Taktausfälle erkennen. Schwankungen der Stromversorgung können überdies Fehlfunktionen auslösen und das System zu einem unvorhergesehenen Verhalten veranlassen. Für die Systemsicherheit ist es deshalb wichtig, die Power-Monitoring-Schaltungen zu nutzen und die Brown-out-Reset- und -Recovery-Funktion zu nutzen.

Als nächstes Glied der Signalverarbeitungskette folgt die Zahlungsabwicklung. Wenn ein Baustein einen industriestandardgemäßen ARM Cortex-M3-Core enthält, kann der Hauptcontroller diese Zahlungsabwicklungsdienste selber abwickeln. Die primären Arten der Abwicklung sind entweder die direkte Bezahlung per Kreditkarte oder Bargeld oder per NFC und Smartphone. Die Verarbeitung von Kreditkartendaten steigert unmittelbar den Bedarf an Rechenleistung, die jedoch ein ARM Cortex-M3 ebenso wie viele andere Mikrocontroller bieten. Zum Beispiel kann dessen ADC-Eingang die Kreditkarte direkt von einem Magnetlesekopf auslesen. Lösungen zum Dekodieren der Informationen auf dem Magnetstreifen sind umgehend verfügbar, doch ebenso kommt die Eigenentwicklung einer solchen Lösung infrage. Rein technisch lassen sich Systeme zur Annahme von Geldscheinen oder Münzen mit einem solchen Rechenkern implementieren.

- Chips für Ladestationen

- Unterschiedliche Designanforderungen

- Systemsicherheit erhöhen

- Integration der Zahlungsabwicklung