All-in-One-Controller von Analog Devices

Integriert und isoliert für energieeffiziente Durchflusswandler

Fortsetzung des Artikels von Teil 1

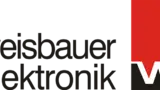

Vollständiger Schaltplan mit wenigen Komponenten

Nur wenige externe Komponenten sind notwendig, um einen hocheffizienten Durchflusswandler mit Hilfe des ADP1074 zu bauen (Bild 2). Auf der primären Seite wird ein N-MOSFET als Hauptschalter und ein P-MOSFET für die aktive Klemmung verwendet. Auf der sekundären Seite werden zwei N-MOSFETs für die synchrone Gleichrichtung benötigt.

Der Controller beinhaltet auf der primären Seite Gate-Treiber für die Ansteuerung des Hauptschalters (NMOS) und des Aktive-Klemmung-Schalters (PMOS). Auf der sekundären Seite sind zwei Gate-Treiber integriert. Die Totzeiten zwischen NMOS, PMOS und SR2 können mit einem Widerstand zwischen NGATE und GND in vier Stufen bestimmt werden. Dadurch kann der resonante Schaltvorgang (ZVS) zwischen NMOS und PMOS sowie optimales Schalten der SR1/2 erreicht werden.

Ein Spannungsteiler bestimmt die minimale Einschaltspannung am Eingang des Wandlers. Eine präzise Referenz und eine einstellbare Hysterese sorgen für einen sehr stabilen Anlauf. Um einen Betrieb an höheren Eingangsspannungen (zum Beispiel 400 V) mit geringem Anlaufstrom zu realisieren, können externe Anlaufschaltungen verwendet werden. Der primäre Chip IC1 ist so konzipiert, dass unterschiedliche externe Anlaufschaltungen mit geringer Stromaufnahme realisiert werden können. Die Strombegrenzung der primären Seite wird mit dem Shunt-Widerstand RSense realisiert, während die Rampensteilheit des Kompensators mit RRamp bestimmt wird.

Die Arbeitsfrequenz und das maximale Tastverhältnis können mit zwei in Reihe geschalteten Widerständen bestimmt werden.

Auf der sekundären Seite werden die Parameter des Kompensators der Regelschleife mit dem Pin Comp programmiert. Die Höhe der Ausgangsspannung wird mit Hilfe eines Spannungsteilers am Pin FB eingestellt. Eine separate, unabhängige Überspannungsüberwachung wird mit einem anderen Spannungsteiler am Pin OVP vorgenommen.

Verhalten beim Ein- und Ausschalten

Die Anlaufgeschwindigkeit beim Einschalten des Controllers wird sowohl auf der primären als auch auf der sekundären Seite programmiert. Für den Anlauf der Signale für den Hauptschalter ist CSS1 verantwortlich, während CSS2 für das weiche Einphasen der synchronen Gleichrichter dient. In der ersten Periode des Anlaufvorgangs wird das Tastverhältnis des PWM linear erhöht mit einer Steilheit, die von CSS1 und RSense bestimmt wird. Da IC2 in dieser Zeit noch nicht aktiv ist, arbeitet der Controller mit offener Regelschleife. Wenn IC2 aktiviert wird, beginnt ein mehrstufiger Prozess, in dem die Regelschleife geschlossen wird und die synchronen Gleichrichter mit einer programmierten Rampe aktiviert werden. Nach Beginn des Anlaufprozesses der sekundären Seite wird sofort die Ausgangsspannung gemessen. Sollte die Spannung vor dem Anlaufen schon einen Wert über dem der Anlaufschwelle (UVLO) haben, werden die synchronen Gleichrichter erst dann angesteuert, wenn die Spannung an CSS2 den Wert der Ausgangsspannung überschreitet. Dadurch wird vermieden, dass ein unkontrollierbarer, hoher Rückwärtsstrom fließt, der die Zerstörung der MOSFETs verursachen könnte.

Ein programmierter Soft-Stopp ist möglich. Die Ausgangsspannung wird im Takt der Absenkung der Spannung an CSS2 reduziert. CSS2 wird mit Hilfe einer konstanten Stromquelle entladen.

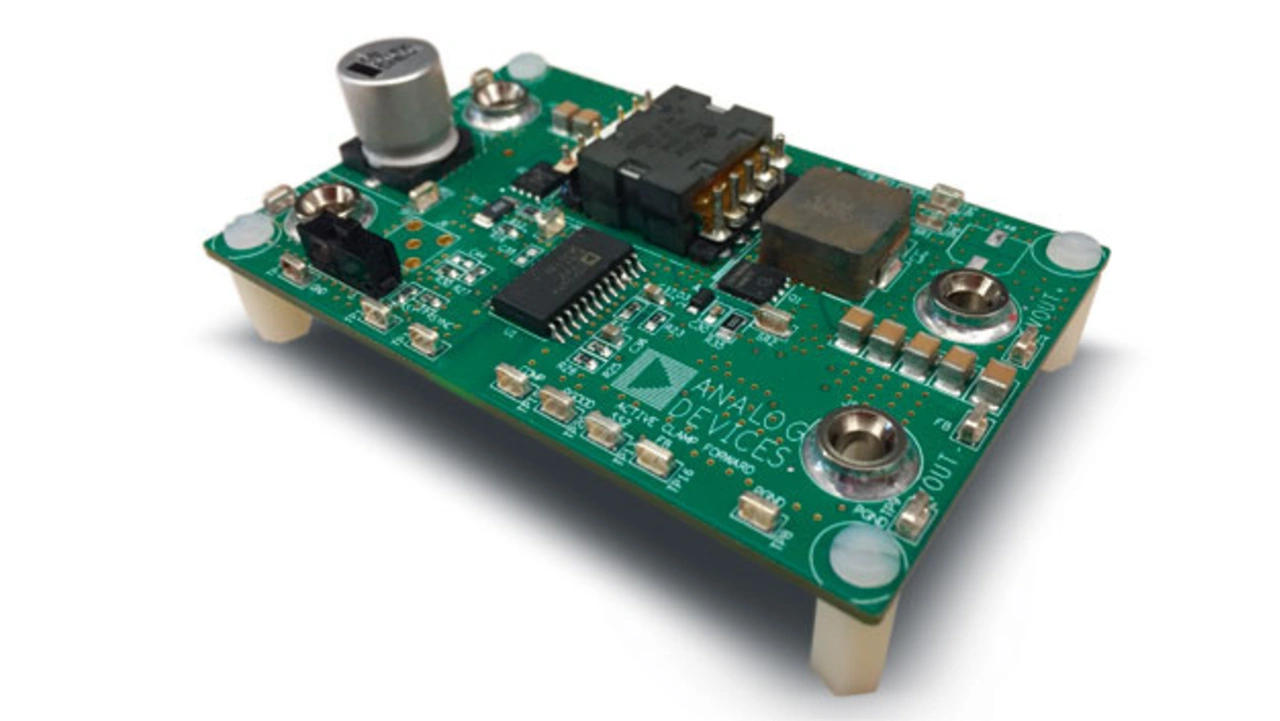

Teillast-Management verbessert den Wirkungsgrad

Der ADP1074 (Bild 4) wurde konzipiert, um Wandler mit hohem Wirkungsgrad zu bauen. Nicht nur der Aktive-Klemmung-Schalter auf der primären Seite und die synchronen Gleichrichter auf der sekundären Seite, sondern auch ein intelligentes Teillast-Management tragen zum hohen Wirkungsgrad in einem weiten Lastbereich bei (Bild 3).

Mit dem multifunktionalen Pin „Mode“ kann der Betrieb CCM (Continuous Conduction Mode), DCM (Discontinuous Conduction Mode) und die Schwelle für das Abschalten der synchronen Gleichrichter programmiert werden. Unterschreitet der Ausgangsstrom diese Schwelle, so werden die SRs deaktiert. Unterschreitet der Ausgangsstrom eine zweite, interne Schwelle, so geht der Controller in den Burst Mode über. Bei Lastsprüngen wird die Ansteuerung der SRs nur mit einer eingestellten Geschwindigkeit vorgenommen, um das optimale dynamische Verhalten zu erzielen und um reversen Strom zu vermeiden.

Der Autor

| Bernhard Strzalkowski |

|---|

| studierte Elektrotechnik an der Technischen Universität Gliwice/Polen und Karlsruhe/Deutschland. Er promovierte 1999–2003 auf dem Gebiet digitaler Koppler. Von 1989 bis 96 entwickelte er unterschiedliche Inverter und Konverter für Windkraftanlagen, elektrische und Hybrid-Fahrzeuge sowie Schiffe bei Magnet Motor/Starnberg. Von 1997 bis 2009 arbeitete er an der Entwicklung von Hochspannungstechnologie und Steuer-ICs für industrielle Anwendungen bei Siemens/Infineon in München. Seit 2009 beschäftigt er sich mit der Entwicklung und der Anwendung digitaler Power Controller bei Analog Devices/München. Er ist Mitglied von Normgremien bei VDE/IEC und hat zahlreiche Patente auf dem Gebiet Leistungselektronik. |

- Integriert und isoliert für energieeffiziente Durchflusswandler

- Vollständiger Schaltplan mit wenigen Komponenten