Design von Schaltwandlern

»Hot Loops« optimieren

Fortsetzung des Artikels von Teil 1

Größe und Platzierung der MOSFETs

Bei diskreten Designs beeinflussen die Platzierung und die Gehäuseabmessungen der verwendeten Leistungs-FETs die ESR- und ESL-Werte der kritischen Schleifen ebenfalls signifikant. Um dies zu verdeutlichen, wird in diesem Abschnitt eine typische Halbbrücke bestehend aus den Leistungs-FETs M1 und M2 sowie dem Entkopplungskondensator CIN modelliert und untersucht.

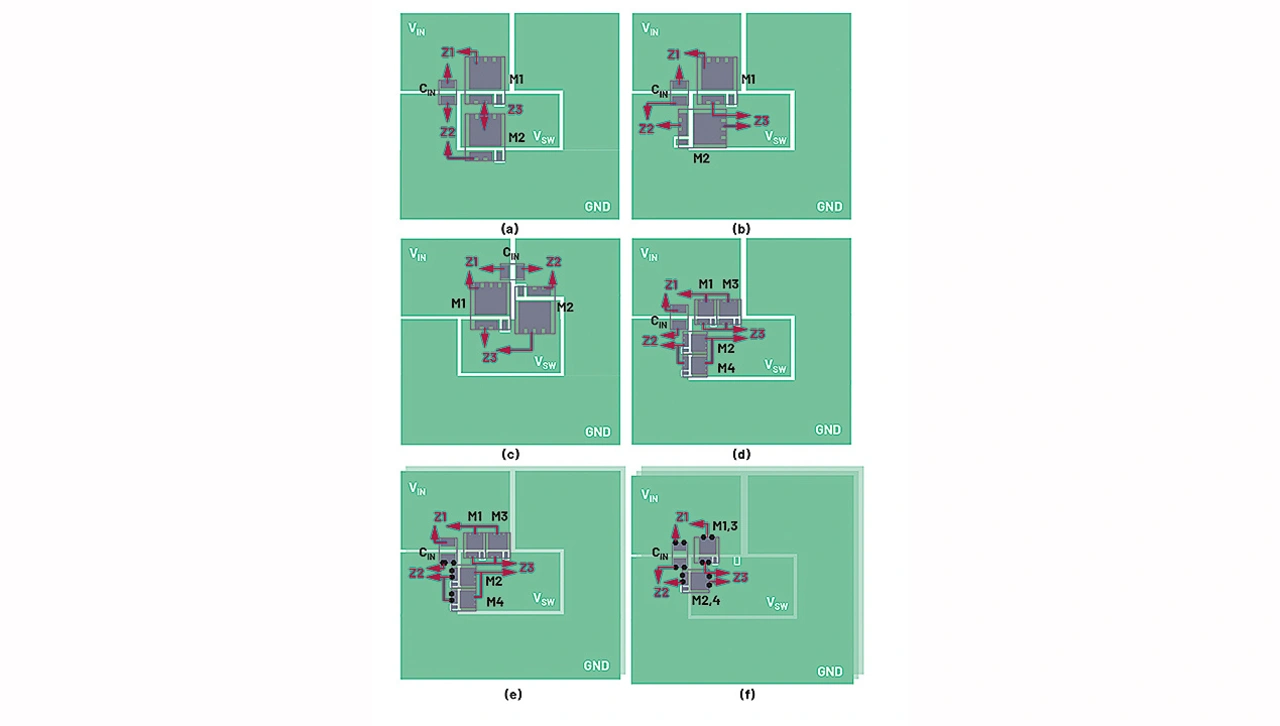

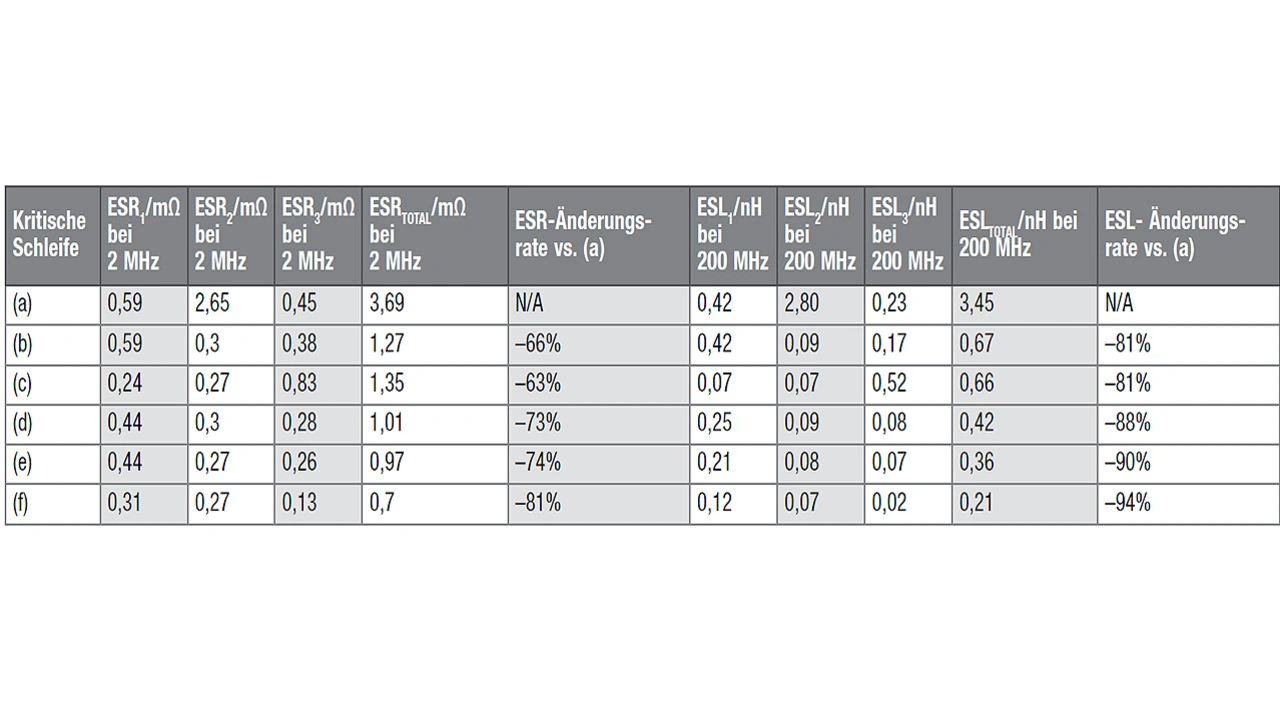

Im Einzelnen wurden gängige Gehäusegrößen von Leistungs-FETs sowie unterschiedliche Platzierungsvarianten verglichen (Bild 6). Die dabei extrahierten ESR- und ESL-Werte sind aus Tabelle 2 zu entnehmen. Die Fälle (a) bis (c) sind drei populäre Platzierungsvarianten mit 5 mm × 6 mm großen MOSFETs. Die parasitäre Impedanz bestimmt sich hier aus der physischen Länge der kritischen Schleife

Folglich reduzieren sowohl die 90°-Platzierung (b) als auch die 180°-Variante (c) den ESR um 60 Prozent sowie den ESL um 80 Prozent, weil die Schleifen schlicht kürzer sind als bei Variante (a).

Da der Vorteil bereits bei der 90°-Platzierung zum Tragen kommt, werden auf der Basis von Variante (b) mehrere weitere Varianten untersucht, um die ESR- und ESL-Werte weiter zu drücken. In Variante (d) wird der 5 mm × 6 mm große MOSFET durch zwei parallelgeschaltete 3,3 mm × 3,3 mm große Bausteine ersetzt. Wegen der kleineren Abmessungen der MOSFETs sinkt die Schleifenlänge weiter und damit auch deren Impedanz um sieben Prozent. Befindet sich eine Massefläche unter der Lage mit der kritischen Schleife, Variante (e), fallen die parasitären Widerstände und Induktivitäten noch einmal um zwei Prozent kleiner aus als bei Variante (d). Ursache hierfür ist, dass in der Massefläche Wirbelströme induziert werden, die ein entgegengesetztes Magnetfeld erzeugen und so die Schleifenimpedanz entsprechend reduzieren.

In Variante (f) befindet sich auf der Unterseite der Platine eine weitere Lage für die kritische Schleife. Sind auf der oberen und der unteren Lage zwei parallelgeschaltete MOSFETs symmetrisch angeordnet und über Vias miteinander verbunden, reduzieren sich ESR und ESL wegen der parallelen Impedanz noch weiter. Kleinere, in einem Winkel von 90° oder 180° auf der Ober- und Unterseite der Leiterplatte platzierte Bausteine ergeben somit die niedrigsten Werte für ESR und ESL.

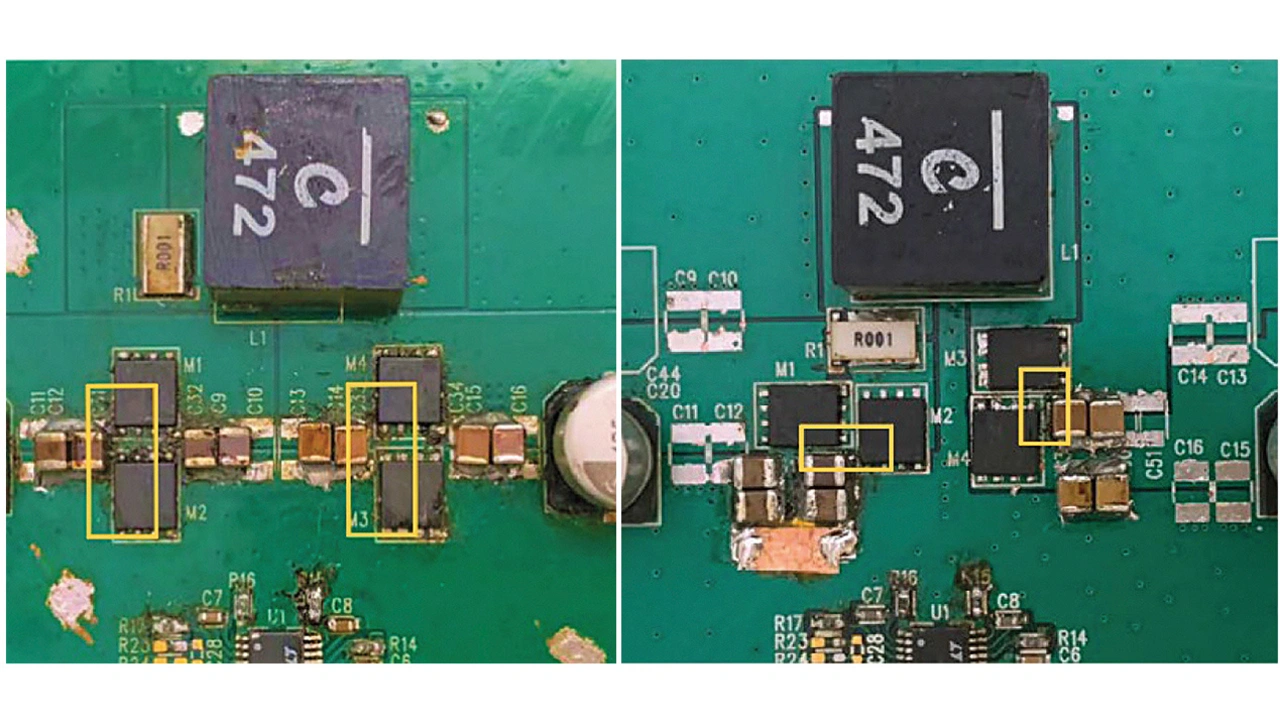

Mit dem Ziel, die Auswirkungen der MOSFET-Platzierung experimentell zu verifizieren, wurden die Demo-Boards DC2825A (bestückt mit dem LT8390) und DC2626A (auf Basis des LT8392) verwendet, bei denen es sich um aus vier Schaltern bestehende Buck-Boost-Controller handelt [4]. Wie aus Bild 7 zu entnehmen ist, sind die MOSFETs auf dem DC2825A gerade und auf dem DC2626A in einem Winkel von 90° angeordnet.

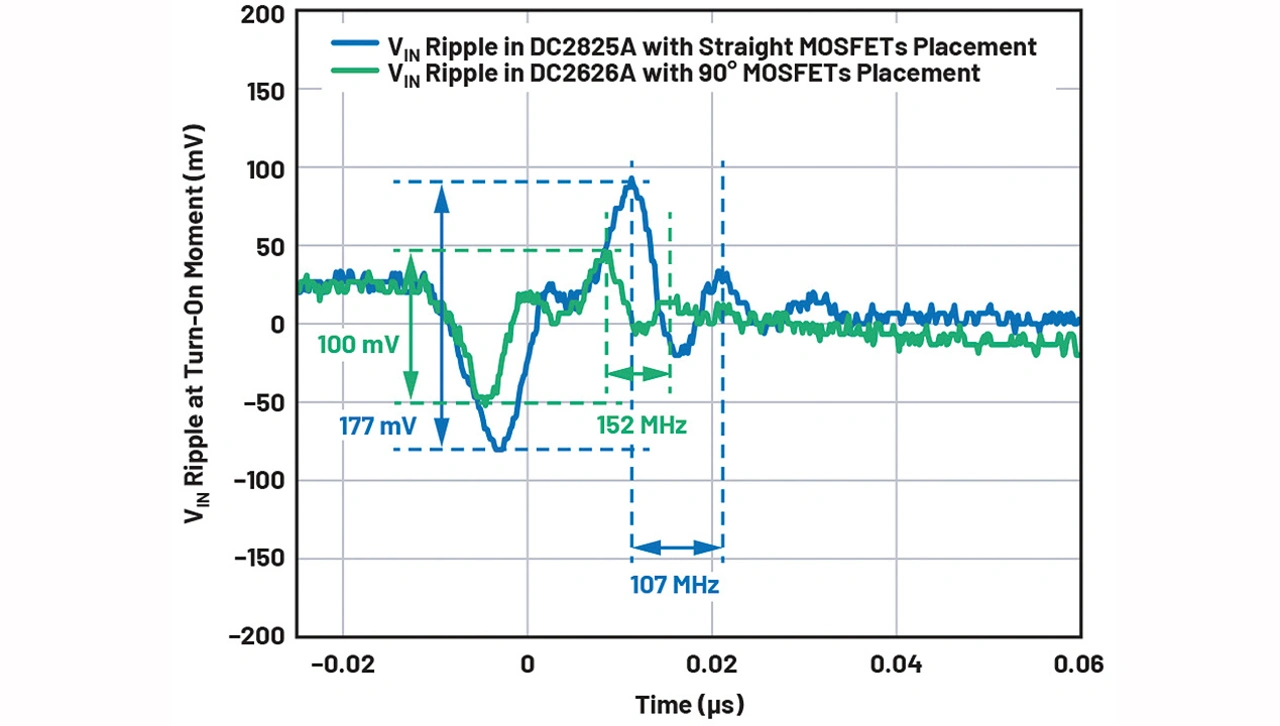

Um gleiche Bedingungen zu erhalten, wurden beide Demo-Boards mit identischen MOSFETs und Entkopplungskondensatoren bestückt und als Tiefsetzsteller (36 V auf 10 V) mit 10 A Laststrom und einer Schaltfrequenz von 300 kHz getestet. Bild 8 zeigt die Schwingung von VIN, wenn M1 einschaltet. Sind die MOSFETs im 90°-Winkel platziert, ist die Amplitude kleiner, während die Schwingfrequenz höher ist. Hieran lässt sich erkennen, dass die parasitäre Induktivität der Leiterplatte infolge der geringeren Schleifenlänge niedriger ist. Sind die MOSFETs gerade angeordnet, ist die kritische Schleife länger und die parasitäre Induktivität entsprechend höher. Daher ist die Amplitude der Schwingung von VIN höher und die Resonanzfrequenz niedriger. Ist die Amplitude höher, steigt auch die Störabstrahlung [4].

Einfluss der Via-Platzierung

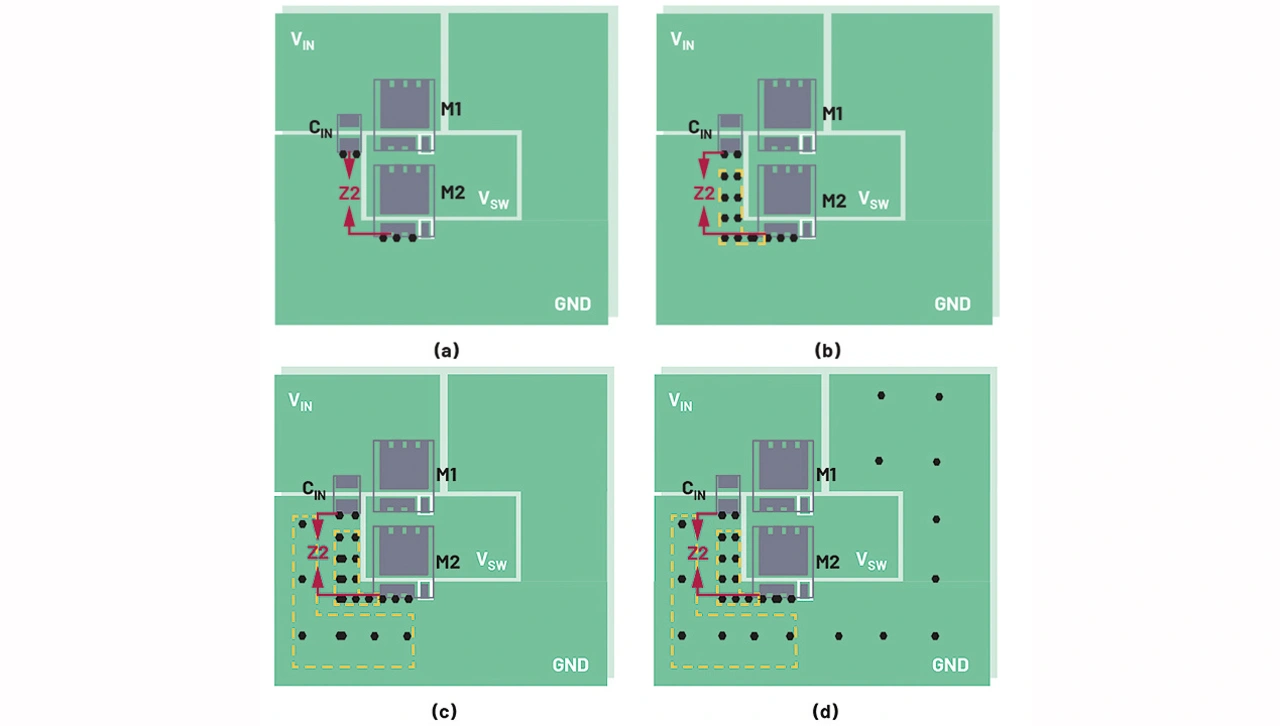

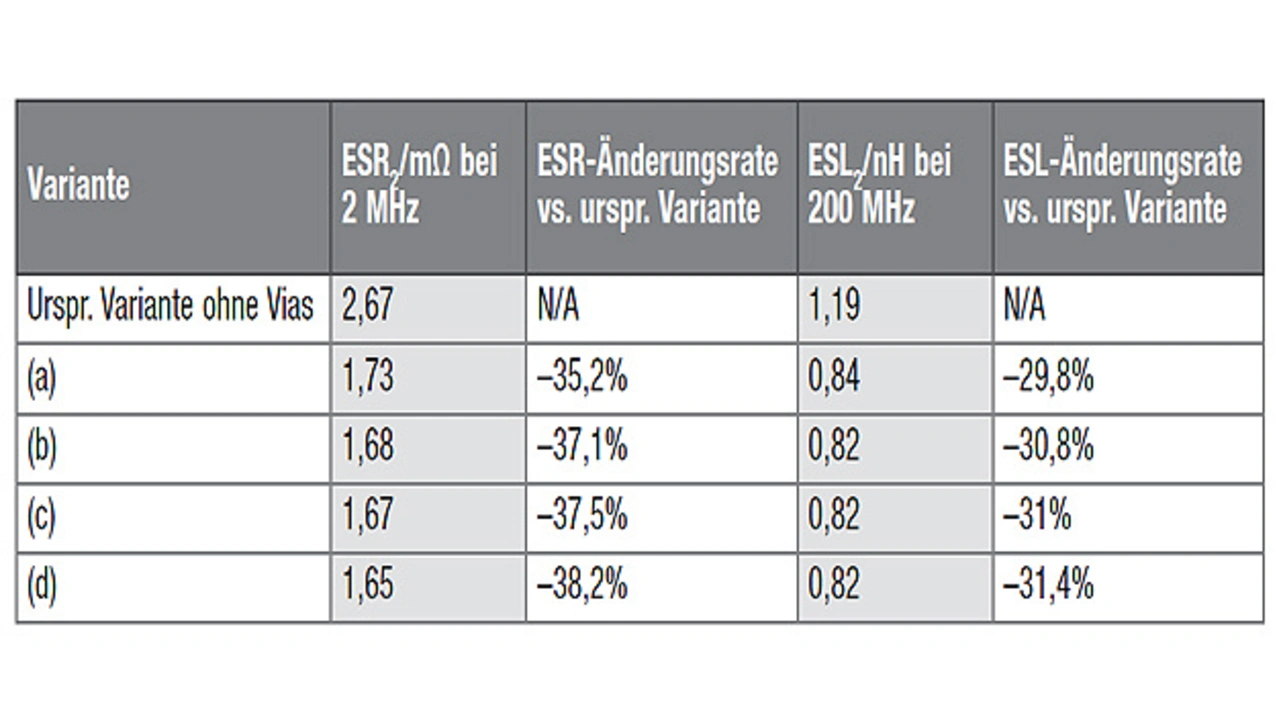

Die Platzierung der Durchkontaktierungen (Vias) in der kritischen Schleife wirkt sich ebenfalls signifikant auf Streuwiderstände und -induktivitäten aus. Bild 9 zeigt die kritische Schleife bei einer zweilagigen Leiterplatte und gerader Platzierung der MOSFETs auf der oberen Lage, während die untere Lage als Massefläche dient. Die parasitäre Impedanz zwischen dem GND-Pad von CIN und dem Source-Pad von M2 ist Teil der kritischen Schleife und wird im Folgenden exemplarisch untersucht, indem diese mithilfe von FastHenry extrahiert wird. Tabelle 3 fasst die simulierten Werte für ESR2 und ESL2 für verschiedene Via-Platzierungsvarianten zusammen.

Generell gilt, dass die parasitäre Impedanz der Leiterplatte umso geringer ist, je mehr Vias hinzugefügt werden. Dennoch sinken ESR2 und ESL2 nicht einfach proportional zur Anzahl der Vias.

Vielmehr verringern die nahe an den Anschluss-Pads befindlichen Vias die Streuimpedanzen am deutlichsten. Beim Layout der kritischen Schleife müssen deshalb mehrere wichtige Vias in unmittelbarer Nähe der Anschlüsse des Entkoppelkondensators CIN und der MOSFETs angeordnet werden, um die Impedanz zu senken.Tabelle 3 fasst die simulierten Werte für ESR2 und ESL2 für verschiedene Via-Platzierungsvarianten zusammen.

Generell gilt, dass die parasitäre Impedanz der Leiterplatte umso geringer ist, je mehr Vias hinzugefügt werden. Dennoch sinken ESR2 und ESL2 nicht einfach proportional zur Anzahl der Vias. Vielmehr verringern die nahe an den Anschluss-Pads befindlichen Vias die Streuimpedanzen am deutlichsten. Beim Layout der kritischen Schleife müssen deshalb mehrere wichtige Vias in unmittelbarer Nähe der Anschlüsse des Entkoppelkondensators CIN und der MOSFETs angeordnet werden, um die Impedanz zu senken.

Zusammenfassung

Wenn man die Streuparameter von kritischen Schleifen reduziert, lässt sich der Wirkungsgrad verbessern und die Störabstrahlung eindämmen. Der vorliegende Artikel hat geklärt, wie gut sich verschiedene Platzierungen der Entkopplungskondensatoren, unterschiedliche Größen und Positionierungen der MOSFETs sowie verschiedene Via-Platzierungsvarianten eignen, die Parameter von kritischen Schleifen auf der Leiterplatte zu minimieren. Wie sich dabei gezeigt hat, ergeben kürzere Schleifen, kleinere MOSFETs, eine symmetrische Platzierung der MOSFETs in einem Winkel von 90° oder 180° sowie Vias in unmittelbarer Nähe wichtiger Bauelemente insgesamt die besten Resultate.

Literatur

[1] M. Kamon, et al., »FASTHENRY: a multipole-accelerated 3-D inductance extraction program,« IEEE Transactions on Microwave Theory and Techniques, vol. 42, no. 9, pp. 1750-1758, Sept. 1994, doi: 10.1109/22.310584.

[2] A. Musing, et al., »Efficient Calculation of Non-Orthogonal Partial Elements for the PEEC Method«, in IEEE Transactions on Magnetics, vol. 45, no. 3, pp. 1140-1143, March 2009, doi: 10.1109/TMAG.2009.2012655.

[3] R. Ren, et al., »Bridging Gaps in Paper Design Considering Impacts of Switching Speed and Power-loop Layout,« 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 2020, pp. 1992-1999, doi: 10.1109/ECCE44975.2020.9236426.

[4] Y. Cho, K. Szolusha: »4-Switch Buck-Boost Controller Layout for Low Emissions—Single Hot Loop vs. Dual Hot Loop«, Analog Dialogue, Vol. 55, Analog Devices, Juli 2021.

[5] H. Zhang: »PCB Layout Consideration for Non-Isolated Switching Power Supplies«, Application Note AN-136, Analog Devices, Juni 2012.

[6] Ch. Kück: »Power Supply Layout and EMI«, Application Note AN-139, Analog Devices, Oktober 2012.

Die Autoren

Dr. Jingjing Sun

arbeitet als Senior Applications Engineer im Support für μModule-Produkte in Multimarket-Anwendungen. Sie promovierte an der University of Tennessee in Knoxville im Bereich Elektrotechnik und kam anschließend zur Power Product Group von Analog Devices in der California Bay Area

Dr. Ling Jiang

arbeitet als Applications Manager im Support für μModule-Produkte in Multimarket-Anwendungen. Sie promovierte der University of Tennessee in Knoxville im Bereich Elektrotechnik und kam anschließend zur Power Product Group von Analog Devices in der California Bay Area.

Dr. Henry Zhang

arbeitet als Applications Director bei Analog Devices. Er machte 1994 an der Zhejiang-Universität in China seinen Bachelor-Abschluss in Elektrotechnik. 1998 bzw. 2001 folgten der Master-Abschluss und die Promotion in Elektrotechnik am Virginia Polytechnic Institute der State University in Blacksburg. Seit 2001 ist Zhang bei Linear Technology bzw. Analog Devices.

- »Hot Loops« optimieren

- Größe und Platzierung der MOSFETs