Applied Materials

Verdrahtungs-Flaschenhals beseitigt

Der neuste Prozess von Applied Materials verringert den Widerstand der Verdrahtung auf ICs um 50 Prozent, was zu deutlich gesteigerter Leistungsfähigkeit und geringerer Leistungsaufnahme führt.

Das erlaubt es erst, den Leistungsgewinn der Transistoren aufgrund der Fortschritte in der Lithografie tatsächlich in höhere Leistungsfähigkeit des gesamten ICs umzusetzen. Denn es würde wenig helfen, wenn die schnelleren Schaltgeschwindigkeiten der winzigen Transistoren durch den hohen Widerstand der Leiterbahnen auf den ICs wieder aufgefressen würde. Tatsächlich hat die Verdrahtung bisher den Flaschenhals auf den ICs gebildet, weil kleinere Strukturgrößen unweigerlich zu einer Erhöhung des Widerstandes der Leiterbahnen führen: Unter Verwendung der herkömmlichen Technik würde sich der Widerstand der Leiterbahnen von 3-nm-ICs gegenüber denen auf 7-nm-ICs um den Faktor 10 erhöhen. Im Gegensatz zu den Transistoren profitieren die elektrischen Verbindungen zwischen ihnen nicht von schrumpfenden Strukturgrößen, genau das Gegenteil ist der Fall.

Jobangebote+ passend zum Thema

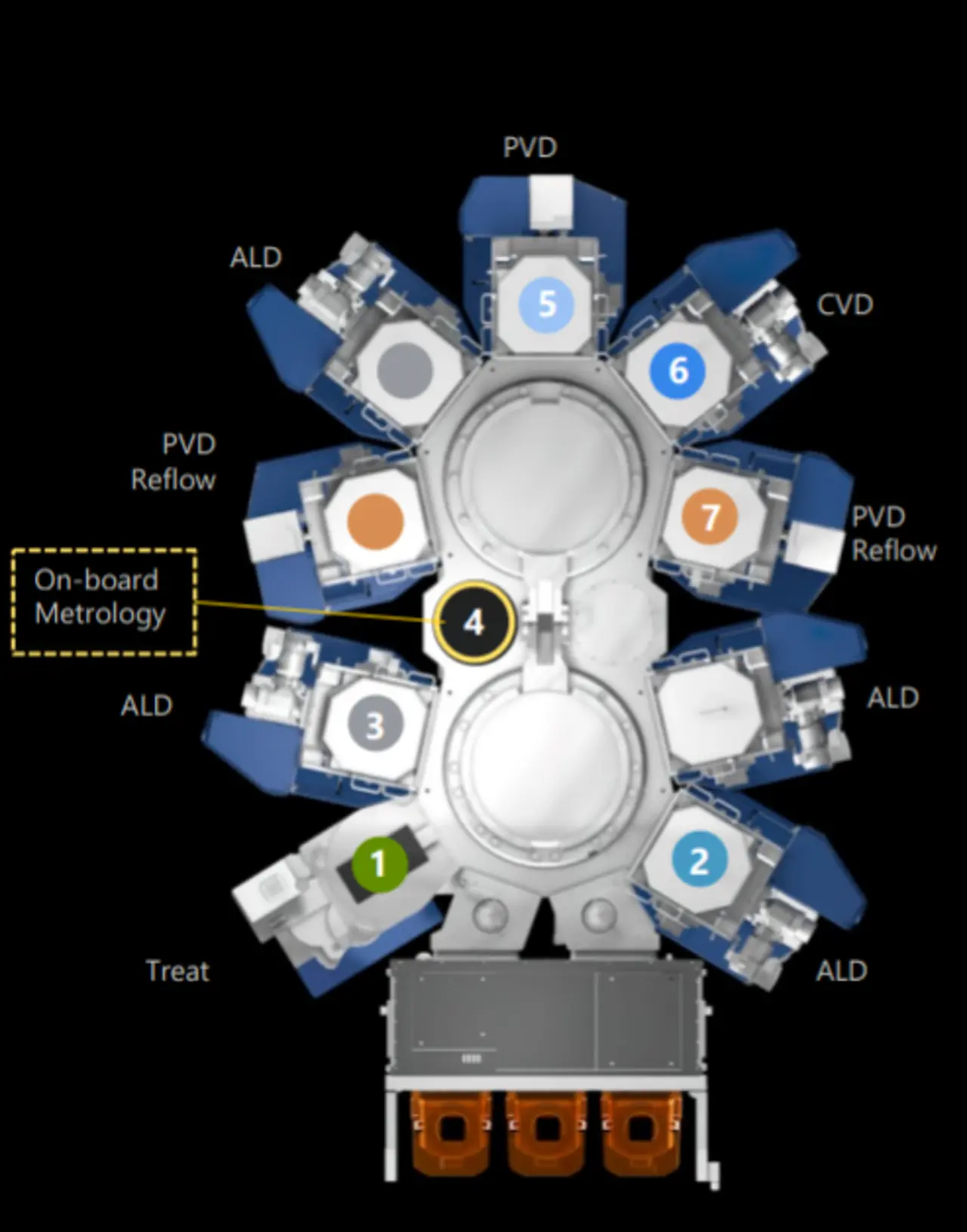

Applied Materials hat jetzt einen neuen Prozess mit neuen Materialien entwickelt, um diesem Dilemma zu entkommen und ihn auf den Namen »Endura Copper Barrier Seed IMS« getauft. Das klingt kompliziert und kompliziert ist der Prozess tatsächlich: Es handelt sich um eine Kombination aus Atomic Layer Deposition (ALD), Physical Vapor Depostion (PVD), Chemical Vapor Depostion (CVD) und Copper Reflow. Dazu kommen noch spezielle Oberflächenbehandlungen sowie spezielle Metrologie-Techniken. Das Ganze findet in einer einzigen Maschine unter Vakuumbedingungen statt. Die Verwendung eines selektiven ALD-Prozesses macht es überflüssig, die Via-Übergänge mit einer Barrier-Layer zu versehen, die den Nachteil hat, einen hohen elektrischen Widerstand aufzuweisen. Die neue Copper-Reflow-Technik erlaubt es, auch sehr enge Gräben durchgehend mit Kupfer auszufüllen, ohne dass Leerstellen entstehen.

»Ein typischer Prozessor für Smartphones enthält Milliarden von Kupfer-Übergängen, die Verdrahtung schluckt ein Drittel der gesamten Leistungsaufnahme eines Chips«, sagt Prabu Raja, Senior Vice President und General Manager der Semiconductor Products Group von Applied Materials. Die Integration verschiedener Prozesstechnologien hätte es ermöglicht, neue Materialien zu verwenden und neue Strukturen aufbauen zu können, die schlussendlich dazu führen, dass die Endanwender sich über eine höhere Leistungsfähigkeit und eine längere Batterielebensdauer ihrer Geräte freuen können.