Künstliche Intelligenz

Welche Prozessorarchitektur eignet sich am besten?

Fortsetzung des Artikels von Teil 1

Grafikprozessoren

Um qualitativ hochwertige Bilder zu erstellen, setzen moderne Grafikprozessoren (GPUs) auf programmierbare Einheiten, die als Shader-Cores bezeichnet werden und über leistungsstarke Gleitkomma-Engines verfügen. Da sich diese Kerne auf die Berechnung konzentrieren und auf viele Funktionen von Allzweckarchitekturen verzichten, sind sie kleiner als CPUs, daher passen mehr von ihnen auf einen Chip. Die Shader-Kerne können auch für andere Aufgaben als Grafik-Berechnungen programmiert werden, wobei ihre Programmiermodell und ihre Software-Entwicklungswerkzeuge schwieriger zu handhaben sind als die einer Standard-CPU.

Um dieses Problem zu umgehen, haben KI-Forscher Werkzeuge zur Entwicklung von DNNs entwickelt. Diese »Frameworks« stellen eine High-Level-Schnittstelle für den Aufbau von Netzwerken dar, mit der der Entwickler die Anzahl der Knoten und Verbindungen festlegt. Einmal spezifiziert, kann das Netzwerk auf jeder Hardware über eine API und einen Satz von Treibern ausgeführt werden. Auf diese Weise müssen DNN-Entwickler die zugrunde liegende Hardware nicht programmieren. Derzeit gehören TensorFlow, Caffe/Caffe2 und Torch/Pytorch zu den beliebtesten DNN-Frameworks.

Nvidia ist der führende Anbieter von GPU-Chips für KI-Anwendungen. Es stellt Treiber für alle gängigen Frameworks sowie andere Tools zur Verfügung, um die Entwicklung und Einarbeitung in DNNs zu erleichtern. Der jüngste High-End-Grafikprozessor des Unternehmens ist das Tesla V100 (Volta) Design mit 320 Shader-Kernen, die insgesamt 14 Billionen FP32-Operationen pro Sekunde verarbeiten können. Der V100 verfügt nur über 6 MB Cache-Speicher; der kleine On-Chip-Speicher kann die Leistung in großen Netzwerken beeinträchtigen, obwohl der Chip einen Speicher mit hoher Bandbreite verwendet, um diesen Mangel teilweise auszugleichen. Die Gesamtleistung für den massiven Chip und seinen High-Bandwidth-Speicher beträgt 250 W TDP.

Jobangebote+ passend zum Thema

Beschleuniger für Rechenzentren

Obwohl GPUs eine effiziente Lösung für DNNs darstellen, insbesondere wenn Gleitkomma-Mathematik benötigt wird, wurden sie ursprünglich für Grafiken und nicht für KI entwickelt. Da die Nachfrage nach KI-Verarbeitung groß ist, entwickeln Unternehmen kundenspezifische Chips, die für die DNN-Beschleunigung optimiert sind. Dieser Ansatz sollte die beste Leistung pro Watt liefern, obwohl das Ergebnis je nach Implementierung unterschiedlich ist.

Da die Entwicklung dieser KI-Beschleuniger noch in den Kinderschuhen steckt, wenden Unternehmen viele verschiedene Architekturen auf dieses Problem an. Einige gemeinsame Merkmale zeichnen sich jedoch ab. Beispielsweise können Produkte, die für die Inferenz vorgesehen sind, auf die Fließkommaunterstützung verzichten und sich auf kleinere Ganzzahlen konzentrieren. Eine ganzzahlige MAC-Einheit verwendet etwa die Hälfte der Siliziumfläche einer vergleichbaren Gleitkommaeinheit; außerdem verwendet ein 8-Bit-MAC ein Viertel der Fläche eines 32-Bit-MAC. So kann der Wechsel von FP32 zu INT8 den Berechnungsbereich bis auf ein Achtel reduzieren. Die kleinere Fläche spart gleichzeitig Energie. Studien haben gezeigt, dass der Unterschied in der DNN-Genauigkeit zwischen FP32 und INT8 für die Inferenz klein ist. Forscher evaluieren andere numerische Formate, um den Kompromiss zwischen Genauigkeit und Werkzeugfläche/Energie zu optimieren.

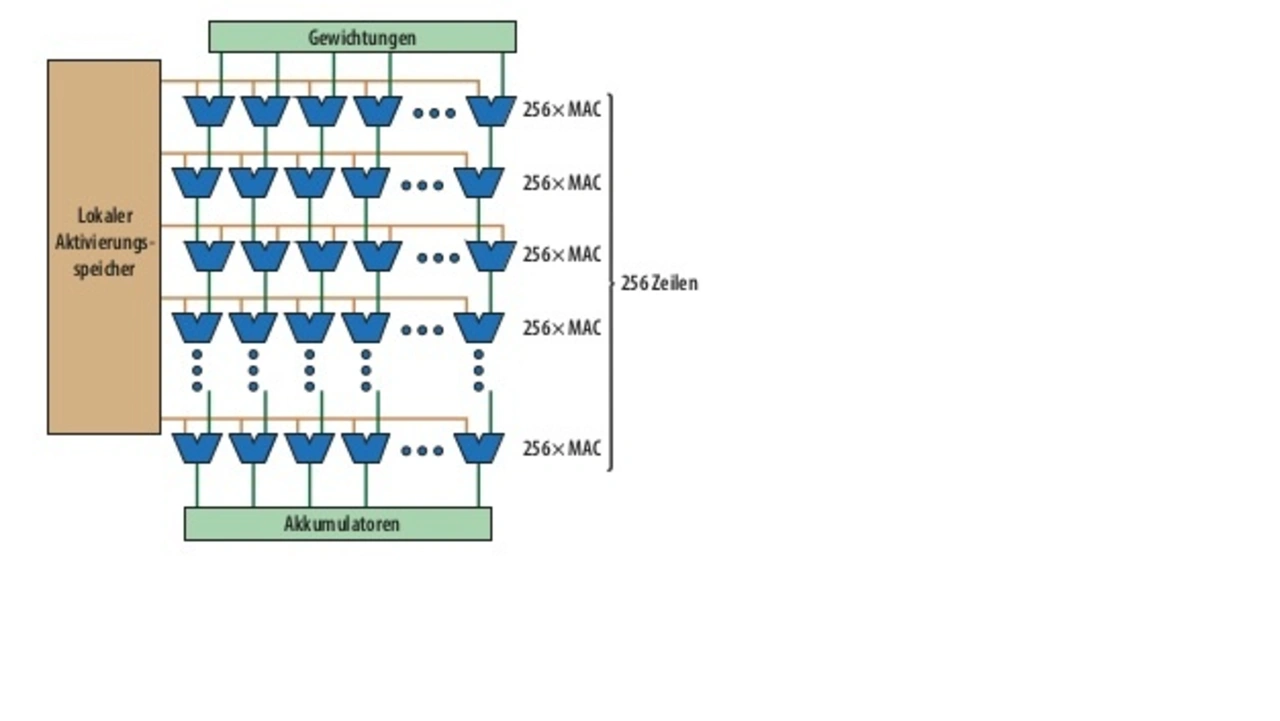

Ein weiteres gemeinsames Merkmal ist das »systolische MAC-Array«. Wie Bild 1 zeigt, kann ein systolisches Array bis zu 256 MACs auf einmal berechnen, dann fließen die Daten sofort zur nächsten Zeile für die nächste Berechnung. Im Gegensatz dazu dekodiert ein CPU- oder GPU-Kern einen Befehl, lädt 512 Bit aus einem Register, berechnet bis zu 16 MACs und speichert die Ergebnisse in einem Register. Die systolische Anordnung eliminiert diese zusätzliche Befehlsdekodierung und den Registerzugriff und vereinfacht das Chip-Design. Schließlich beinhalten KI-Prozessoren oft spezielle Hardware zur Berechnung gängiger DNN-Funktionen wie Aktivierung, Normalisierung und Pooling; diese Funktionen erfordern oft mehrere Anweisungen auf einer Standard-CPU oder GPU.

- Welche Prozessorarchitektur eignet sich am besten?

- Grafikprozessoren

- FPGAs

- Konsumgüter und IoT-Produkte