IEDM 2013

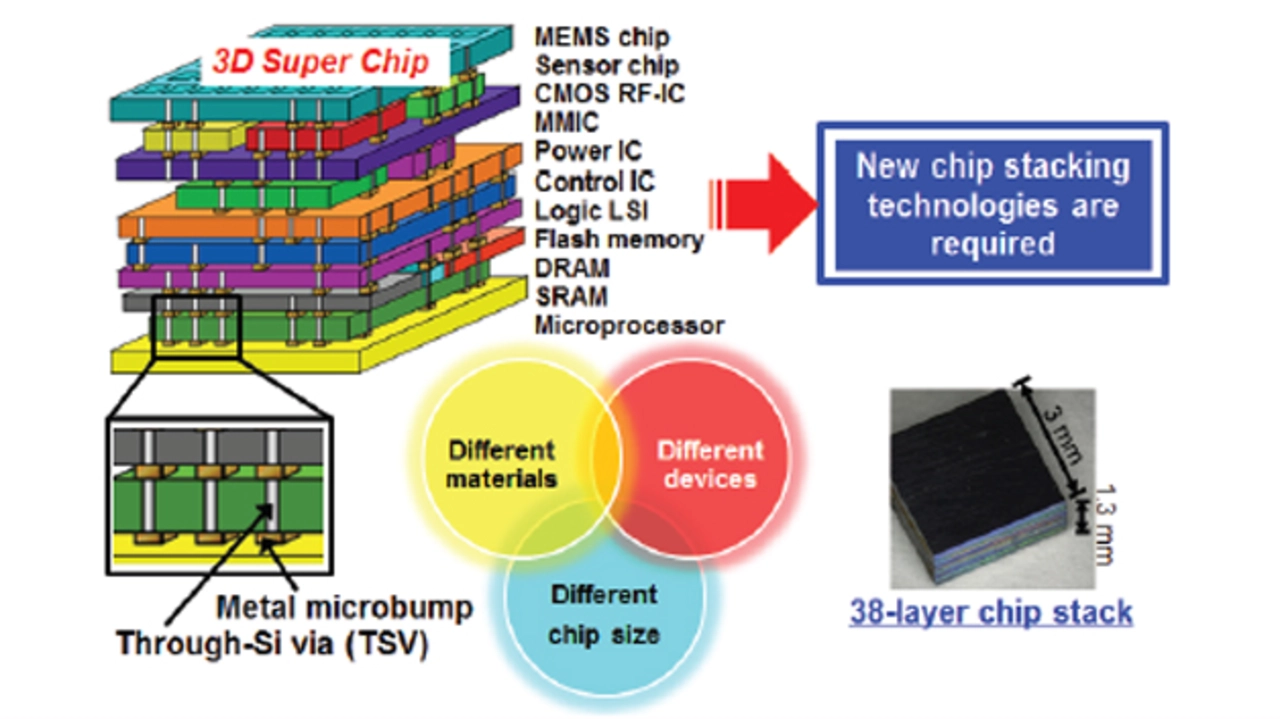

Mit heterogener 3D-Integration zum „Superchip“

Fortsetzung des Artikels von Teil 1

Tauglichkeit für die Massenfertigung essentiell

Ein großes Problem bei der 3D-Integration sieht Koyanagi im Produktionsdurchsatz. Für die Massenfertigung sei Chip-auf-Chip-Stacking (C2C) nicht geeignet. Er schlägt ein neues Verfahren mit Selbstorganisation und elektrostatischem Bonding vor, das einen hohen Durchsatz verspricht. Das Verfahren heißt „reconfigured Wafer-to-Wafer“ (RW2W). Dabei werden zunächst die KGDs von mehreren Wafern sortiert und dann simultan auf sogenannte Träger-Wafer gebondet. Diese rekonfigurierten Wafer enthalten dann nur noch KGDs. Auf einem Ziel-Wafer werden dann die für die jeweilige Chipschicht erforderlichen Chips von den rekonfigurierten Wafern in einem Durchgang aufgebracht. Die einzelnen Chips (KGDs) richten sich dann dank eines Flüssigkeitsverfahrens selbstständig auf dem darunterliegenden Substrat aus. Die Oberflächenspannung der Flüssigkeit wird dazu genutzt, mehrere Chips gleichzeitig pro Schicht auszurichten. Auf dem Substrat werden dabei hydrophile und hydrophobe Gebiete erzeugt. Dieses Verfahren wurde bei der Platzierung von rund fünfhundert erprobt und zeigte eine Ausrichtungsgenauigkeit von 0,5 µm innerhalb von 0,1 s. Durch Anlegen einer hohen Spannung lassen sich die Chips elektrostatisch bonden oder bei umgekehrter Polarität wieder trennen. Die transferierten Chips werden, während sie sich auf einem Supportwafer befinden, von der Rückseite her gedünnt, um dann die TSVs und µ-Bumps zu erzeugen. Anschließend wird der Supportwafer von den gedünnten Chips mit dem Ziel-Interposer-Wafer entfernt und das Stacking lässt sich fortsetzen. Mit diesem Verfahren wurden vier bis acht Chips simultan übertragen und gebondet. In der Zukunft könnten es auch mehr als Tausend Chips sein.

Jobangebote+ passend zum Thema

- Mit heterogener 3D-Integration zum „Superchip“

- Tauglichkeit für die Massenfertigung essentiell