IEDM 2013

Mit heterogener 3D-Integration zum „Superchip“

Die Skalierung von Halbleiterprozessen, auch „More Moore“ genannt, wird immer schwieriger. Einen Ausweg aus dem Dilemma verspricht die heterogene 3D-Integration, eine „More than Moore“-Technologie.

Bei der heterogenen 3D-Integration lassen sich unterschiedliche Arten von Chips verschiedener Größen, Funktionen und Materialien aufeinander stapeln. Neu ist ein Verfahren mit Selbstorganisation und elektrostatischem Bonding, das auch einen hohen Produktionsdurchsatz verspricht.

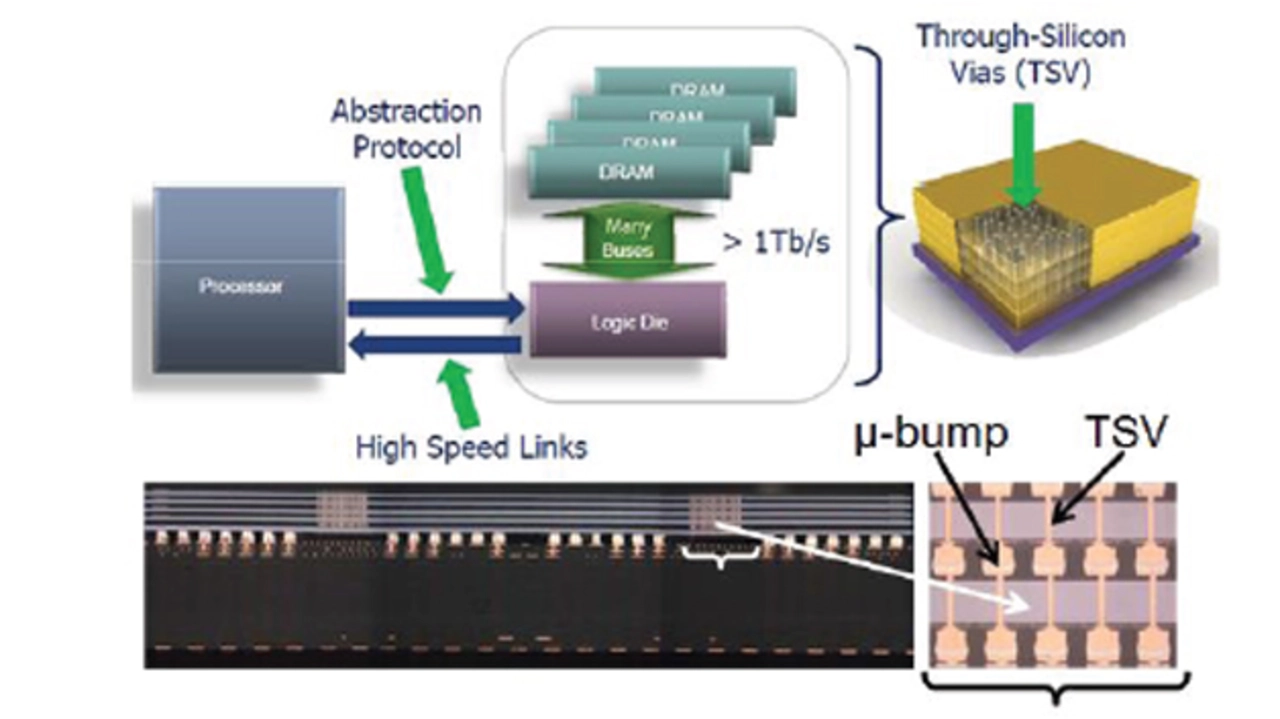

Im asiatischen Part der Plenarvorträge auf der IEDM 2013 in Washington gab Mitsumasa Koyanagi von der Tohoku-Universität in Sendai/Japan einen Überblick über den aktuellen Stand der Technik bei heterogener 3D-Integration und zeigte erstaunliche Applikationsbeispiele, wie einen 3D-DRAM-Chip für Super-Computer mit Datenbandbreiten von 128 und 160 Gbit/s. Dieser hybride Speicherwürfel (HMC -- Hybrid Memory Cube) besteht aus mehreren gestapelten DRAM-Chips, die mit µ-Bumps und TSVs (Through Silicon Vias) miteinander verbunden sind. Teil des Chipstapels ist darüber hinaus ein Controller-Chip, der Fehler erkennen und per Redundanz „reparieren“ kann.

Jobangebote+ passend zum Thema

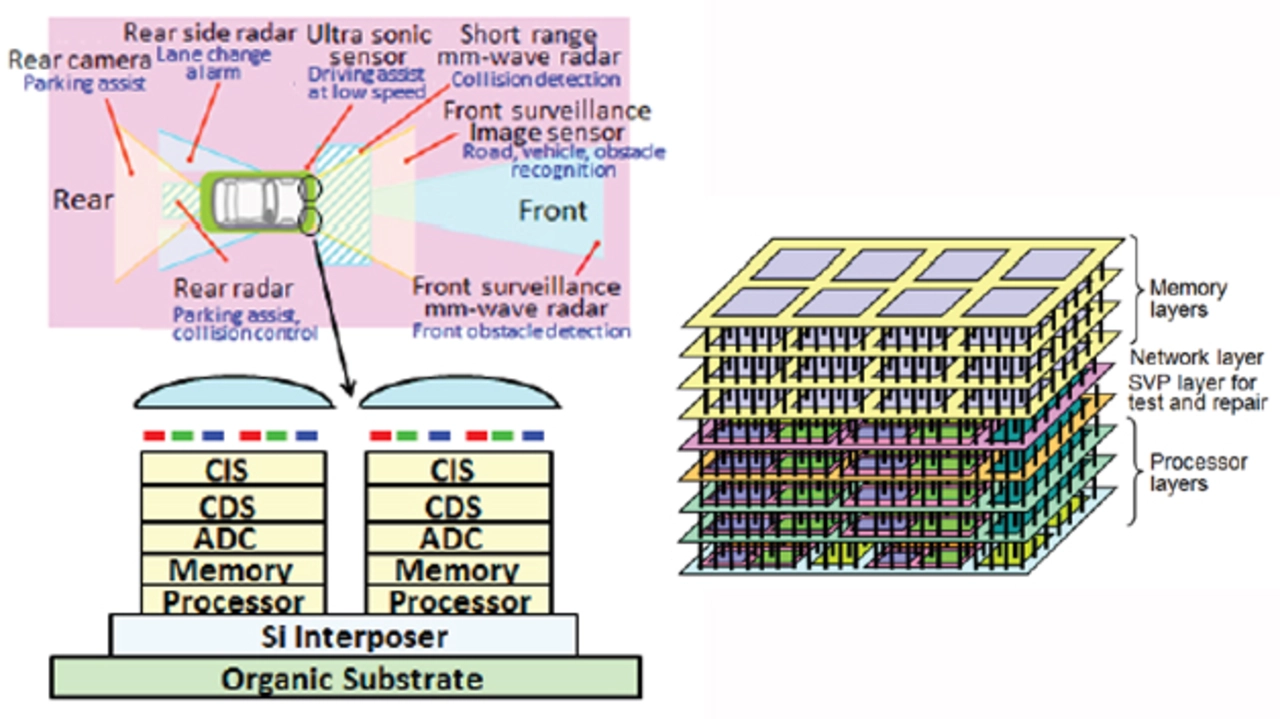

Ein weiteres Beispiel ist ein CMOS-Bildsensor mit integrierter Datenverarbeitung für Fahrerassistenzsysteme im Auto. Dieser 3D-Superchip integriert zwei identische Chipstapel, bestehend aus CMOS-Bildsensor, Analog-Chip, A/D-Umsetzer-Chip, Speicherchip und Prozessor. Beide Stapel sind dann über eine Zwischenschicht (Interposer) auf einem organischen Substrat aufgebracht. Biomedizinische Anwendungen sind ebenfalls ein vielversprechendes Anwendungssegment. Koynagi zeigte eine Retina-Prothese, die Blinden wieder das Sehvermögen zurückgeben soll. Die aus drei gestapelten Chips bestehende künstliche Retina wurde dann zu Versuchszwecken einem Kaninchen eingepflanzt.

In der 3D-Integration spielt der Test eine entscheidende Rolle. Es dürfen nur funktionstüchtige Chips (KGD – Known Good Dies) integriert werden. Das häufige Testen macht 3D-Superchips kompliziert und teuer. Deshalb hält Koyanagi DfT-Prinzipien (Design for Test) für unerlässlich. Alle Stapelchips sollten eingebaute Selbsttest-Schaltungen (BIST) umfassen. Bei den Verbindungen zwischen den Chips sind Boundary-Scan-Verfahren sinnvoll. Ein gutes Beispiel für einen DfT-Superchip ist ein Netzwerk-Switch-Superchip, der aus mehreren Speicher- und Prozessorchips sowie einem Supervisor-Chip besteht. Der Supervisor überwacht die gesamte Funktion des Superchips einschließlich der Testfunktion. Im Fehlerfall ersetzt der Supervisor einen Funktionsblock durch einen redundanten.

- Mit heterogener 3D-Integration zum „Superchip“

- Tauglichkeit für die Massenfertigung essentiell