Mit aktiver Klemmung

Hoher Wirkungsgrad für PFSB-Wandler

Vollbrückenwandler beschaltet man meist mit einem Löschglied, um Schwingungen oder Spannungsspitzen zu dämpfen. Diese bestehen meist aus einem Widerstand und einem Kondensator. Jedoch lässt sich mit einem aktiven Löschglied, das zusätzlich eine Diode enthält, der Wirkungsgrad effektiv steigern.

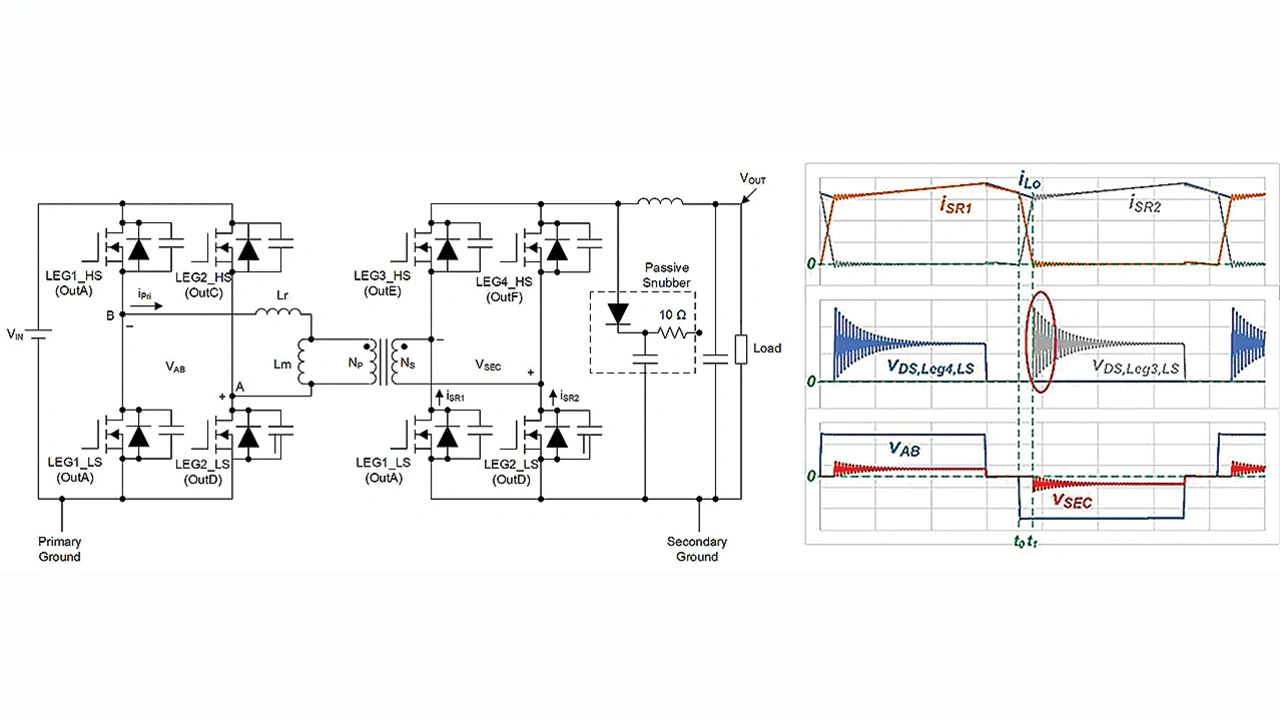

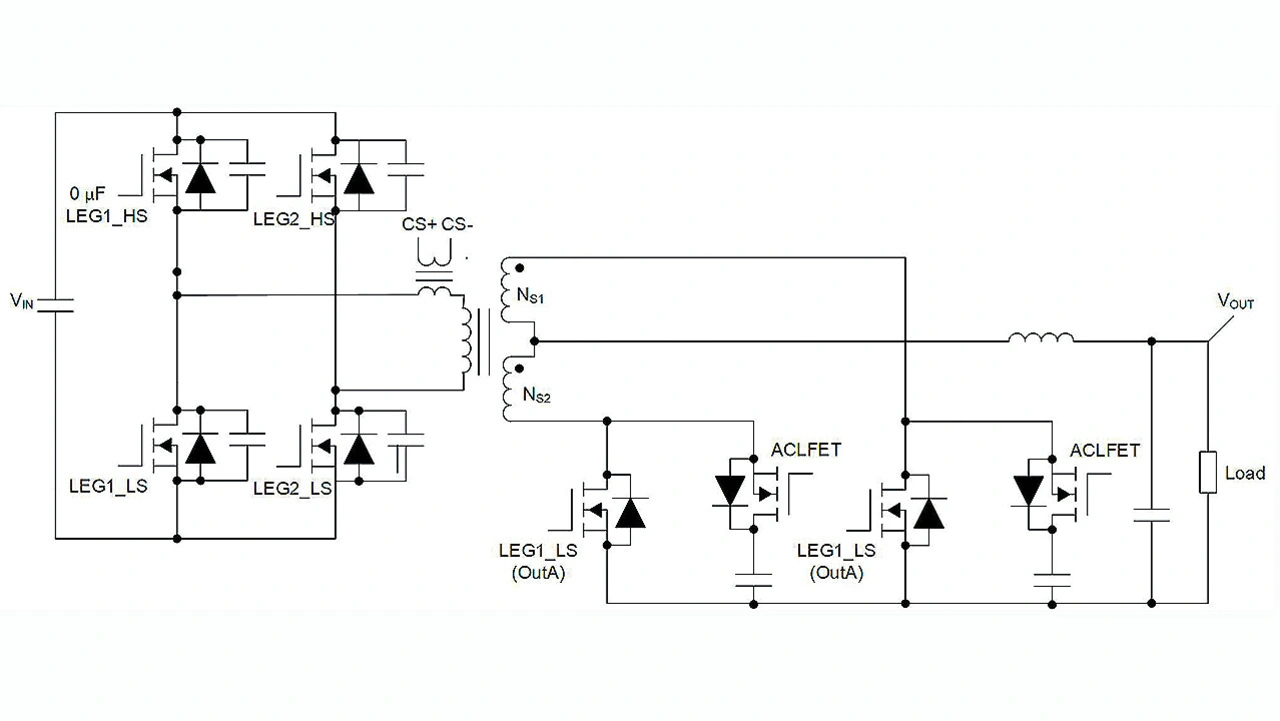

Phasenversetzt arbeitende Vollbrückenwandler (Phase-Shifted Full-Bridge, PSFB) werden in Applikationen mit einem hohen Leistungsbedarf eingesetzt. Denn die eingangsseitigen Schalter können sanft schalten – somit ist ein hoher Wandlerwirkungsgrad erzielbar [1]. Jedoch gerät die parasitäre Kapazität des Ausgangsgleichrichters in Resonanz mit den Streuinduktivitäten des Übertragers (in Bild 1 mit Lr bezeichnet). Hierbei kommt es zu starken Spannungs-Oszillationen mitsamt den daraus resultierenden Belastungen [2].

Tatsächlich kann sich am Ausgangsgleichrichter eine Spannung von 2 x VIN x NS/NP aufbauen, wobei NP und NS die Windungszahl der Primär- beziehungsweise Sekundärwicklung angeben. Traditionell leistet man Abhilfe, indem man den Ausgangsgleichrichter mit einer passiven Snubber-Schaltung [2] – auch als RC-Löschglied bezeichnet – versieht.

Jobangebote+ passend zum Thema

In Bild 1 ist beispielsweise ein RCD-Snubber bestehend aus Widerstand, Kondensator und Diode zu sehen, der ein zu starkes Ausschlagen der Spannung am Gleichrichter verhindert und somit das Verwenden eines Bauteils mit geringerer Nennspannung und einer besseren Figure of Merit (Gütezahl) erlaubt, was wiederum die Verlustleistung senkt.

Kommen MOSFETs als Synchrongleichrichter zum Einsatz, kann man davon ausgehen, dass sie mit geringerer Nennspannung bei gleichem Kostenniveau niedrigere COSS- und RDS(on)-Werte aufweisen als MOSFETs, die für höhere Spannungen ausgelegt sind. Passive Snubber-Schaltungen haben allerdings den Nachteil, dass sie einen Teil der Energie, die die Spannungsausschläge verursacht hat, dissipieren und deshalb zulasten des Wirkungsgrads gehen.

Der Artikel beschreibt als Alternative eine aktive Snubber-Schaltung mit der zugehörigen Ansteuerung. Die Schaltungskombination minimiert die Spannungsbelastung für den Gleichrichter, um einen hohen Wandlerwirkungsgrad zu erreichen, verringert jedoch gleichzeitig die in der Snubber-Schaltung dissipierte Energie, ohne Abstriche am Betriebsbereich machen zu müssen.

PFSB-Wandler mit aktiver Klemmung

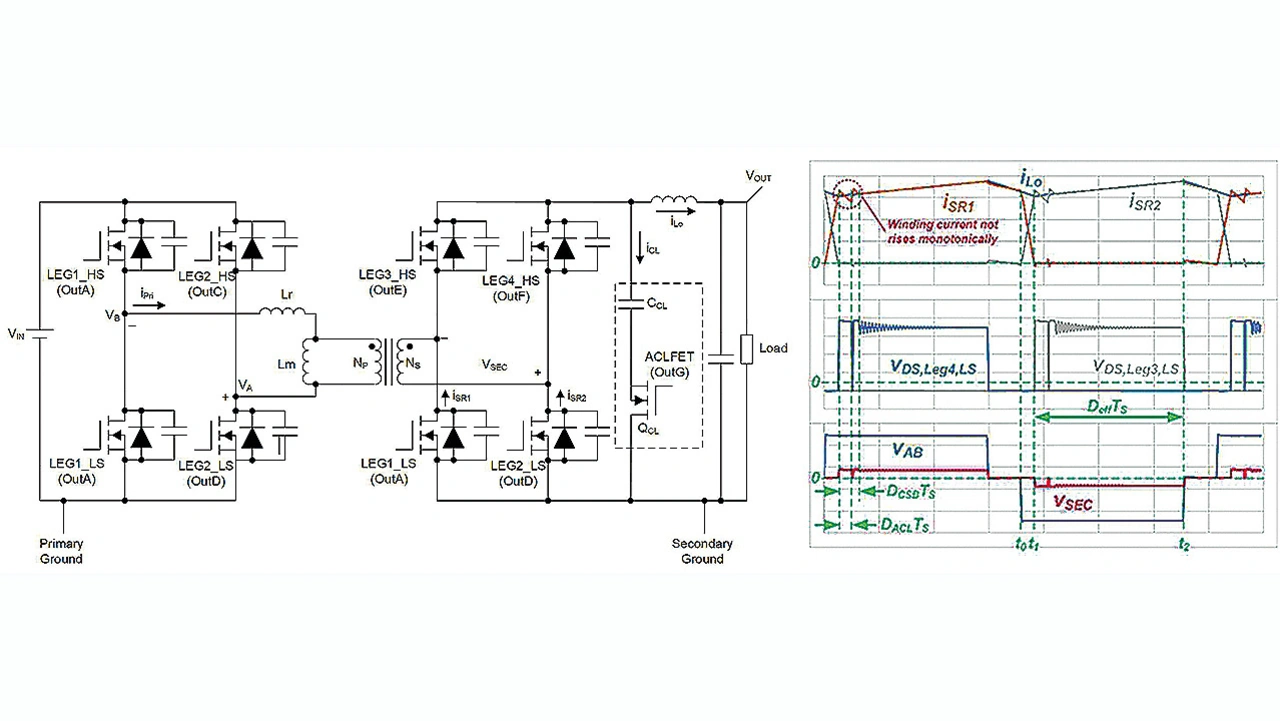

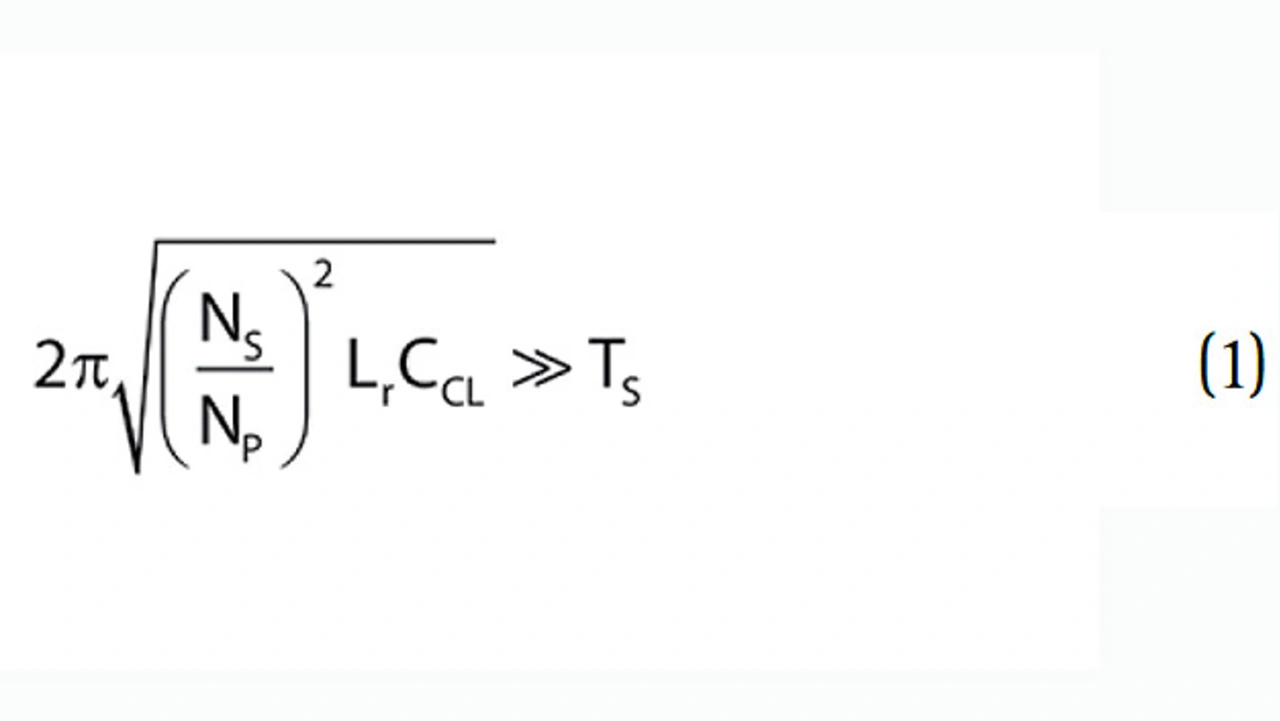

In Bild 2 ist zu sehen, wie ein aktiver Klemmzweig bestehend aus dem Kondensator CCL und dem MOSFET QCL vor der Ausgangsinduktivität eingefügt wurde. Dieser Zweig leitet während der Einschaltzeit (Deff) einen Strom und klemmt damit die Spannung VSEC an der Sekundärwicklung und damit die Spannungsbelastung des Gleichrichters auf die an CCL liegende Spannung VCL. Um die Spannung am Ausgangsgleichrichter niedrig zu halten, ist der Kapazitätswert von CCL so hoch zu wählen, dass die Spannungswelligkeit an diesem Kondensator gering bleibt. Als Faustregel sollte die Resonanzperiode des durch Lr und CCL gebildeten Schwingkreises deutlich größer sein als die Schaltperiode TS [3]. Siehe hierzu Gleichung 1:

Die Spannungsbelastung des Gleichrichters wird mit der aktiven Snubber-Schaltung auf etwa VIN x NS/NP begrenzt, also auf etwa die Hälfte der Spannungsbelastung, die sich ohne Klemmung ergibt.

| Legende |

|---|

| VIN = Wert der Eingangsspannung |

| NS = Windungszahl der Sekundärwicklung |

| NP = Windungszahl der Primärwicklung |

| COSS = Wert der Ausgangskapazität |

| RDS(on) = Wert des Einschaltwiderstands |

| CCL = Kondensator Snubber-Schaltung |

| QCL = MOSFET Snubber-Schaltung |

| Deff = Einschaltzeit des Tastzyklus |

| VSEC = Spannung an der Sekundärwicklung |

| VCL = Spannung an Kondensator CCL |

| Lr = Streuinduktivität des Übertragers |

| TS = Schaltperiode |

| DeffTS = Einschaltzeit des Tastzyklus |

| DCSBTS = Zeitspanne, in der das Strom-Zeit-Gleichgewicht erreicht wird |

| Lm = Induktivität der Primärwicklung |

| iSR1 = Stromfluss durch Wandler 1 |

| iSR2 = Stromfluss durch Wandler 2 |

| VLr = Spannung an Lr |

| Δt = Gesamtzeit, in der der aktive Klemmzweig leitend ist |

| ΔiCL = Gesamtdifferenz des Stromflusses durch CCL |

| iSEC = Strom auf Sekundärseite des Wandlers |

| iLo = Strom durch Spule Lo |

| iSR = Strom durch Wandler 2 |

| t3 = Beginn des Aufladens von CCL |

| iCL,peak = Spitzenstrom durch Kondensator CCL |

Anders als bei einer passiven Snubber-Schaltung dissipiert die Energie bei der aktiven Schaltungskombination nicht in einem Widerstand, sondern wird lediglich im LC-Resonanzkreis gespeichert. Ist die Spannung an der Ausgangswicklung nicht mehr null, wird Energie von der Primär- an die Sekundärwicklung übertragen, womit Energie in die Ausgangsinduktivität gelangt und ein Strom durch die Body-Diode von QCL fließt, selbst wenn der MOSFET gar nicht eingeschaltet ist. Indem QCL erst dann eingeschaltet wird, wenn bereits ein Strom durch seine Body-Diode fließt, wird gewährleistet, dass QCL im Spannungsnulldurchgang schaltet. Aus diesem Grund kann man davon ausgehen, dass ein PFSB-Wandler mit aktiver Snubber-Schaltung einen höheren Wirkungsgrad erreicht als ein solcher mit passiver Schaltung – identische Spezifikationen vorausgesetzt.

Design des aktiven Klemmzweigs

Versieht man einen PFSB-Wandler mit einer aktiven Snubber-Schaltung, so hat der Strom in der Übertragerwicklung während der Einschaltzeit des Tastzyklus (Deff), also jenem Abschnitt, in dem die Spannung an der Ausgangswicklung von null verschieden ist (TS), keinen monoton steigenden Verlauf. Das liegt daran, dass der Kondensator der aktiven Snubber-Schaltung ebenfalls Energie in die Ausgangsinduktivität überträgt, sodass die Energie nicht ausschließlich aus dem Eingang entnommen wird. Der nichtmonotone Stromverlauf könnte jedoch schwierige Voraussetzungen für eine Spitzenstromregelung ergeben, die meist den Eingangsstrom oder den Strom in der Übertragerwicklung erfasst. Ein höherer Eingangs- oder Übertragerstrom bedeutet hier nicht zwangsläufig, dass das Tastverhältnis ebenfalls größer ist.

Um das Erfassen des Spitzenstroms während der monoton steigenden Phase des Stroms zu ermöglichen, ist zu gewährleisten, dass DeffTS stets größer ist als die Zeitspanne, in der das Strom-Zeit-Gleichgewicht erreicht wird (DCSBTS) – und das über den gesamten Versorgungsspannungs- und Laststrombereich hinweg. Weil von PFSB-Wandlern mit größerem Deff ein höherer Wirkungsgrad zu erwarten ist, sind sie meist so ausgelegt, dass sie im Bereich mittlerer bis hoher Lasten, in dem Deff deutlich größer als DCSB sein dürfte, einen höheren Deff-Wert aufweisen. Bei geringer Last dürfte der Wandler wahrscheinlich in den lückenden Betrieb übergehen, in dem Deff bei gleicher Eingangs- und Ausgangsspannung kleiner ist als im nichtlückenden Betrieb. Damit DeffTS auch bei geringer Last stets größer als DCSBTS bleibt, wurde im vorliegenden Fall eine laststrombasierte Frequenzabsenkung implementiert.

Die Dauer von DCSBTS wird zu einem wichtigen Faktor für die Spitzenstromregelung. Die entscheidende Frage lautet jetzt, wie lange es dauert, bis das Strom-Zeit-Gleichgewicht erreicht ist. Beantworten lässt sich die Frage, indem man den Stromfluss im aktiven Klemmzweig berechnet.

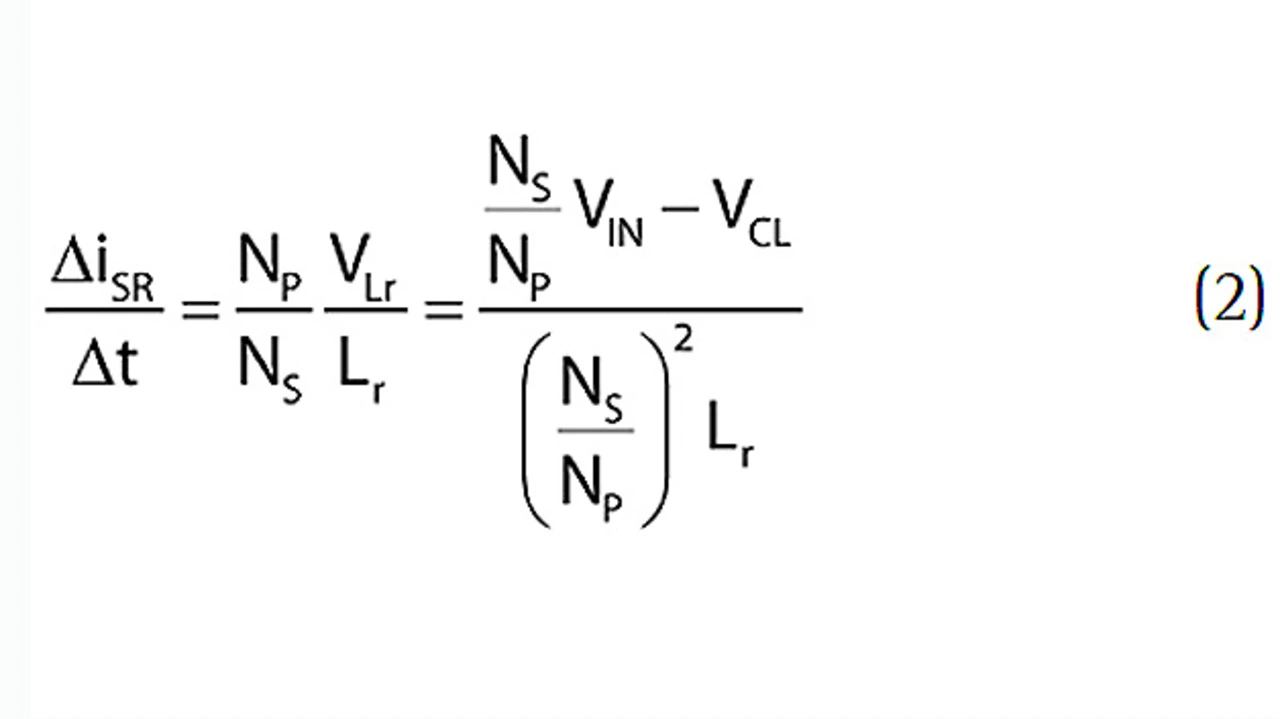

Unter der Annahme, dass VCL konstant und Lm unendlich ist, drückt Gleichung 2 die Änderungsrate des Gleichrichterstroms während der Ausschaltzeit des Tastzyklus aus, jener Zeitspanne also, in der VSEC = 0 ist und iSR1 und iSR2 kommutieren:

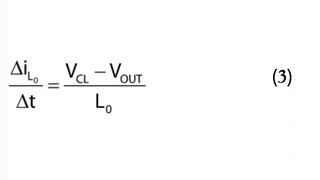

Mit Gleichung 3 (sh. Formel) lässt sich die Änderungsrate des Stroms in der Ausgangsinduktivität berechnen

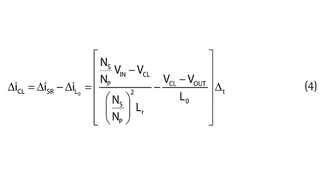

Unter Heranziehen der Gleichungen 2 und 3 sowie der Kirchhoffschen Knotenregel ist es mithilfe von Gleichung 4 (sh. Formel) möglich, die Änderungsrate des Stroms in der aktiven Klemmschaltung zu berechnen

Design des aktiven Klemmzweigs, Formeln 3-7

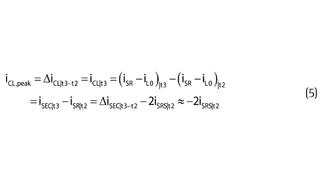

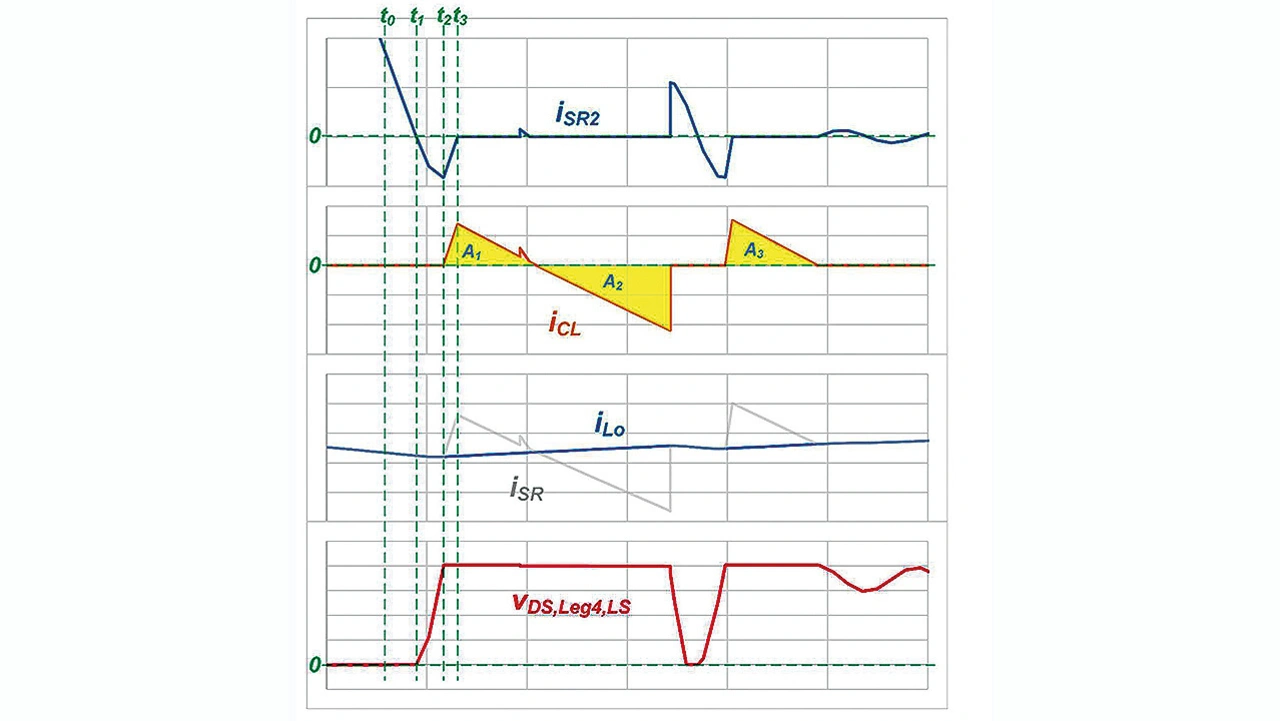

Da VCL ≈ VIN x NS/NP ist [3], ist lediglich die Gesamtzeit, in der der aktive Klemmzweig leitend ist, als Δt in Gleichung 4 einzusetzen, um ΔiCL zu erhalten. Allerdings muss man den Scheitelwert von iCL kennen, um den Effektivwert (Root Mean Square, RMS) von iCL zu berechnen. Wie man aus Bild 3 ersehen kann, lässt sich, wenn iSEC = iLo (nach Aufladen von Coss auf VCL) zum Zeitpunkt t2 und iSEC = iSR zum Zeitpunkt t3 (Beginn des Aufladens von CCL) ist, mit Gleichung 5 (sh. Formel) der Wert von iCL,peak wie folgt errechnen (Bild 3):

Gleichung 6 ergibt den Wert von iSR2 zum Zeitpunkt t2 (sh. Formel)

Geht man davon aus, dass die Abfallrate des Stroms iSR2 von t0 bis t2 gleich ist, kann mit Gleichung 7 (sh. Formel) die Zeitspanne zwischen t2 und t1 berechnet werden.

Da CCL ein Strom-Zeit-Gleichgewicht bewahren muss, ist die Summe der Flächen A1 und A3 gleich der Fläche A2.

Wie an Gleichung 7 deutlich wird, bestimmt der COSS-Wert des Synchrongleichrichters den Scheitelstrom im aktiven Klemmzweig. Wählt man also einen Synchrongleichrichter-MOSFET mit niedrigem COSS-Wert, ist der Effektivstrom im aktiven Klemmzweig geringer, was zu einem verbesserten Wandlerwirkungsgrad beiträgt.

Es folgen einige Richtlinien zum Design von PFSB-Wandlern mit aktiver Snubber-Schaltung:

➔ QCL darf erst nach dem Ende der Ausschaltphase des Tastzyklus einschalten, um den Rückfluss von Energie aus CCL an die Primärseite zu verhindern.

➔ Damit im Spannungsnulldurchgang geschaltet wird, muss QCL einschalten, während die Body-Diode noch leitend ist.

➔ Je länger QCL eingeschaltet ist, umso geringer wird VCL und die Spannungsbelastung des Synchrongleichrichters, während der Effektivstrom durch QCL zunimmt.

➔ Je geringer der COSS-Wert des Synchrongleichrichters ist, umso niedriger ist der Effektivstrom in der aktiven Klemmschaltung und umso mehr reduziert sich die Spannungsbelastung des Synchrongleichrichters.

Die aktive Klemmung eignet sich nicht nur für Vollbrücken-Gleichrichter, sondern ebenfalls für andere Gleichrichter-Bauarten wie etwa Stromverdoppler [4] oder Gleichrichter mit Mittelanzapfung.

In Bild 4 ist ein PFSB-Wandler mit aktiver Klemmung an einem Gleichrichter mit Mittelanzapfung zu sehen, wie er in einem Referenzdesign von Texas Instruments implementiert ist.

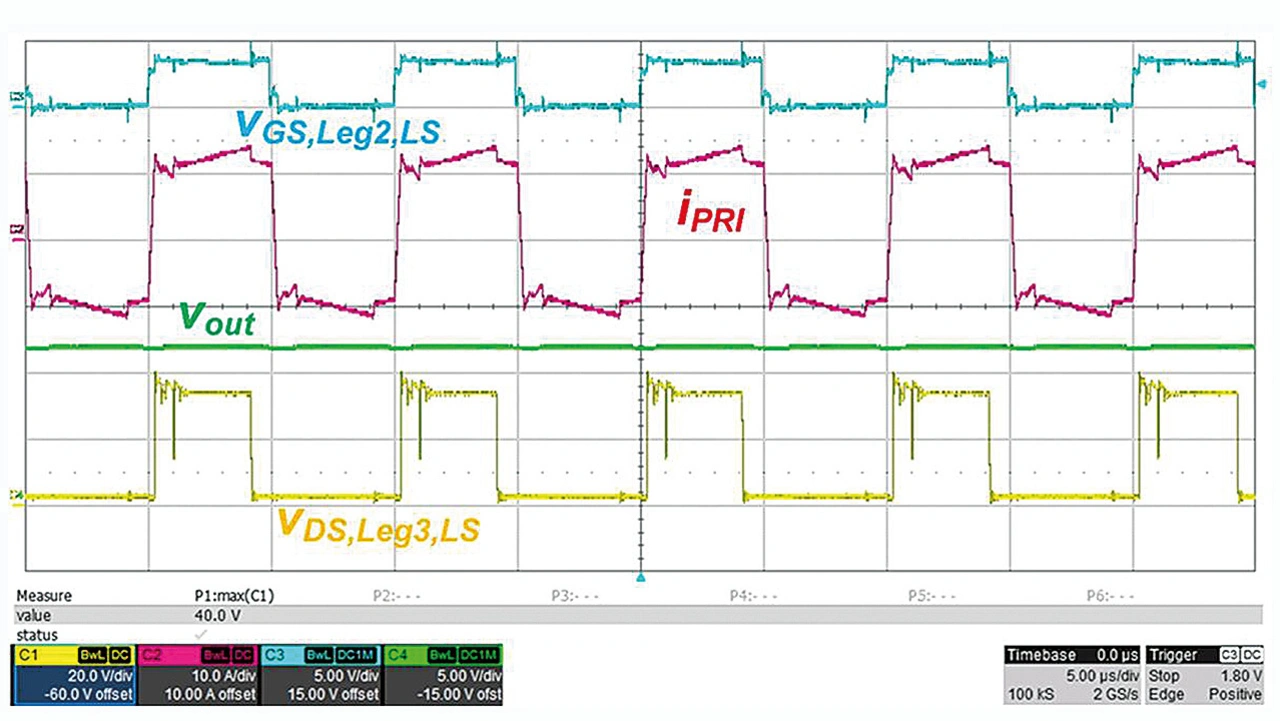

Wie in Bild 5 zu erkennen ist, lässt sich die Spannungsbelastung des Synchrongleichrichters mit zwei aktiven Klemmschaltungen auf unter 40 V begrenzen, wobei die Klemmverluste – in Form sehr geringfügiger Leitungsverluste – bei 250 A Laststrom vernachlässigbar gering sind.

Effizienter PFSB-Wandler

Thema dieses Artikels ist das Verwenden aktiver Snubber-Schaltungen in PFSB-Wandlern. Mit einer aktiven Snubber-Schaltung verringert sich die Spannungsbelastung des Ausgangsgleichrichters und sie erzeugt selbst lediglich eine vernachlässigbar geringe Verlustleistung, sodass sich der Wandlerwirkungsgrad entsprechend erhöht. Jedoch bringt der Einfluss der aktiven Snubber-Schaltung auf den Strom erschwerte Voraussetzungen für die Spitzenstromregelung mit sich.

Hält man die Einschaltzeit des Leistungsschalters der aktiven Snubber-Schaltung jedoch konstant und implementiert eine Frequenzabsenkung, lässt sich ein sehr effizienter PFSB-Wandler mit Spitzenstromregelung realisieren. Auf Basis der vorgeschlagenen Regelungsmethode wurde der Prototyp eines PFSB-Wandlers mit 400 V Eingangsspannung, 12 V Ausgangsspannung und einer Ausgangsleistung von 3 kW gebaut und über den gesamten Lastbereich getestet. Hierbei ergab sich, dass die Spannungsbelastung des Ausgangsgleichrichters selbst beim vollen Laststrom von 250 A unter 40 V bleibt.

Literatur

[1] Designing a Phase Shifted Zero Voltage Transition (ZVT) Power Converter. Unitrode Power Supply Design Seminar SEM 900. 1993.

[2] Lin, Song-Yi, and Chern-Lin Chen. April 1998. »Analysis and Design for RCD Clamped Snubber Used in Output Rectifier of Phase-Shift Full-Bridge ZVS Converters«. Veröffentlicht in IEEE Transactions on Industrial Electronics 45 (2), pp. 358-359.

[3] Sabate, J.A., V. Vlatkovic, R.B. Ridley, and F.C. Lee. 1991. »High-Voltage, High-Power, ZVS, Full-Bridge PWM Converter Employing an Active Snubber«. Sixth Annual Applied Power Electronics Conference and Exhibition, pp. 158-163.

[4] Texas Instruments. Design Review: 100W, 400kHz, DC/DC Converter With Current Doubler Synchronous Rectification Achieves 92% Efficiency. 2023.