Superjunction-MOSFETs für hart und resonant schaltende Applikationen

Die Alternative zu GaN

Fortsetzung des Artikels von Teil 1

Zwei Topologien, ein MOSFET

Mit der MOSFET-Familie CoolMOS C7 mit 600 V Sperrspannung adressiert Infineon die Anforderungen hinsichtlich Leistungsfähigkeit, Wirkungsgrad und Leistungsdichte sowohl von hart als auch resonant schaltenden Topologien. Die Familie konnte zudem beim spezifischen Flächenwiderstand die Grenze von 1 Ω/mm² durchbrechen.

In einem TO-247-Gehäuse heißt das beispielsweise, dass der größte Chip mit einem maximalen RDS(on) von 17 mΩ eine rund zehnprozentige Verbesserung gegenüber der vorherigen Generation (SJ-Bausteine CoolMOS C7 mit 650 V) darstellt. In einem TO-220/D2PAK-Gehäuse hat der größte Chip einen maximalen RDS(on) von 40 mΩ.

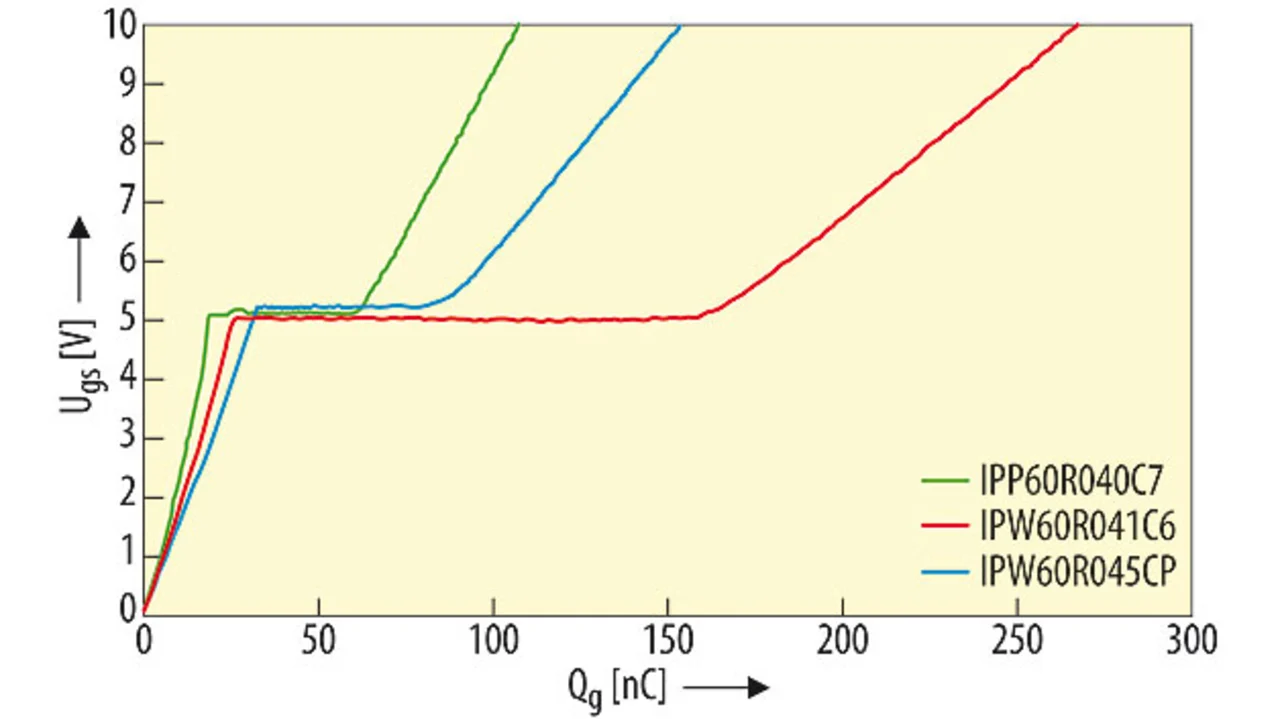

Gleichzeitig reduzieren sich mit der C7-Halbleiterstruktur im Vergleich zu früheren SJ-Technologien die Schaltverluste aufgrund einer niedrigeren Gate-Ladung Qg von rund 107 nC bei 40 mΩ und einer geringeren Gate-Drain-Ladung Qgd. Die geringere Gate-Ladung und die niedrigere Gate-Drain-Ladung haben geringere Treiber-Verluste zur Folge, wobei die niedrigere Gate-Drain-Ladung auch noch einen positiven Einfluss auf die Schaltzeiten und die Schaltverluste hat (Bild 1).

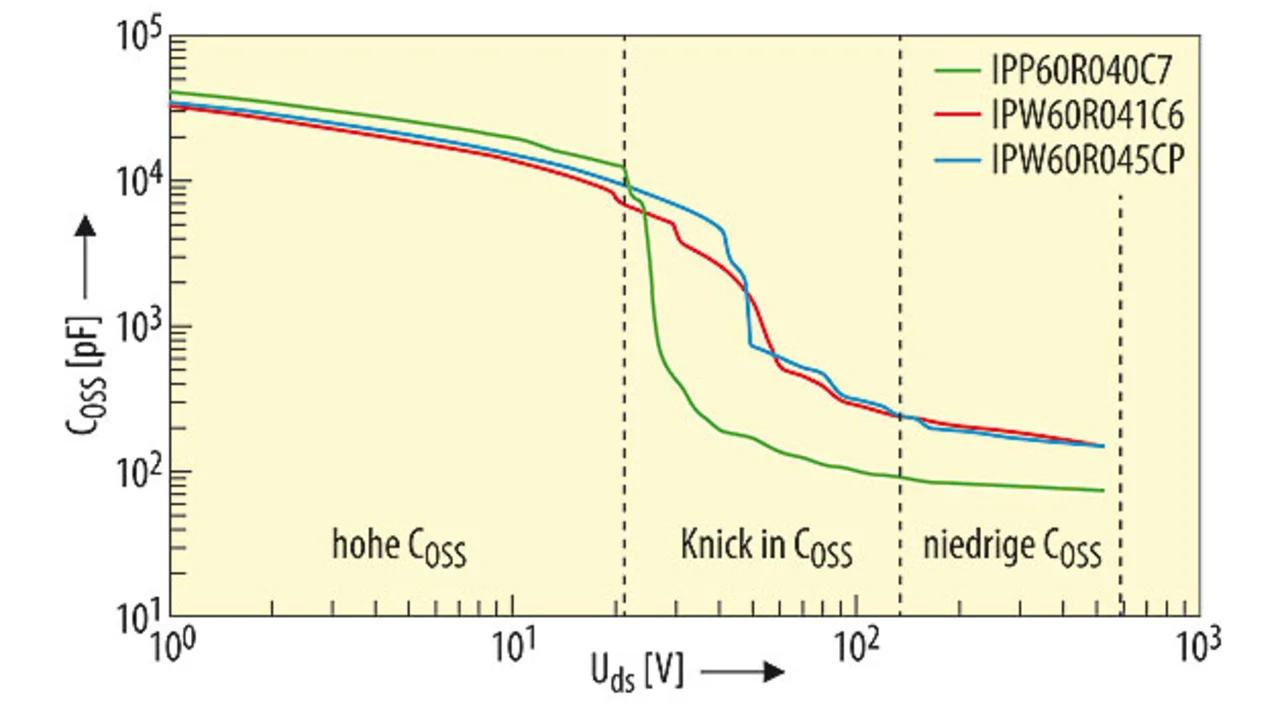

Auf die C7-Struktur sind auch die Verbesserungen hinsichtlich der Ausgangskapazität COSS zurückzuführen. In Bild 2 ist ein Vergleich der Ausgangskapazitäten von CoolMOS C7 und der vorherigen CoolMOS-Generationen C6 und CP dargestellt.

Jobangebote+ passend zum Thema

Die C7-Generation weist bei niedrigeren Spannungen höhere COSS-Werte auf. Steigt die Spannung an, sinken die Werte deutlich schneller. Dies führt bei höheren Spannungen zu niedrigeren Werten. Durch die höhere Kapazität bei niedrigerer Spannung benötigt die C7-Generation eine geringere Ausschaltenergie Eoff. Die geringere Kapazität bei hoher Spannung bedingt einen schnelleren dv/dt-Übergang. Im Vergleich zu vorherigen Generationen sinkt damit EOSS bei typischen DC-Verbindungsspannungen durch die Kombination des COSS-Abfalls bei geringeren Spannungen und der niedrigeren COSS-Werte bei höheren Spannungen (COSS dominiert EOSS, was wiederum den Gesamtwert der gespeicherten Energie in der Ausgangskapazität darstellt).

In hart schaltenden Anwendungen stellt diese Energie einen festen Anteil der Schaltverluste dar, der bei leichten Lasten einen signifikanten Anteil hat. Die meisten Verluste sind lastabhängig und steigen deutlich, wenn die Last größer wird. Die Verringerung von EOSS kann in hart schaltenden Designs eine Verbesserung hinsichtlich des Wirkungsgrads bei niedrigen Lasten darstellen; dieses Ergebnis ist vergleichbar mit dem, was in Zukunft mit den Galliumnitrid-Technologien möglich ist.

- Die Alternative zu GaN

- Zwei Topologien, ein MOSFET

- Vorteile bei PFC- und LLC-Designs