Halbleiter-Entwicklung aus TSMC-Sicht

»Goldenes Zeitalter für die Halbleiterindustrie«

Fortsetzung des Artikels von Teil 1

Technologieplattform für HPC/KI

Neben den bereits beschriebenen Prozessinnovationen gibt es laut Zhang auch bereichsspezifische Prozessoptimierungen, die speziell dabei helfen, HPC-Rechenplattformen zu verbessern. Bei CPUs sind beispielsweise OverDrive oder die Erhöhung von VDD wirksame Techniken, um die Leistung zu steigern. Eine Frequenzverbesserung im einstelligen Prozentbereich allerdings führt dazu, dass die Leistungsaufnahme deutlich steigt. Also hat TSMC mit dem N4X-Prozess seinen ersten 5-nm-Prozess entwickelt, der speziell für HPC-Anwendungen optimiert wurde. Er erlaubt im Vergleich zu einem N5-Prozess eine um 15 Prozent höhere Geschwindigkeit; im Vergleich zum noch schnelleren N4P ist bei 1,2 V auch noch ein Plus von 4 Prozent möglich. Mit N4X können Treiberspannungen von über 1,2 V erreicht werden, was eine zusätzliche Performance-Steigerung erlaubt.

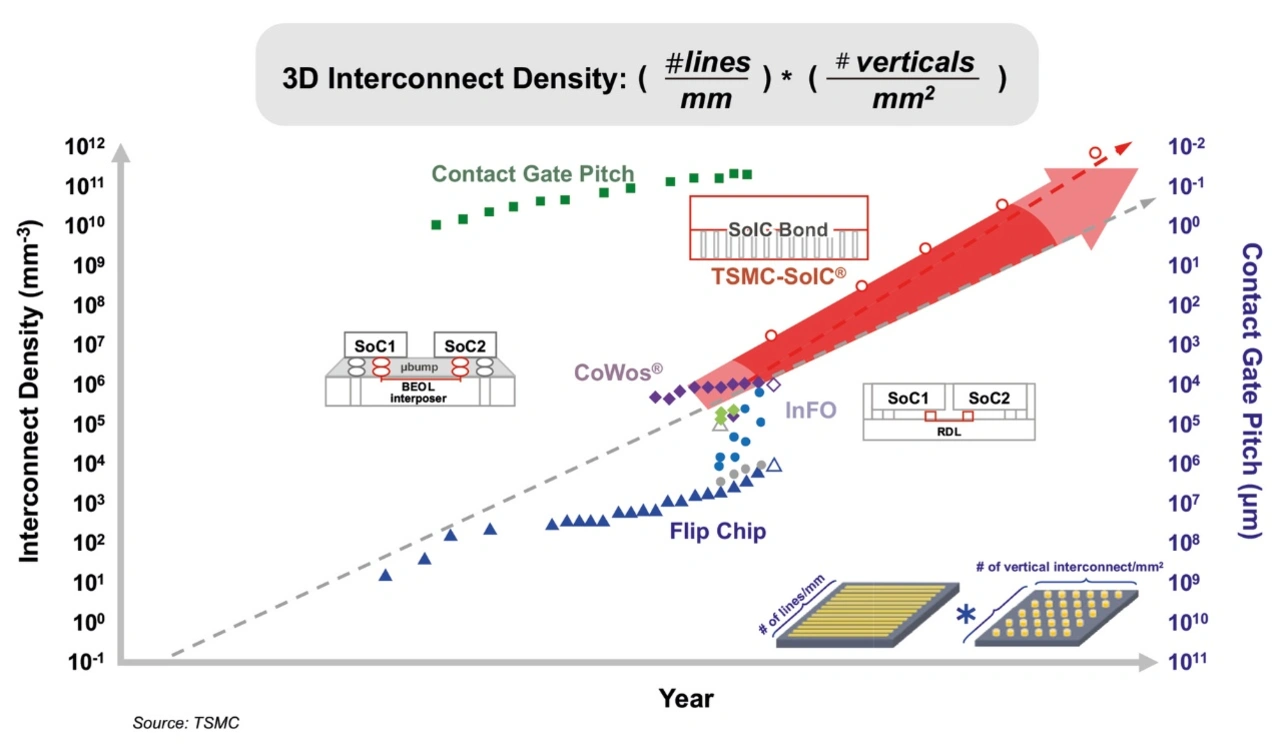

Laut Zhang nutzen die heutigen HPC/KI-Plattformen – sei es GPU, NPU oder ASIC – typischerweise eine Interposer-Technologie, um das SoC mit dem HBM zu kombinieren.

Jobangebote+ passend zum Thema

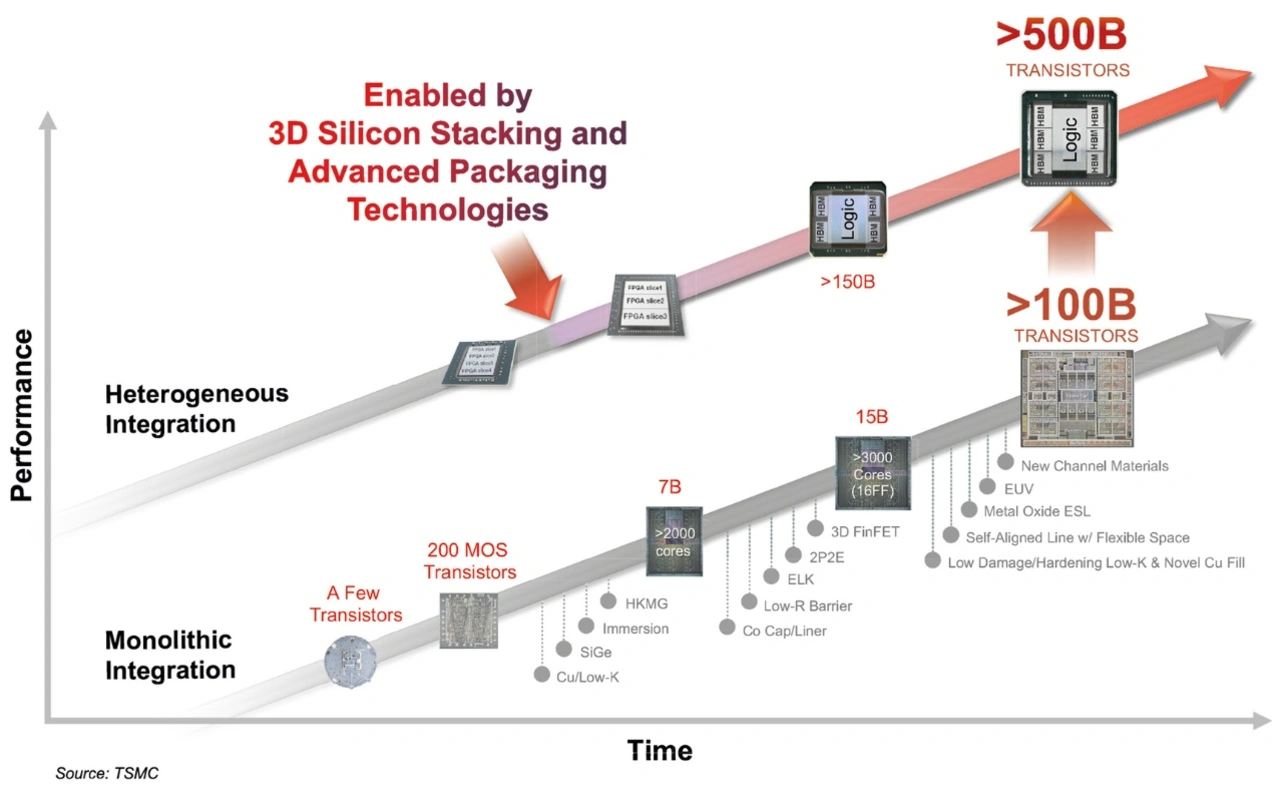

Neben der Prozesstechnologie spielt bei HPC/KI-Plattformen die Gehäusetechnik mittlerweile eine entscheidende Rolle. TSMC hat im Laufe der Jahre verschiedene Ansätze für das Packaging und die Integration auf Chipebene entwickelt, darunter CoWoS (Chip-on-Wafer-on-Substrate, 2,5-D-Technologie), InFO (Integrated Fan-out, 2,5D-Technologie) und mit SoIC (System on Integrated Chips, 3D-Technologie mit Chip on Wafer und Wafer on Wafer) die jüngste Variante. Mit diesen Verfahren können laut Zhang über 500 Mrd. Transistoren in ein gehäustes System integriert werden. So hat TSMC beispielsweise eine Kombination von 3D-SoIC und CoWoS für die Fertigung des KI-Beschleunigers »MI300X« von AMD genutzt, der 153 Mrd. Transistoren aufweist. Zhang ist aber überzeugt, dass diese Ansätze für zukünftige Hochleistungs-Plattformen für HPC/KI nicht ausreichen. Er ist vielmehr überzeugt, dass die Technologien dahingehend weitergetrieben werden müssen, dass Halbleiter realisiert werden, die eine deutlich höhere Komplexität aufweisen und gleichzeitig auch energieeffizienter sind.

Ein Weg, um die Rechenleistung zu erhöhen, besteht seiner Meinung nach darin, dass die Rechen-SoCs mithilfe der SoIC-Technik aufeinandergestapelt werden, um so die benötigte Compute-Dichte zu erhöhen. Gleichzeitig ist auch eine höhere Speicher-Bandbreite notwendig, also muss mehr HBM (High-Bandwidth-Memory) ins Gehäuse gesetzt werden; folglich müsse auch der Interposer (CoWos) vergrößert werden. »Das reicht aber immer noch nicht aus, denn auch die Stromversorgung stellt ein Problem dar. Also müssen Spannungsregler integriert werden, um das Stromversorgungsproblem in den Griff zu bekommen.

Denn eine effiziente Stromversorgung ist ein weiterer, entscheidender Faktor, um Hochleistungsanwendungen zu ermöglichen.« Auch hierfür wurden bereits Technologien entwickelt, die eine effiziente Stromverteilung auf dem Die und im Gehäuse ermöglichen. So kann beispielsweise ein SHDMiM-Kondensator (Super-High-Density-Metal-Isolator-Metal) auf dem Die integriert oder in den CoWoS-Interposer eingebettet werden, um die Leistungsübertragung innerhalb des Gehäuses zu verbessern. Andere Technologien wie eingebettete Deep-Trench-Kondensatoren (eDTC) in größeren CoWoS-Modulen (2500 mm2 Interposer-Größe), Kondensatoren über aktiven Logikschichten und integrierte Spannungsregler verbessern ebenfalls die Stromversorgung.

Zu guter Letzt muss seiner Aussage nach auch die Verbindung nach außen verbessert werden; auch hier ist eine deutlich höhere Bandbreite erforderlich, also seien Hochgeschwindigkeits-SerDes-Designs für die effiziente Übertragung großer Datenmengen unerlässlich. Die Hochgeschwindigkeitssignalisierung für Rechenzentrumsanwendungen erfordert eine Datenrate von mehr als 224 Gbit/s. Das Erreichen von Hochgeschwindigkeitsverbindungen mit dieser Rate stellt jedoch zwei primäre Herausforderungen dar: Leistungseffizienz und Signalintegrität, insbesondere bei einer Einfügedämpfung von bis zu 35 bis 40 dB. Um eine Leistungseffizienz von mehr als 5 pJ/bit zu erreichen, sind für die Entzerrung komplexe Schaltungen erforderlich. Es wird erwartet, dass CPO (Co-Packaged Optics) eine bessere Bandbreitendichte und Energieeffizienz über 224 Gbit/s hinaus bietet. Mit CPO könne die Photonik in der Nähe des Computer-SoC integriert werden. Zhang erwartet, dass CPO eine über 170-fache Geschwindigkeit bringt, aber nur 20 Prozent der Leistung von Kupferkabelverbindungen verbraucht. Darüber hinaus seien optische Kanäle besser skalierbar als elektrische. Auch wenn noch verschiedene technische Probleme gelöst werden müssen – Zhang ist überzeugt: »Die Physik sagt uns, dass das der richtige Weg ist.«

Zhangs Fazit zu HPC/KI-Plattformen: »Mit den modernsten Prozesstechnologien können heute ungefähr 100 Mrd. Transistoren monolithisch in einen Die integriert werden, das reicht nicht für die Zukunft, man muss 3D-Technologien nutzen, um die Integrationsdichte weiter zu erhöhen, aber mit 3D-Silicon-Stacking- und Advanced-Packaging-Technologien lassen sich bis zu 1 Billion Transistoren integrieren.«

Technologien für die mobile Kommunikation

Die drahtlose Konnektivität ist ein Standardmerkmal für mobile Geräte und mittlerweile auch für die meisten IoT-Geräte geworden. Das spiegeln auch die Daten wider, auf die Zhang verweist: Nach einer Analyse von Cisco wurden im Jahr 2022 71 Prozent des Edge-IP-Verkehrs über drahtlose Verbindungen abgewickelt, »und dieser Anteil wird weiter steigen«, so Zhang. Angesichts der begrenzten Akkukapazität ist die Energieeffizienz weiterhin die wichtigste Anforderung bei der technologischen Optimierung mobiler Anwendungen, um die Akkulaufzeit zu verlängern – ein entscheidender Faktor für die Benutzerfreundlichkeit.

Mobile SoCs mit integrierten Anwendungsprozessoren (AP) und Mobilfunkmodem entwickeln sich weiter. Während höhere Verbindungsgeschwindigkeiten, geringere Latenzzeiten und eine bessere Energieeffizienz nach wie vor von entscheidender Bedeutung sind, inspiriert der Aufstieg von Edge-KI-Technologien für KI-unterstütztes 5G und potenziell KI-natives 6G die Integration dedizierter KI-Beschleuniger oder neuronaler Verarbeitungseinheiten (NPUs) in mobile SoCs, um das Nutzererlebnis mit Funktionen wie Gesichtserkennung, Fotoverbesserung, Sprachverarbeitung und Echtzeit-Szenenanalyse auf die nächste Stufe zu bringen. »All diese neuen und wachsenden Anforderungen an die Rechenleistung treiben die Migration der Produkttechnologie auf fortschrittlichere Prozessknoten weiter voran«, so Zhang.

Auch im Bereich der RF-TRX-Chip-Architektur hat sich in den letzten Jahren einiges getan. So wurden beispielsweise die im 4G-Mobilfunk-SoC befindlichen Datenkonverter in den 5G-NR-RF-TRX verlagert und Serdes-PHYs wurden hinzugefügt, um die Verbindungsschnittstelle digital zu konsolidieren und zu vereinfachen. Diese Architekturänderung führte zu einem erheblichen Wachstum des digitalen Anteils in RF-TRX-Bausteinen für Mobilfunk, was die technologische Migration der Mobilfunk-RF-TRX von der 28-nm-Technologie zu 12-nm-FinFET zur Folge hatte, um den Vorteil der digitalen PPA-Skalierung für stromverbrauchsempfindliche 5G-Geräte zu nutzen. Zhang ist überzeugt, dass sich dieser Trend bei 6G fortsetzen wird. Er erklärt weiter, dass sich keiner wundern sollte, wenn 6G-Transceiver dann mithilfe von 7- oder sogar 5-nm-Technologien gefertigt werden.

Automotive

Der Automotive-Markt ist mittlerweile für viele Hersteller aus der Halbleiterindustrie ein durchaus interessanter Markt, das gilt auch für TSMC. Denn auch dieser Zielmarkt braucht immer mehr Rechenleistung. Das gelte insbesondere für ADAS-Anwendungen, die ein höheres Autonomie-Level (L2+ bis L5) ermöglichen; in diesem Bereich steigt die benötigte Rechenleistung enorm, also werden auch hier zunehmend modernste Prozesse, sprich: 5 bis 3 nm, benötigt. »Für ’Eyes off, Hands off’ ist eine Rechenleistung von über 1000 TOPS in einem Auto notwendig«, so Zhang weiter. Dabei ist natürlich die Leistungsaufnahme ein echtes Problem, insbesondere bei Batteriefahrzeugen. Zhang berichtet aus seinem persönlichen Umfeld, dass ein Freund, der bei einem führenden OEM arbeitet, der meistgehasste Mann im Unternehmen sei. Denn alle strengten sich unglaublich an, die Leistungsaufnahme zu reduzieren, und dann komme er mit leistungsstärkeren Halbleitern, die aber eben auch deutlich mehr Leistung verbrauchen, und damit mache er alle Fortschritte der anderen zunichte. Der Ratschlag seinerseits, dann auf fortschrittlichere Prozesstechnologien zu wechseln, wird nicht verneint, allerdings braucht das seine Zeit. »Es gibt einen guten Grund dafür, warum die Automotive-Industrie typischerweise immer ein paar Generationen hinter den Prozesstechnologien aus dem Privatkunden- und HPC-Bereich bleiben: die stringenten Safety-Anforderungen«, so Zhang.

Die Anforderungen an die Defektdichte für alle Applikationen lege prinzipiell nahe 0 dppm (Defective Parts Per Million). Um dieses dppm-Niveau zu erreichen, seien Mio. Wafer notwendig, die über Jahre prozessiert werden. »Das ist natürlich nicht schnell genug, um die zukünftigen Automotive-Anforderungen erfüllen zu können. Deshalb müssen die Technologie-Entwickler bei der Foundry und die Designer auf der Automotive-Seite enger zusammenarbeiten, nur so lässt sich hier die Geschwindigkeit erhöhen«, fordert Zhang. TSMC versuche schon einiges, um der Automotive-Industrie entgegenzukommen. So wurden bereits Logiktechnologien für den Automobilbereich in 16, 7 und 5 nm entwickelt und sie erfüllten die Zuverlässigkeitsanforderungen der Automobilklasse 1 sowie die Anforderungen der Automobilindustrie an niedrige DPPM. Außerdem würden mittlerweile grundsätzlich Auto-Design-Rules genutzt, um die Defektdichte zu reduzieren. »Mit diesen Ansätzen bin ich überzeugt, dass wir dahin kommen, dass die Automotive-Industrie schneller auf modernere Prozessgeometrien zurückgreifen kann«, so Zhang.

Bei den MCUs, die bislang die wichtigsten Arbeitspferde im Fahrzeug sind, ergibt sich wiederum ein anderes Problem, das laut Zhang aber eigentlich schon gelöst ist. MCUs zeichnen sich typischerweise durch eine Menge an integriertem NVM-Speicher, sprich: Flash-Speicher, aus. Das Problem dabei ist, dass diese Speichertechnik nur bis Technologieknoten hinunter zu 28 nm skaliert werden kann, eine weitere Skalierung verbietet sich aufgrund der Kosten und der Komplexität. Zhang: »In zonalen Architekturen müssen MCUs höhere Rechenleistungen erreichen, also ist ein Wechsel auf kleinere Prozessstrukturen unabdingbar. Die gute Nachricht: Die Industrie hat neue Speichertechnologien entwickelt; MRAM und RRAM und diese sogenannten Emerging Technologies sind genau zum richtigen Zeitpunkt aufgetaucht, um hier als Ersatz zu fungieren. Wenn wir also auf MRAM oder RRAM setzen, können wir die Skalierung der Technologie schnell vorantreiben von 28 auf 16 und in Zukunft auf 7 nm.«

Ökonomisch betrachtet sind Halbleiter wichtiger denn je

Zum Abschluss seiner Keynote verweist Zhang auf folgendes Verhältnis: Der Foundry-Markt soll 2030 zirka 250 Mio. Dollar zum gesamten Halbleiterumsatz mit 1 Billion Dollar beitragen. Dieser gesamte Halbleiterumsatz wiederum soll einen Elektronikmarkt mit einem Volumen von 3 Billionen Dollar sowie eine Informationstechnologiebranche von 12 Billionen Dollar ermöglichen, was wiederum 145 Billionen Dollar an Bruttosozialprodukt ausmacht. Zhang abschließend: »Damit wird klar, dass der wirtschaftliche Einfluss von Halbleitern enorm ist.«

- »Goldenes Zeitalter für die Halbleiterindustrie«

- Technologieplattform für HPC/KI