Halbleiter-Entwicklung aus TSMC-Sicht

»Goldenes Zeitalter für die Halbleiterindustrie«

Dr. Kevin Zhang, TSMC, betont in seiner Keynote auf der diesjährigen ISSCC, dass die Halbleiterindustrie in ein neues goldenes Zeitalter startet, das nicht nur enorme Innovationen mit sich bringt, sondern auch wirtschaftlich äußerst reizvoll ist.

Die Zahlen, auf die Dr. Kevin Zhang, Senior Vice President für Business Development bei TSMC, seine Prognose eines goldenen Zeitalters stützt, sind äußerst vielversprechend. Heute weist der Halbleitermarkt ein Volumen von rund 500 Mrd. Dollar auf; laut Khan soll sich dieser Umsatz bis 2030 verdoppeln und dann 1 Billion Dollar betragen. Und diese Prognose ist sogar noch eher konservativ, denn in den Zahlen sind laut Zhang die Auswirkungen, die KI auf die Halbleiterindustrie haben wird, noch nicht einmal inbegriffen – und hier schlummert einiges an Volumen. Zhang zitiert in diesem Zusammenhang Lisa Su, CEO von AMD. Sie geht davon aus, dass sich der Umsatz ausschließlich mit KI-ICs 2028 auf 400 Mrd. Dollar belaufen wird. Und an ein durch KI getriebenes Umsatzwachstum im Halbleitersegment glauben auch andere; so führt Zhang weiter aus, dass Sam Altman, CEO von Open AI, plant, in Halbleiter zu investieren. Wie viel Umsatz durch KI konkret zu der 1 Billion Dollar kommen wird, will Zhang nicht mit Zahlen beziffern, aber auch er ist fest überzeugt, dass »KI das Wachstum im Halbleitermarkt noch beschleunigen wird«.

Vier Anwendungen stehen für 95 Prozent des Halbleitermarktes

Der größte Anteil am 1-Billionen-Dollar-Markt im Jahr 2030 soll auf HPC-Anwendungen (High-Performance-Computing) entfallen, 30 Prozent auf Mobilkommunikation, 15 Prozent auf Automotive und 10 Prozent auf IoT, und in den meisten Anwendungen steigt der Bedarf an modernsten Fertigungstechnologien. Zhang kommentiert, dass früher davon ausgegangen wurde, dass das Edge das meiste Silizium verbrauchen wird, aber heute gelte das nicht mehr, »und das liegt an der KI«, so Zhang. KI habe sich für HPC-Anwendungen schnell als wichtigster Wachstumsmotor herauskristallisiert. »KI weist einen unstillbaren Bedarf an energieeffizienten Recheneinheiten auf«, so Zhang weiter. Und auch diese Aussage untermauert er mit Zahlen: die Komplexität führender großer Sprachmodelle (LLMs) für generative KI ist enorm angestiegen, was natürlich auch eine deutlich höhere Rechenleistung erforderlich macht: »um mehr als das 10.000-Fache in weniger als zwei Jahren«, so Zhang weiter.

Auch die drahtlose Kommunikation treibe den Halbleiterbedarf nach oben, und damit auch den Bedarf an modernsten Prozesstechnologien. Er greift drei Technologien heraus: Mobilfunk, WiFi und Bluetooth – in allen drei Bereichen steige die Datenrate; also ist eine verbesserte Signalverarbeitung notwendig, und das beschleunige den Übergang auf modernste Siliziumtechniken. »WiFi 7 geht dieses Jahr in Produktion, und damit diese ICs die Ziele in Hinblick auf Performance und Leistungsaufnahme erreichen, müssen sie mit 7 nm gefertigt werden«, erklärt Zhang.

»Automotive durchläuft wirklich eine fundamentale Revolution, viele sprechen vom Software-definierten Fahrzeug, ich würde es vielmehr Silizium-definiertes Fahrzeug nennen, denn die Software läuft auf Silizium, und davon wandert vieles in die Fahrzeuge, angefangen bei Sensoren über Connectivity und die fortschrittlichsten Prozesstechnologien für Halbleiter, die das Fahrzeug autonom machen.«

Das Foundry-Modell hat die Welt verändert

Zur Erinnerung: Dr. Morris Chang hat vor 30 Jahren das »Pure Play Foundry«-Geschäftsmodell initiiert und damals TSMC gegründet. »Das hat die gesamte Halbleiterbranche verändert. Die Halbleiterunternehmen konnten sich auf die Produktentwicklung konzentrieren, die Foundry kümmerte sich um Technologie-Entwicklung und die Wafer-Fertigung. Das hat die Innovationsgeschwindigkeit deutlich gesteigert«, so Zhang. Das Foundry-Modell hat natürlich auch neue Player am Halbleitermarkt auf den Plan gerufen, mit steigendem Erfolg: Entfiel 2010 laut Zhang nur 2 Prozent des Halbleiterumsatzes auf Fabless-Unternehmen, waren es 2010 bereits 23 Prozent. Zhang: »2030 erwarten wir, dass der Fabless-Anteil auf 40 Prozent steigen wird, dazu kommen noch 10 Prozent des Umsatzes, der auf Systemhäuser und Cloud-Provider entfallen wird, die ebenfalls auf Foundries zurückgreifen.«

Skalierung muss weitergehen

Früher erfolgte die Skalierung ausschließlich über kleinere Prozessstrukturen, doch die Zeiten sind längst vorbei, »heute erfolgt die Skalierung über neue Transistorarchitekturen und neue Materialien«, so Zhang weiter. Als Beispiele verweist er auf FinFETs, die mit dem 16-nm-Knoten eingeführt wurden. Heute wiederum stehe die Industrie vor dem Übergang zu Nanosheet-Transistoren, die sich laut Zhangs Aussage durch eine hervorragende Elektrostatik und eine geringere Spannung auszeichnen. Auch wenn die Nanosheet-Transistoren sicherlich erst einmal ein paar Jahre die Produktion beherrschen werden, arbeitet TSMC bereits an der darauffolgenden Generation, und da setzt die Foundry auf CFETs, also das Übereinanderstapeln von NMOS- und PMOS-Transistoren. Zhang: »Damit lässt sich die Transistordichte fast verdoppeln.« In Hinblick auf neue Materialien arbeitet die Foundry beispielsweise an 2D-TMDs (quasi-zweidimensionale Übergangsmetall-Dichalcogenide), die laut Zhang noch einmal eine deutlich höhere Energieeffizienz versprechen als heutige Ansätze. Zhang betont: »CFETs sind nicht mehr nur eine Idee, die auf einer PowerPoint-Präsentation gezeigt wird, sondern wir haben schon funktionierende CFETs gefertigt.«

Jobangebote+ passend zum Thema

DTCO ist ein Muss

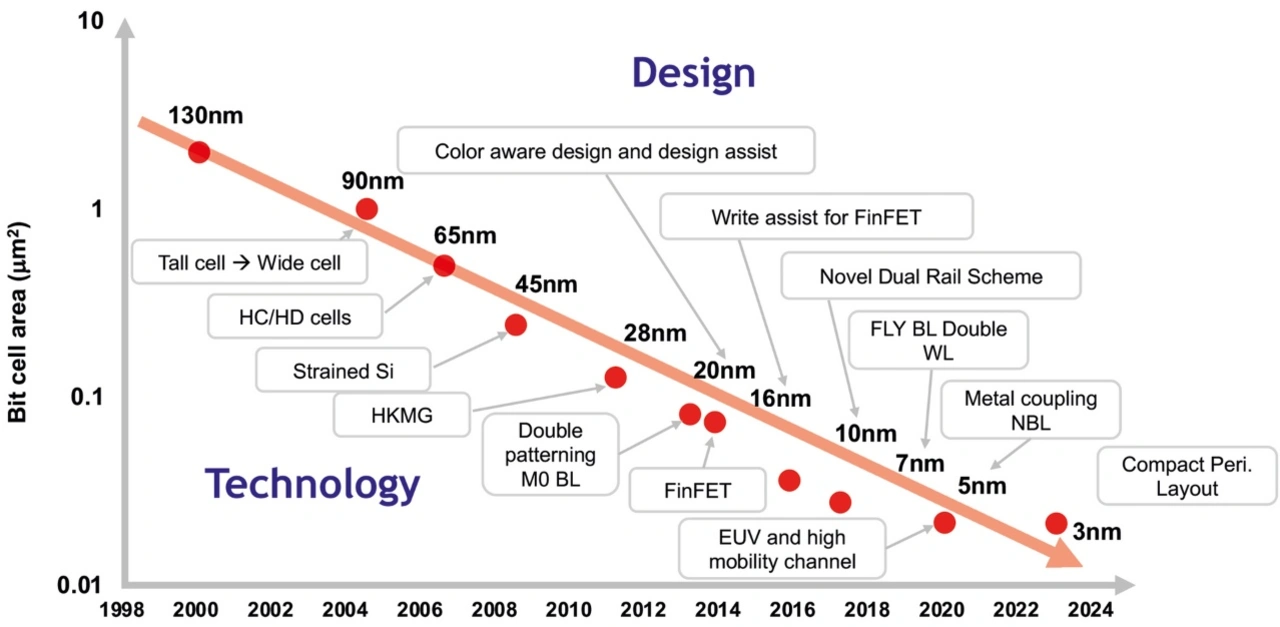

Auch wenn die Halbleiterindustrie in der Lage ist, die Skalierung munter weiter voranzutreiben, darf nicht vergessen werden, dass der Aufwand immer größer und kostspieliger wird. Deshalb ist Zhang überzeugt, dass ein DTCO-Ansatz (Design-Technology-Co-Optimization) unabdingbar ist; Designer und Technologieentwickler müssten zusammenarbeiten, um auf Produktebene das Maximum zu erreichen – DTCO ist ein Schlüssel zum Erfolg. Als Beispiel verweist er auf die sogenannte Fin-Depopulation, sprich: die Anzahl der Finnen pro Transistor zu reduzieren, wodurch die Höhe der Standard-Logikzellen und die Leistungsaufnahme sinken – problematisch dabei ist nur, dass damit auch Geschwindigkeit verlorengeht. Also haben sich die Technologieentwickler und Designer zusammengesetzt und einen neuen Ansatz entwickelt, den Zhang »FinFlex« nennt. Damit können Designer Transistoren mit 1 Finne oder 2 Finnen oder 2 Finnen und 3 Finnen mischen, um so auf Produktebene die optimale Geschwindigkeit, optimale Dichte und optimale Leistungsaufnahmen zu erreichen. Eine SRAM-Bitzelle ist für ihn ein weiteres Beispiel, das zeigt, was mit DTCO erreicht werden konnte. 2000 lag die Prozessgeometrie bei 130 nm, in diesem Jahr kommt eine 3-nm-Technologie zum Einsatz, »sodass wir eine Verbesserung der Dichte um einen Faktor von 100 realisieren konnten«, so Zhang. Hierfür sind natürlich einerseits die Verringerungen der Prozessstrukturen verantwortlich, aber eben nicht nur, sondern auch neue Design-Ansätze wie beispielsweise die NBL-Schreib-Assist-Technik, mit der sich die minimale Betriebsspannung (VMin) reduzieren lässt, »und das um über 300 mV für HD-SRAM«, so Zhang weiter. Für diese Fortschritte sind also »Technologieentwickler und Designer gleich wichtig«, betont Zhang.

Er erklärt weiter, dass die gezeigten Verbesserungen nicht um ihrer selbst willen stattfinden, sondern dass es bei allen Fortschritten schlussendlich darum ginge, ein energieeffizientes Computing zu erreichen. Und hier hätte die Industrie bereits viel erreicht, »innerhalb von etwas mehr als einer Dekade konnte zwischen den Prozessknoten N28 und N3 der Wert Perf/W/mm2 um über das 80-Fache verbessert werden.«

- »Goldenes Zeitalter für die Halbleiterindustrie«

- Technologieplattform für HPC/KI