Hohe Strahlung im Weltraum handhaben

Schaltungen für anspruchsvolle Umgebungen entwickeln

Fortsetzung des Artikels von Teil 1

Techniken, um Strahlungsschäden zu mindern

Die erste Möglichkeit ist die Gate-Auswahl. Bei einem Leistungstransistor, der nicht versehentlich einschalten darf, ist es besser, PMOS anstatt NMOS zu verwenden. Da die Wahrscheinlichkeit mit der Größe zunimmt, ist es von Vorteil, auf kleinere Halbleiterstrukturen zu setzen, was aber auch andere Risiken mit sich bringt (siehe unten). Außerdem gibt es spezielle Minderungstechniken für den IC-Entwurf, z.B. das Vermeiden von Gates mit vielen Eingängen.

Neben diesen grundlegenden Schritten gibt es eine Reihe spezifischerer Schutztechniken für Einzelereignis-Störungen und -Latches.

Jobangebote+ passend zum Thema

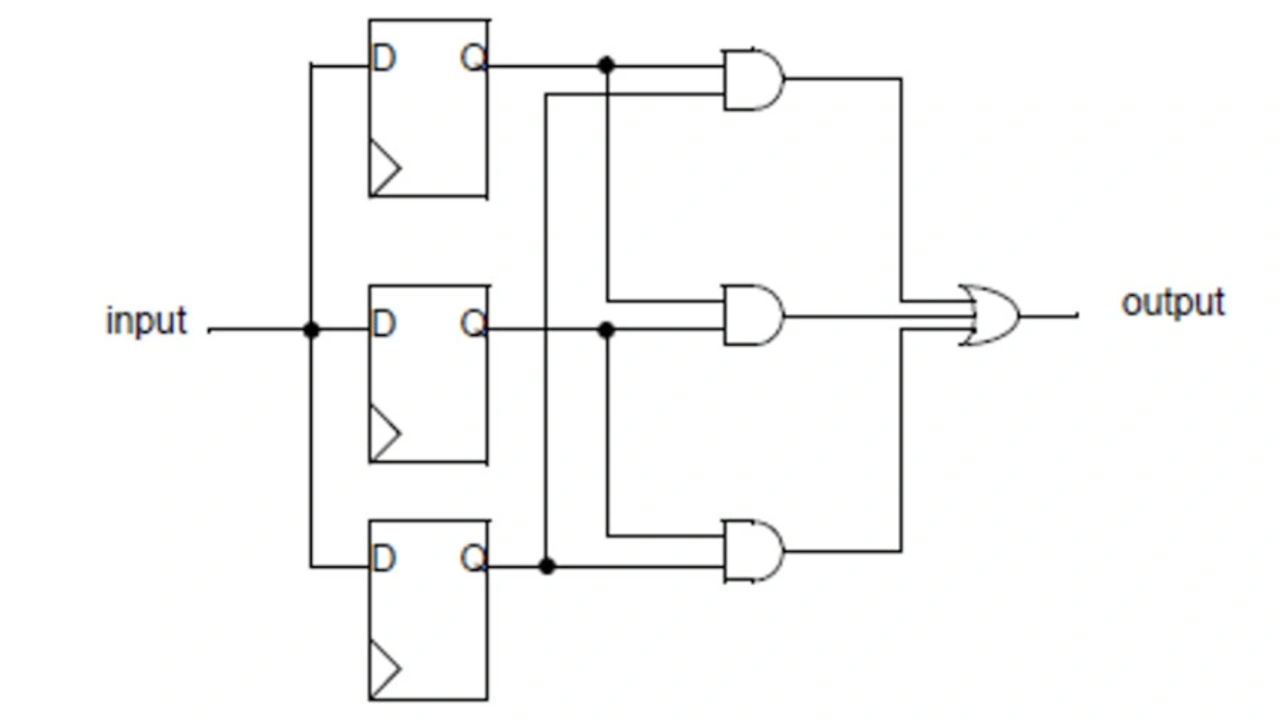

Besonders erwähnenswert ist das dreifach redundante Flip-Flop (Bild 4). Dies – und seine zahlreichen Varianten – kommt vor allem in der Luft-/Raumfahrttechnik zum Einsatz, da es den bestmöglichen Schutz gegen Störungen durch Einzelereignisse bietet. Das Prinzip hat jedoch Nachteile, die verhindern, dass es im gesamten System verwendet werden kann: Das dreifach redundante Flip-Flop verdreifacht die Größe der Schaltung und erhöht den Strombedarf des gesamten Systems. Redundante Flip-Flops sollten daher in kritischen Bereichen zum Einsatz kommen, in denen wichtige Entscheidungen getroffen werden müssen.

Um zu vermeiden, dass ein Taktfehler sich im gesamten System ausbreitet, ist es auch möglich, die Takte zu jedem der Flip-Flops zu jittern oder zu verschieben, sodass sie alle völlig unabhängig sind. Der Nachteil dieser Methode ist, dass sich die sichere Fehlerrate verdoppelt.

Schließlich könnte ein vollständig redundantes System mit getrennten Mikroprozessoren implementiert werden, bei dem die Ergebnisse verglichen werden. Und nur bei einer Stimmenmehrheit darf der Ausgang zur Entscheidung herangezogen werden. Auch dies ist eine teure Methode.

Kurz gesagt, die verwendete Technik, um Störungen durch Weltraumstrahlung zu mindern, hängt von der Kritikalität der Komponente und der Wahrscheinlichkeit ab, dass ein zerstörerisches Ereignis sie beeinträchtigt.

Vorhersage und Behebung von Softwarefehlern

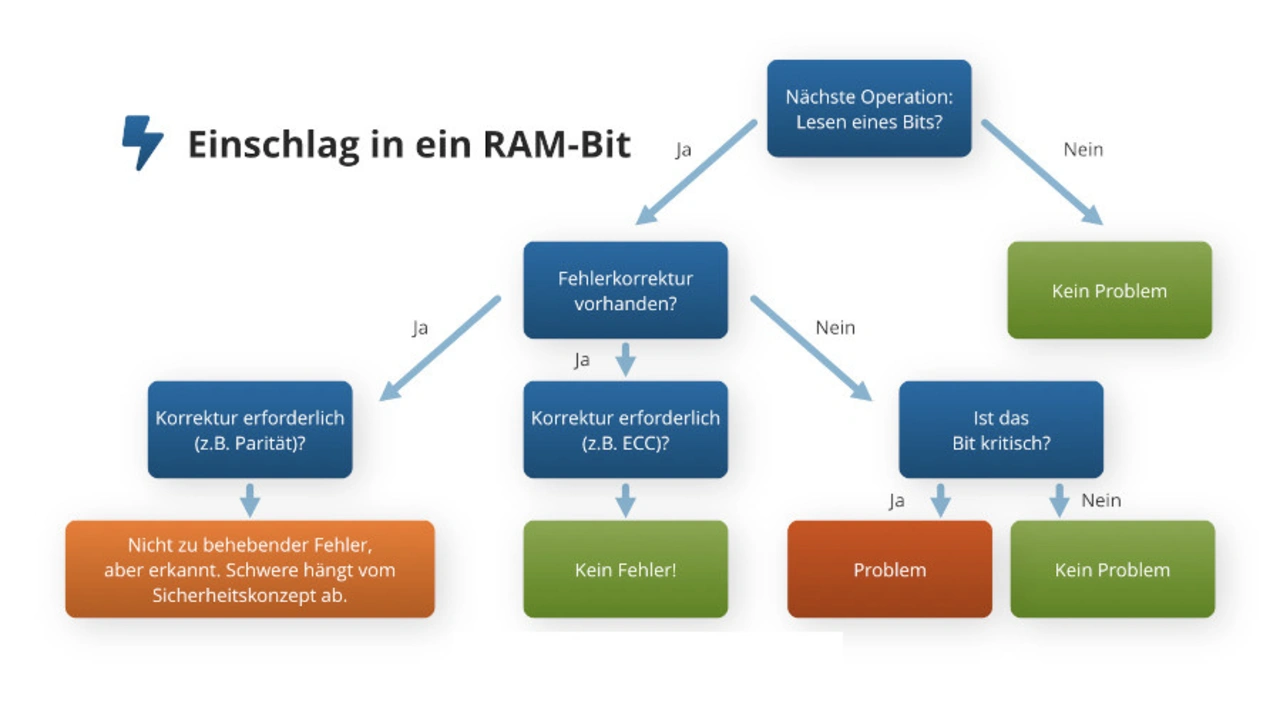

Nachdem ein eingehendes Teilchen auf den Arbeitsspeicher (RAM) trifft, hängt das Problem davon ab, ob der nächste Schritt im Lesen oder Schreiben besteht. Werden diese Daten gelesen, ist das problematisch. Ist die nächste Operation ein Schreibvorgang, wird der Fehler behoben. Wie sagt lässt sich also voraussagen, was passieren wird?

Das ist abhängig von der Software des Systems. Natürlich lassen sich Strategien zur Speicherauffrischung einsetzen, um den Speicher korrekt zu halten. Geht man noch einen Schritt weiter, lassen sich einige Funktionen – bei denen die Daten für die Funktion nicht kritisch sind – einfach ignorieren und der Betrieb wird fortgesetzt.

Für kritischere Elemente lässt sich Fehlerkorrekturcode (ECC) einsetzen, der in den Speicher integriert ist und Fehlerschutz bereitstellt. Dabei ist zu beachten, dass nicht immer genug Korrekturparität bereitsteht, um jeden Fehler zu beheben. Aber selbst in diesem Fall ist dieser Ansatz immer noch in der Lage, einen Fehler zu erkennen, auf ein Problem aufmerksam zu machen und zu verhindern, dass bestimmte Aktionen oder Funktionen in kritischen Phasen ausgeführt werden (Bild 5).

Weitere Maßnahmen sind zyklische Redundanzprüfungen in Kommunikationskanälen oder das Verändern des Hammning-Abstands der Zustandsmaschinen auf größer als 1, um ein versehentliches Umschalten in einen anderen Zustand zu vermeiden. Darüber hinaus ist es möglich, Software-Selbsttestverfahren durchzuführen und die Hardware die Software sowie die Software die Hardware überprüfen zu lassen. Und natürlich gibt es externe Watchdogs, wie sie bei Embedded-Systemen üblich sind. Schließlich gibt es noch eine ferngesteuerte Überwachung des internen Takts oder einen Sicherheitstakt, der von einem PC aus wiederhergestellt werden kann.

Umgang mit nicht-ionisierender Strahlung

Wie erwähnt, gibt es auch Effekte durch nicht-ionisierende Strahlung, wobei Verdrängungsschäden zu allmählichen Effekten führen. Bits im Halbleiteraufbau werden dabei im Laufe der Zeit beschädigt und Leckagen verursachen eine verringerte Verstärkung in Bipolartransistoren.

Dieser Effekt wurde in Satelliten dokumentiert, insbesondere bei CMOS-Bildsensoren, die im Laufe der Zeit beschädigt wurden. In diesem Fall muss das Bauteil möglicherweise irgendwann ausgetauscht werden, oder größere Komponenten kommen zum Einsatz, um Ersatzpixel bereitzustellen und die Lebensdauer des Satelliten zu verlängern. Auch hier gibt es eine Reihe von Techniken, um Störungen zu mindern, z.B. eine Form von Redundanz oder ECC. Auf der Analogseite ist es ratsam, die Spannung und den Strom sorgfältig zu überwachen, damit sich Latch-ups leichter erkennen und bestimmte Bereiche schnell abschalten lassen.

Das IC-Layout spielt dabei eine entscheidende Rolle: Bei uns auf der Erde werden die Leiterbahnen im Chip mit jeder Generation immer enger aneinandergereiht, und die IC-Entwürfe gehen bis an die Grenzen dessen, was die Technik zulässt. Bei Elektronik, die für den Einsatz im Weltraum ausgelegt ist, bietet es sich jedoch an, den Abstand zwischen den kritischen Knotenpunkten zu vergrößern, um einen besseren Schutz zu gewährleisten.

Ist Ihr IC nun raumfahrttauglich?

Lassen sich nun serienmäßige Standard-Bauelemente im All verwenden? Die Antwort ist etwas schwieriger, denn es kommt darauf an.

Die NASA hat versucht, vier Klassen A, B, C und D zu definieren (Tabelle), die von der Mission und der angestrebten Lebensdauer abhängen. Beispielsweise befindet sich das James-Webb-Weltraumteleskop in der Klasse A.

| Charakterisierung | Klasse A | Klasse B | Klasse C | Klasse D |

|---|---|---|---|---|

|

Priorität (Kritische Bedeutung für den NASA-Strategieplan) |

Hohe Priorität | Hohe Priorität | Mittlere Priorität | Niedrige Priorität |

| Nationale Bedeutung | Sehr hoch | Hoch | Mittel | Niedrig bis mittel |

| Komplexität | Sehr hoch bis hoch | Hoch bis mittel | Mittel bis niedrig | Mittel bis niedrig |

| Lebensdauer der Mission (primärer Grundauftrag) | Lang, >5 Jahre | Mittel, 2–5 Jahre | Kurz, <2 Jahre | Kurz, <2 Jahre |

| Kosten | Hoch | Hoch bis mittel | Mittel bis niedrig | Niedrig |

| Startbeschränkungen | Kritisch | Mittel | Wenige | Wenige bis keine |

| Wartung während des Betriebs | N/A | Nicht möglich oder schwierig | Möglich | Möglich und planbar |

| Alternative Forschungsmöglichkeiten oder Rückflugmöglichkeiten | Keine Alternativen oder Rückflugmöglichkeiten | Wenige oder keine Alternativen/Rückflugmöglichkeiten | Wenige oder keine Alternativen/Rückflugmöglichkeiten | Erhebliche Alternativen/Rückflugmöglichkeiten |

| Beispiele | HAST, Cassini, JIMO, JWST | MER, MRO, Entdeckungsflüge, ISS-Ausstattung/Versorgung | ESSP, Forschungsflüge, MIDEX, komplexe ISS-Subrack-Baugruppen | SPARTAN, GAS Can, Technik-Demonstratoren, einfache ISS-, Express-Middeck- und Subrack-Baugruppen, SMEX |

Tabelle. Die NASA unterscheidet vier Klassen von Weltraumtauglichkeit bei elektronischen Bauelementen, abhängig von der Mission. (Quelle: EnSilica)

Der Autor

Paul Morris

ist CMO des ASIC-Designhauses EnSilica. Das Unternehmen hat eine Reihe von ASICs für die Märkte Automotive, Medizintechnik und Satellitentechnik entwickelt, darunter Ka-Band-Fahrzeug-zu-Satelliten-Kommunikations-ICs für die Europäische Weltraumorganisation (ESA).

- Schaltungen für anspruchsvolle Umgebungen entwickeln

- Techniken, um Strahlungsschäden zu mindern