Skalierung im Interconnect vorantreiben

Das Semi-Damascene-Verfahren: ein Wendepunkt?

Die »Semi-Damascene«-Metallisierung gilt als kostengünstiges Verfahren, um das Problem der zunehmenden RC-Verzögerung bei einem Metal-Pitch von 20 nm und darunter zu adressieren.

Vor mehr als fünf Jahren schlug das imec das »Semi-Damascene«-Verfahren vor, um die zunehmenden Probleme der RC-Verzögerung im Zusammenhang mit Cu-Dual-Damascene-Verfahren in fortgeschrittenen Technologieknoten zu lösen. In Kombination mit einem strukturierbaren Metall wie Ru verspricht Semi-Damascene, die Anforderungen an RC-Verzögerung, Flächenbedarf, Kosten und Energieeffizienz zu erfüllen und damit einen Skalierungspfad für das Interconnect zu bieten.

Dieser Artikel untersucht das Konzept, fasst die aktuellen Herausforderungen sowie die potenziellen Lösungsansätze von Ru-basierten Semi-Damascene-Verfahren zusammen und appelliert an die Wissenschaft und Industrie, gemeinsam den Weg für eine industrielle Umsetzung zu ebnen.

Das Potenzial von Semi-Damascene für zukünftige Interconnects

1997 markierte die Einführung des Cu-Dual-Damascene-Integrationsschemata im Back-End-of-Line (BEOL) von Logik- und Speicherchips einen Wendepunkt in der Halbleitertechnik. Die Halbleiterhersteller verabschiedeten sich von der subtraktiven Aluminiumstrukturierung und setzten stattdessen auf nasschemische Verfahren wie die Kupfergalvanisierung und das chemisch-mechanischen Polieren (CMP). Dieser radikale Wandel war notwendig, um die zunehmende RC-Verzögerung in Aluminium-basierten Verbindungen zu bewältigen, die durch das steigende RC-Produkts verursacht wurden.

Da das Kupfer-Dual-Damascene-Verfahren kostengünstig und auf mehrere Schichten des BEOL-Stacks angewendet werden kann, ebnete es den Weg für viele nachfolgende Generationen von Logik- und Speichertechnologien.

Doch in einigen Jahren werden die Metallabstände in den kritischsten BEOL-Schichten unter 20 nm fallen und damit auch die Cu-Dual-Damascene-Technik an ihre Grenzen stoßen. Wenn sich die Länge der immer kleiner werdenden Metallleitungen der mittleren freien Weglänge der Elektronen von Kupfer annähern, steigt die RC-Verzögerung drastisch an. Hinzu kommt noch, dass die Cu-Metallisierung eine Barriere- sowie eine Liner- und eine Deckschicht erforderlich macht, um eine gute Zuverlässigkeit zu gewährleisten und zu verhindern, dass Cu in das Dielektrikum eindiffundiert. Diese Zusatzschichten beanspruchen jedoch einen erheblichen Anteil der ohnehin begrenzten Leitungsbreite, sodass die wertvolle, leitende Fläche nicht vollständig für das Verbindungsmetall genutzt werden kann. Diese Probleme zwingen die Halbleiterindustrie dazu, alternative Metallisierungsverfahren zu entwickeln, die bei engen Metal-Pitches bessere Leistungskennzahlen aufweisen.

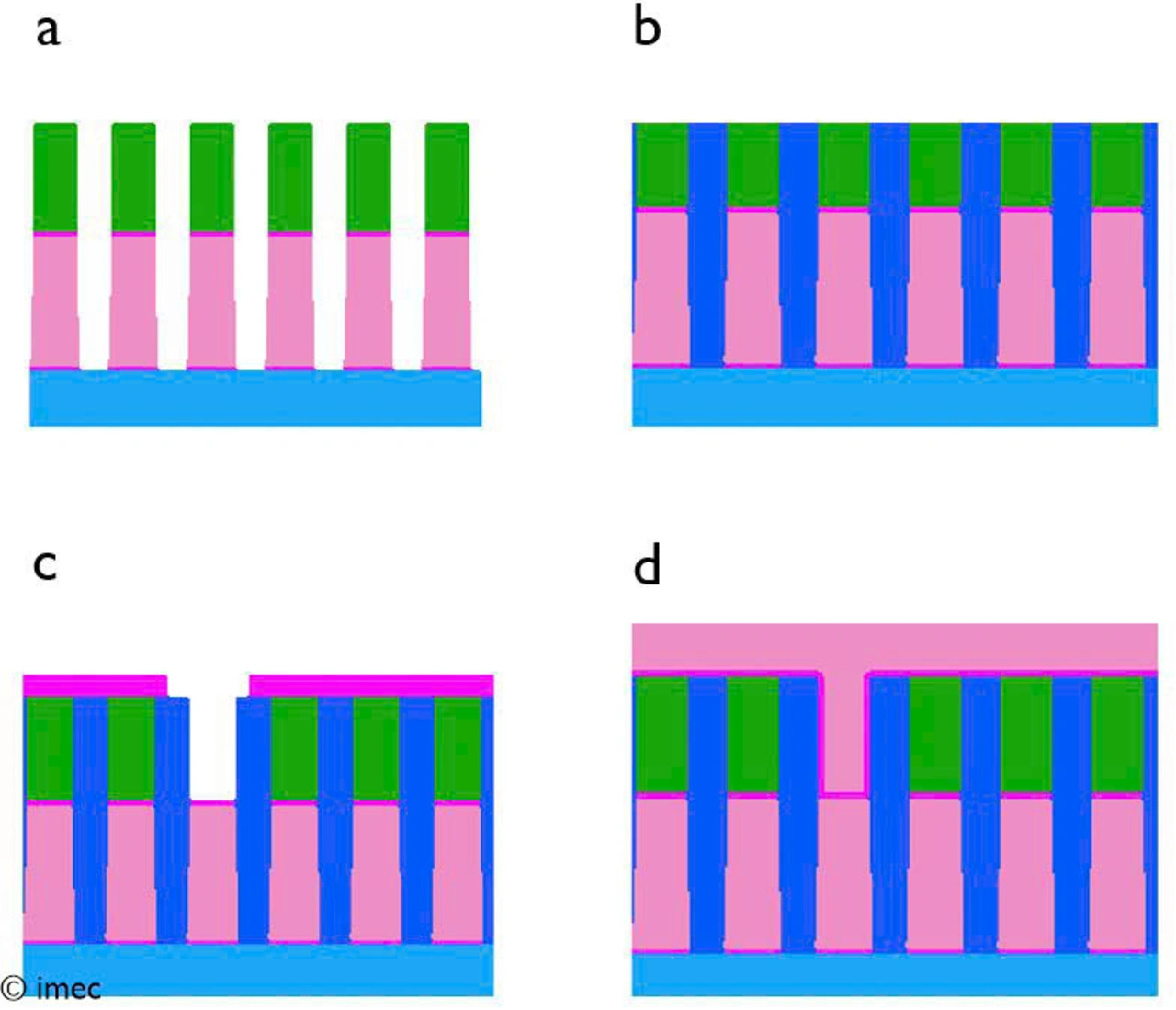

Nach der Anmeldung eines ersten Patents im Jahr 2017 stellte das imec der Halbleiterbranche im Jahr 2020 ein neues Metallisierungskonzept mit dem Namen »Semi-Damascene« vor. Ähnlich wie bei der Al-basierten Metallisierung beginnt die Semi-Damascene-Integration mit der direkten Strukturierung (oder subtraktiven Metallisierung) der ersten lokalen Verbindungsmetallschicht. Dafür ist ein strukturierbares Metall wie Wolfram (W), Molybdän (Mo) oder Ruthenium (Ru) erforderlich.

Die Verbindung zur nächsten Metallisierungsschicht erfolgt über eine Durchkontaktierung, die mithilfe einer Single-Damascene-Technik gefertigt wird: Dabei wird in das Dielektrikum ein Loch geätzt, das anschließend mit Metall gefüllt und überfüllt wird – das heißt, die Metallabscheidung wird solange fortgesetzt, bis sich eine Metallschicht über dem Dielektrikum gebildet hat. Diese Metallschicht wird anschließend maskiert und geätzt, um die zweite Verdrahtungsebene zu erzeugen, deren Leitungen orthogonal zur ersten Schicht ausgerichtet sind.

Jobangebote+ passend zum Thema

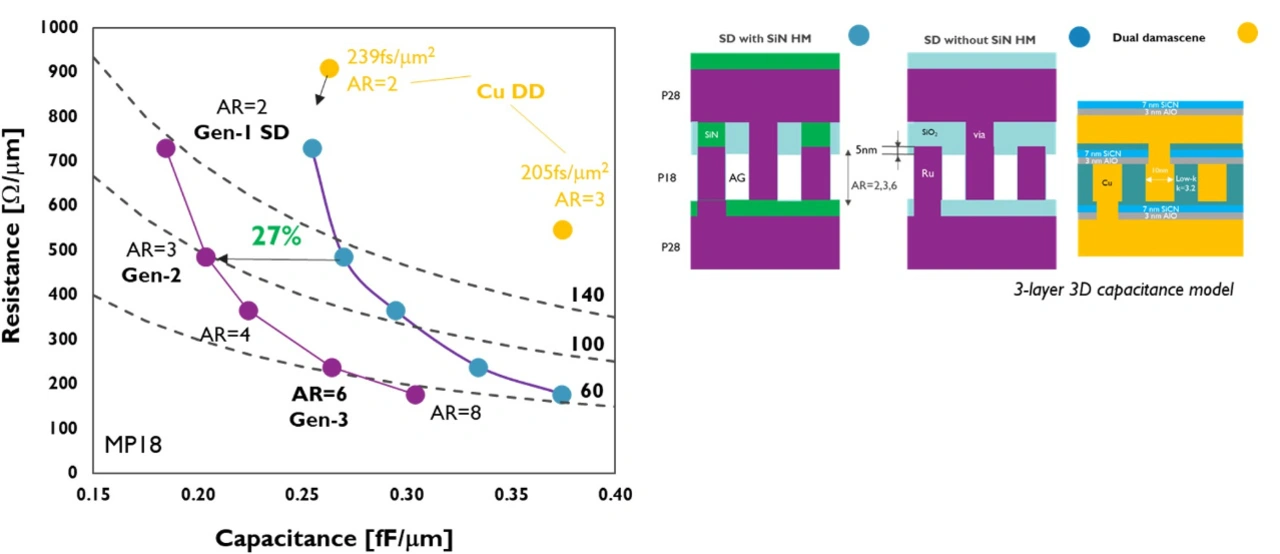

Das Konzept von Semi-Damascene ist vielversprechend. Es kann als zweischichtiges Metallisierungsmodul betrachtet werden, das sich potenziell auf mehrere Schichten erweitern lässt – was es kostengünstig macht. Durch das subtraktive Ätzen können Leitungen mit einem höheren AR (Aspect-Ratio) hergestellt werden, als das bei herkömmliche Kupferverbindungen der Fall ist, was wiederum den Widerstand verbessert. Darüber hinaus können die Metallleitungen potenziell mit Luftspalten anstelle von Low-k-Dielektrikum kombiniert werden. Luftspalten haben eine niedrigere Dielektrizitätskonstante, was zu einer geringeren Kapazität innerhalb der Ebene führt. Außerdem macht Semi-Damascene die Verwendung von Metall-CMP überflüssig, was den Prozessablauf vereinfacht und eine präzisere Kontrolle der Linienhöhe ermöglicht. Zudem bietet die Verwendung von hochschmelzenden Metallen wie Ruthenium zusätzliche Vorteile. Sie können ohne Barriereschicht verwendet werden, was sowohl den Durchgangs- als auch den Leitungswiderstand verringert. Außerdem sind diese Metalle widerstandsfähiger gegen Elektromigration und weisen bei kleineren Abmessungen insgesamt einen geringeren Widerstand als Kupfer auf.

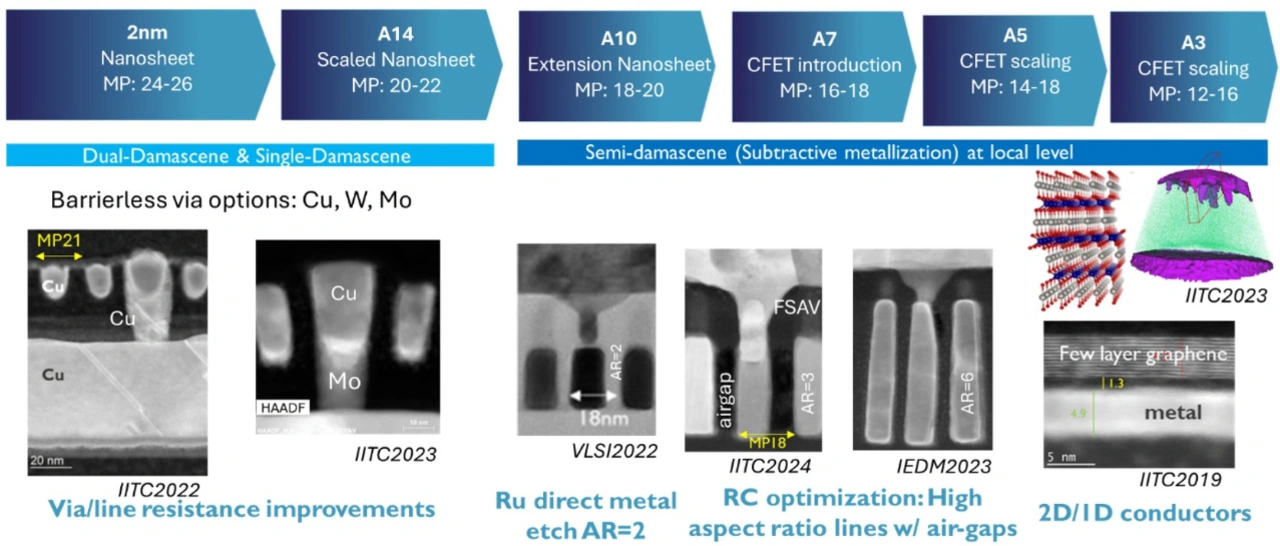

Und was sagt die Branche dazu? Vielversprechend, aber auch disruptiv

Seit imec die Semi-Damascene-Integration eingeführt hat, haben zahlreiche Organisationen begonnen, ähnliche Verfahren zu erforschen. Durch Simulationen und Experimente konnten dabei stetige Fortschritte erzielt werden. Inzwischen wurde der erste Schritt des Verfahrens, das subtraktive Ätzen der ersten Metallschicht, erfolgreich demonstriert und von verschiedenen Organisationen auf Konferenzen vorgestellt. Experimente haben eindeutig gezeigt, dass der Ersatz von Cu durch subtraktiv geätztes Ru in der ersten lokalen Verbindungsschicht bereits deutliche Vorteil bringen kann, selbst bei einem moderaten AR von ungefähr 2. Für nachfolgende Generationen könnte das AR auf 3 oder sogar 6 erhöht werden und mit mehreren lokalen Metallschichten kombiniert werden. Es gibt immer mehr Belege aus der Forschung und Entwicklung dafür, dass Semi-Damascene tatsächlich eine vielversprechende Option darstellt und einen Interconnect-Skalierungspfad bietet.

Gleichzeitig gibt es aber auch noch offene Fragen. Die Industrie erwägt derzeit, die erste Generation der Semi-Damascene-Technologie in die Entwicklungsphase zu überführen, die Phase vor der eigentlichen Produktion. Wie bei jeder neuen Technologie erfolgt dieser Übergang jedoch nicht von heute auf morgen.

Die Semi-Damascene-Integration stellt die konventionelle BEOL-Fertigung vor Herausforderungen. Sie erfordert neue Werkzeuge und Materialien, und vielleicht werden einige Fehlermechanismen in der Forschungsphase nicht erfasst. Solche Investitionen lohnen sich nur, wenn die Technologie das Potenzial hat, für mehrere Technologiegenerationen genutzt werden zu können.

Während der erste Schritt mit nur einer Metallschicht umfassend dokumentiert ist, wird weniger über die Umsetzung eines zwei- oder sogar mehrschichtigen Integrationsschematas gesprochen. Damit könnten aber das volle Potenzial und die Vorteile von Semi-Damascene voll ausgeschöpft werden. Aus diesem Grund ermutigt das imec die F&E-Gemeinschaft, die Diskussion zu eröffnen, dabei zu helfen, die bestehenden Lücken zu schließen, und Erkenntnisse über die mehrschichtige Integration auf Konferenzen zur Verbindungstechnologie auszutauschen.

Interconnect-Roadmap: Einführung von fünf Generationen Semi-Damascene

Das imec schlägt vor, die nachfolgenden Generationen des Semi-Damascene-Verfahrens schrittweise einzuführen. Die Einführung der ersten Generation ist für den Logik-Technologieknoten A10 oder A7 vom imec vorgesehen, bei dem der Metal-Pitch der kritischsten Verbindungen nur noch 18 nm beträgt. Zu diesem Zeitpunkt wird die Integration von GAA-Nanosheet (Gate-All-Around) voraussichtlich zum Standard gehören, während CFETs (Complementary FETs) noch nicht zum Einsatz kommen. Die Einführung von Semi-Damascene wird daher die einzige größere Änderung sein, mit der sich Halbleiterhersteller auseinandersetzen müssen.

Das imec empfiehlt, subtraktiv geätztes Ru in der ersten lokalen Metallisierungsschicht (M0) einzusetzen, die auf MOL (Middle of Line) folgt. Diese erste Generation wird ein AR von 2 aufweisen, was etwas höher ist als das heutige typische AR von Kupferleitungen (zirka 1,6). Dank der Eigenschaft von Ru, dass auch bei kleinen Metal-Pitches keine Barriere notwendig ist, bietet dieser Ansatz bereits Vorteile in Bezug auf den elektrischen Widerstand und Zuverlässigkeit im Vergleich zu Kupfer.

In der zweiten Generation plant das imec, das AR der M0-Verbindungsleitungen auf 3 zu erhöhen, um den Widerstand weiter zu senken. Darüber hinaus soll M0 mit einer barrierefreien Durchkontaktierung kombiniert werden. Da ein höherer AR-Wert jedoch oft dazu führt, dass die Kapazität innerhalb der Ebene steigt, werden in dieser Generation Luftspalte anstelle von dielektrischen Füllmaterialien mit niedrigem k-Wert verwendet. Luftspalte bieten nicht nur eine niedrigere Dielektrizitätskonstante, sondern lösen auch das »Lückenfüllungsproblem«: die Herausforderung, sehr schmale Gräben gleichmäßig mit Dielektrika zu füllen.

In der dritten Generation werden Vias und eine zweite Metallschicht mithilfe des Semi-Damascene-Verfahrens hinzugefügt, so dass eine echte Semi-Damascene-Integration für die beiden kritischsten Schichten des BEOLs erreicht wird: M0 und M2. In der vierten Generation könnten sogar noch weitere Schichten mithilfe des Semi-Damascene-Verfahrens integriert werden. Das AR wird dabei schrittweise auf 4, 5 und sogar noch mehr erhöht werden – je nachdem, was machbar ist. Bis zu einem AR von ungefähr 6 wird erwartet, dass in Kombination mit Luftspalten ein signifikanter RC-Vorteil gegenüber anderen Optionen erreicht wird.

Langfristig, möglicherweise in der 5. Generation, plant das imec alternative Metalle in die Semi-Damascene-Roadmap aufzunehmen. Denkbar sind strukturierbare binäre oder ternäre Verbindungen, die im Vergleich zu herkömmlichen Einzelmetallen bessere Leistungskennzahlen bei engen Abständen zwischen den Verbindungen bieten.

Das Semi-Damascene-Verfahren könnte somit der nächste Wendepunkt in der BEOL-Fertigung werden. Es zeichnet sich durch viele Vorteile aus, nicht nur in Bezug auf Widerstand, Kapazität und Flächenverbrauch. Experimente und Simulationen deuten außerdem auf einen geringeren Energieverbrauch und bessere thermische Eigenschaften im Vergleich zu Cu-Dual-Damascene-Verfahren hin. Gleichzeitig ermöglicht die oben beschriebene schrittweise Einführung, die Risiken zu minimieren, die typischerweise mit der Einführung einer neuen Technologie verbunden sind.

Fortschritt bei weiteren Generationen des Semi-Damascene-Verfahren

Während die erste und zweite Generation bereit sind, in die Entwicklungsphase einzutreten, sind für die Weiterentwicklung der nachfolgenden Generationen noch umfangreiche Forschungsarbeiten notwendig. Die wesentlichen Herausforderungen lassen sich in drei Bereiche unterteilen: die Integration von mehreren Schichten, ddie weitere Erhöhung des AR und die Erforschung neuer Metalle für die fünfte Generation.

Im Folgenden werden die jüngsten Fortschritte vorgestellt, über die imec-Forscher berichteten. Die Ergebnisse sollen nicht nur dazu beitragen, die verbliebenen Lücken zu schließen, sondern auch den Dialog fördern und andere Forschungseinrichtungen dazu ermutigen, die Forschung vom imec zu ergänzen – zum Nutzen des gesamten Ökosystems.

Auf dem Weg zu mehrschichtigen Integrationsschemata in hochentwickelten Interconnect-Systemen

Wie bereits erwähnt, ist das Semi-Damascene-Verfahren im Wesentlichen ein Integrationsschema mit zwei Metallschichten, das jedoch potenziell auf mehrere Schichten erweitert werden kann. Die Prozessoptimierung für mehrschichtige Konzepte steckt jedoch noch in den Kinderschuhen. Welche Methoden eignen sich am besten für die Implementierung? Welche Lithografie- und Ätzverfahren, Hartmasken und Resiste sollen verwendet werden? Und wie lassen sich die Durchkontaktierungen (Vias) integrieren, die die extrem schmalen Verbindungsleitungen der nachfolgenden BEOL-Schichten verbinden?

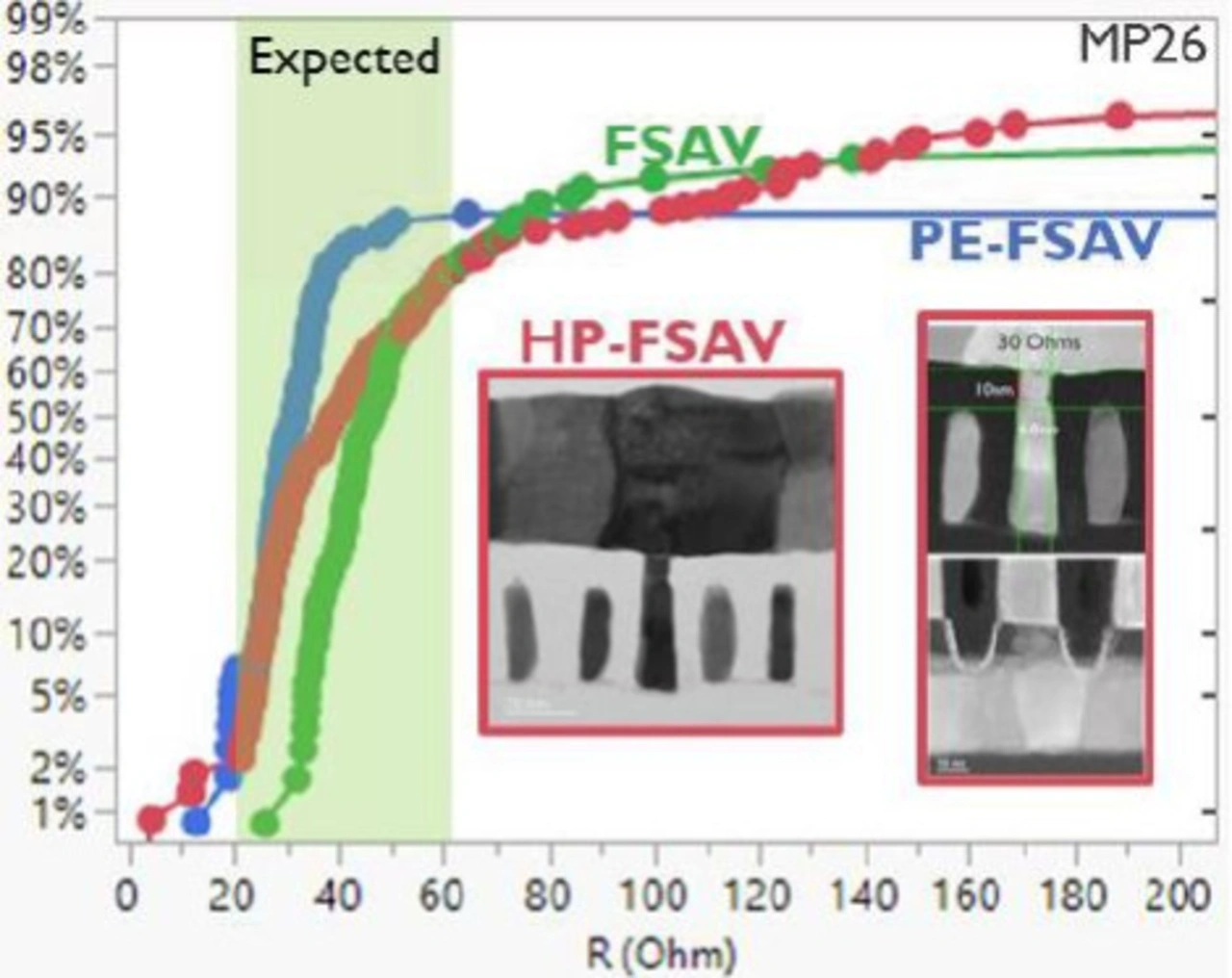

Für die letzte Frage hat das imec bereits vor einiger Zeit die vollständig selbstausrichtende Durchkontaktierung (FSAV: Fully Self-Aligned Via) als Schlüsselbaustein für Semi-Damascene vorgeschlagen. FSAVs ermöglichen eine präzise Ausrichtung der Leitungen und Durchkontaktierungen (sowohl am oberen als auch am unteren Ende der Durchkontaktierung), was entscheidend ist, um Leckströme zwischen Durchkontaktierung und Leitungen zu minimieren. Bisher wurden bereits von mehreren Forschungseinrichtungen, einschließlich dem imec, diverse Integrationsschemata für FSAVs vorgestellt.

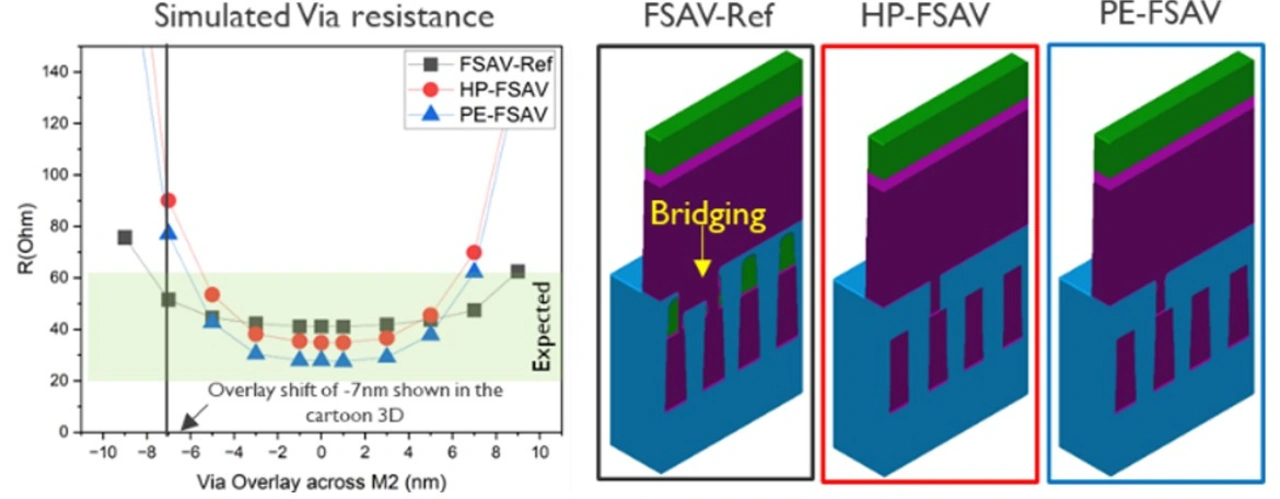

Auf der IITC 2024 war das imec die erste Organisation, die verschiedene FSAV-Integrationsmöglichkeiten miteinander verglich, um herauszufinden, wie FSAVs am effektivsten in einer 300-mm-Fab implementiert werden können. Dabei standen folgende Fragen im Vordergrund: Wie lässt sich der angestrebte Via-Widerstand bei optimaler Überlagerung von Via und Leitung erreichen und wie kann gleichzeitig eine geringe Variabilität sowie hohe Reproduzierbarkeit über den gesamten 300-mm-Wafer sichergestellt werden?

Neben dem herkömmlichen Einzel-Damascene-Verfahren (FSAV) zur Herstellung der Durchkontaktierung (bei dem ein Loch in ein SiO2-Dielektrikum geätzt und anschließendem mit Metall aufgefüllt wird) hat das imec auch zwei säulenbasierte FSAV-Integrationsschemata (hier wird die Durchkontaktierung als Säule durch direktes Ätzen einer Metallschicht geformt) untersucht. Die beiden Varianten werden als »Hybrid-Säule« (HP-FSAV) und »Säule mit Ätzstoppschicht« (PE-FSAV) bezeichnet.

Die drei Integrationsschemata unterscheiden sich in der Anzahl der Prozessschritte sowie in den verwendeten Strukturierungs- und Ätzverfahren, der Integration von Hartmasken und der Art des Resists. Für alle drei Varianten konnte jedoch gezeigt werden, dass die Ziele in Bezug auf Widerstand und in Bezug auf den Spielraum für die Überlagerung von Via zur Leitung erreicht werden können. Der größte Unterschied besteht in der Gleichmäßigkeit des Widerstands über den gesamten Wafer hinweg. Alle Ansätze bieten ausreichende Prozessfenster für die Lithografie- und Ätzverfahren. Daher sind sie mit dem derzeitigen Equipment für die direkte Metallätzung kompatibel.

Andere Arbeiten vom imec zeigen, dass es auch ein selbstausrichtendes Prozessfenster für die Implementierung von Luftspalten gibt. Diese sind erforderlich, um den Kapazitätsvorteil beizubehalten, wenn die Leitungs-ARs weiter erhöht werden.

Der aktuelle Stand der Technik zeigt, dass es bereits praktikable Optionen gibt, um mindestens zwei Schichten mit dem Semi-Damascene-Verfahren zu realisieren. Allerdings ist die Anzahl der bisher hergestellten Wafer begrenzt. Daher ermutigt das imec andere Organisationen, das Puzzle zu vervollständigen und das Ökosystem der Industrie entscheiden zu lassen, welche Option den besten Weg nach vorne darstellt.

Schrittweise AR-Erhöhung von Semi-Damascene-Leitungen: Hürden verstehen und überwinden

Eine weitere Verringerung des Widerstands von Ru-basierten Semi-Damascene-Leitungen lässt sich durch die Erhöhung des Aspect-Ratios erreichen. Im Jahr 2022 zeigte das imec erstmals, dass die Implementierung von Semi-Damascene-Leitungen mit einem AR von 6 die RC-Metrik im Vergleich zu Schemata mit einem niedrigeren AR signifikant verbessern kann. Kurz darauf deuteten erste Experimente darauf hin, dass Leitungen mit einem hohen AR auch mit Mehrschicht-Schemata kompatibel sind.

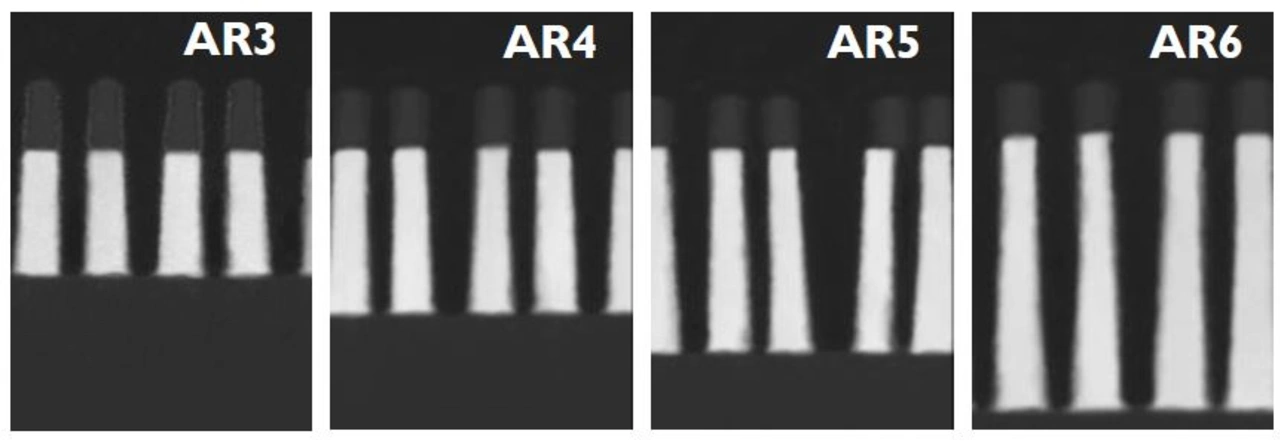

Die Herstellung von Verbindungsleitungen mit moderaten ARs (2 und 3) ist inzwischen relativ gut verstanden. Doch die Erhöhung des ARs, bei gleichzeitiger Sicherstellung eines niedrigen Leitungswiderstands und einer hohen Zuverlässigkeit, stellen weiterhin eine technische Herausforderung dar. Deshalb muss jeder Prozessschritt, von der Strukturierung und Ätzung, über die Reinigung bis hin zur Fehlerkontrolle, kritisch hinterfragt werden.

Ein Beispiel ist das direkte Metallätzen, das die Seitenwände der Ru-Leitungen angreift und dadurch zu Defekten wie Leitungsbrüchen führen kann. Dieses Problem verschärft sich mit steigendem AR. Um den Leitungswiderstand so gering wie möglich zu halten, ist ein grundlegenderes Verständnis für die Prozesse zur Leitungsbildung und deren Zuverlässigkeit bei hohem AR erforderlich.

Als erste wichtige Erkenntnis entdeckten die Forscher vom imec, dass die Zusammensetzung des Stacks, der zur Bildung von Metallleitungen mit hohem AR verwendet wird, einen erheblichen Einfluss auf den Widerstand der Semi-Damascene-Leitungen hat. Dabei zeigte sich, dass Defekte in Form von Leitungsbrüche der Hauptgrund für die Leistungsunterschiede bei verschiedenen Stapelzusammensetzungen sind.

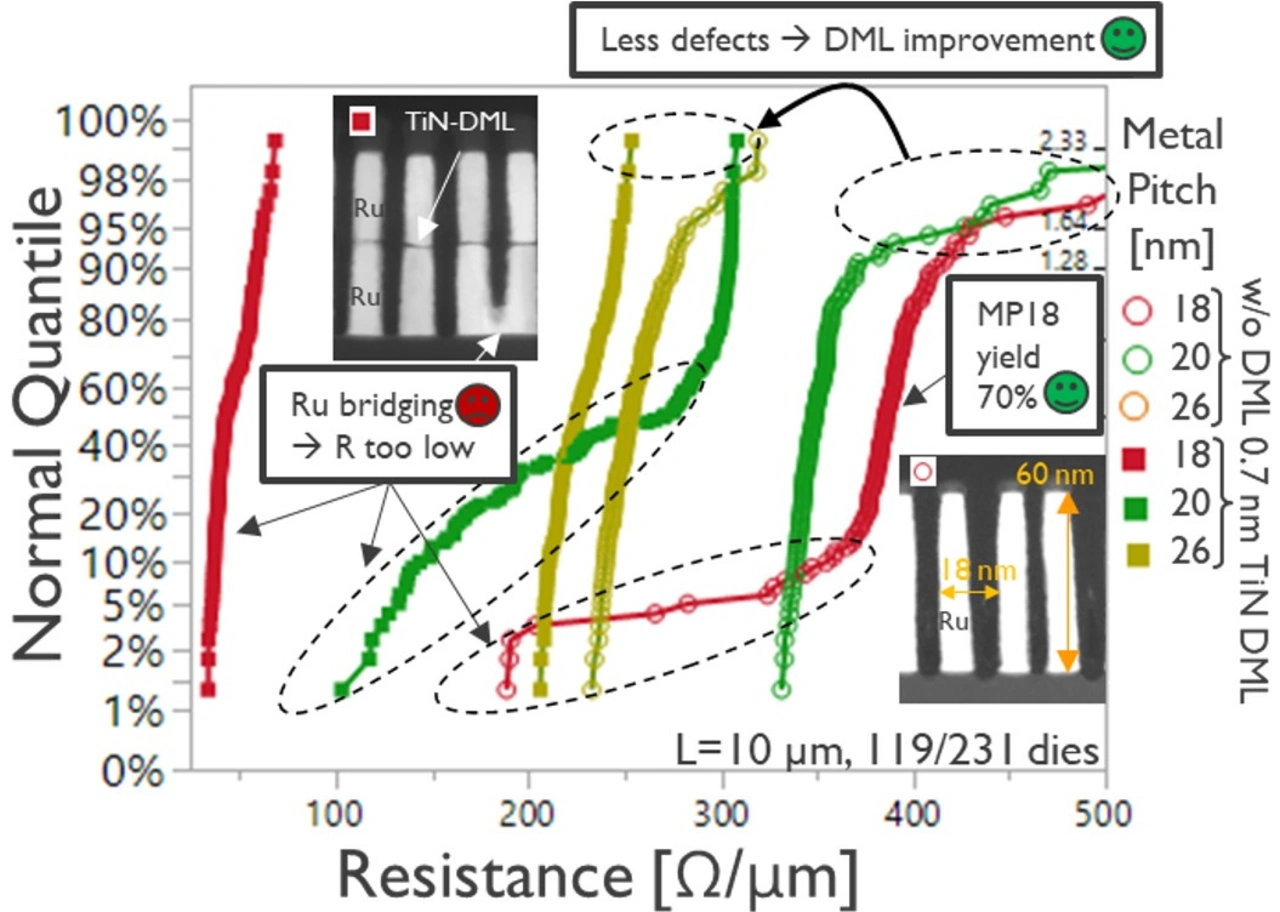

Durch zahlreiche Experimente identifizierte das imec einen optimalen Stack, der mit einer 1-nm-dicken TiN-Schicht beginnt, die für eine bessere Haftung sorgt. Darauf folgt physikalisch abgeschiedenes (PVD) Ru. Im Vergleich zu anderen in der Studie verwendeten Zusammensetzungen bot dieser Ansatz über die gesamte Höhe der Metallleitungen hinweg den geringsten Widerstand.

Die Studie lieferte außerdem erste Hinweise darauf, dass die Defektanfälligkeit der Leitungen von der Kornstruktur und der Kristallorientierung der Ru-Metallkörner abhängig ist. Diese morphologischen Parameter wiederum hängen stark von der Methode ab, die zur Abscheidung von Ru verwendet wird – mit einer klaren Präfenz für PVD.

Zusätzlich zu diesen Erkenntnissen hat das imec vor kurzem einen innovativen Ansatz entwickelt, um Leitungen mit hohem AR weiter zu verbessern. Dafür wird eine extrem dünne TiN- oder W-Schicht (Sub-nm-Schicht) zwischen zwei Ru-Schichten eingefügt. Dieser Aufbau ist im Vergleich zu anderen Stacks ohne diese zusätzliche Schicht weniger anfällig für Defekte an den Seitenwänden und damit für Leitungsbrüche.

Der wesentliche Vorteil dieser »Defektminderungsschicht« besteht darin, dass die Fertigung von Leitungen mit hohem AR und großer Länge bei geringer Defektdicht möglich wird. Dies ist ein vielversprechendes Ergebnis für die Entwicklung eines Ru-Semi-Damascene-Verfahrens mit einem AR von ≥6.

Die Ergebnisse wurden auf dem VLSI-Symposium 2024 vorgestellt. Die Experimente belegten eine gute Zuverlässigkeit der Leitungen bis hinunter zu einem Pitch von 24 nm. Es sind aber noch weitere Arbeiten erforderlich, um die Ergebnisse für einen Pitch von 18 nm zu optimieren und auszuweiten, die Kompatibilität mit der Integration von Luftspalten zu demonstrieren und eine ausreichende Sicherheitsreserve in Bezug auf einen zeitabhängigen dielektrischen Durchbruch (TDDB) und mechanische Zuverlässigkeit nachzuweisen.

Fortschritte in der Verbindungstechnik: die Suche nach alternativen Leitern

Die bisherige Arbeit zur Semi-Damascene-Integration konzentrierte sich vor allem auf die Verwendung von Ru als bevorzugtem Leiter. Vor einigen Jahren begann das imec zu untersuchen, ob es andere Metalle mit noch besseren Eigenschaften gibt. Die Suche wurde von einfachen Metallen auf binäre und ternäre geordnete Verbindungen ausgeweitet. Nach einer vielversprechenden Vorstudie schlossen sich weltweit mehrere Forschungs- und Entwicklungsgruppen der Idee an und suchten ebenfalls nach geeigneten Legierungen.

Vor kurzem traf sich die Gemeinschaft auf dem vom imec organisierten Themenworkshop »Novel metals for advanced interconnects« im Rahmen des VLSI 2024, um den Stand der Technik und zukünftige Forschungsrichtungen zu diskutieren - sowohl aus industrieller als auch aus akademischer Sicht.

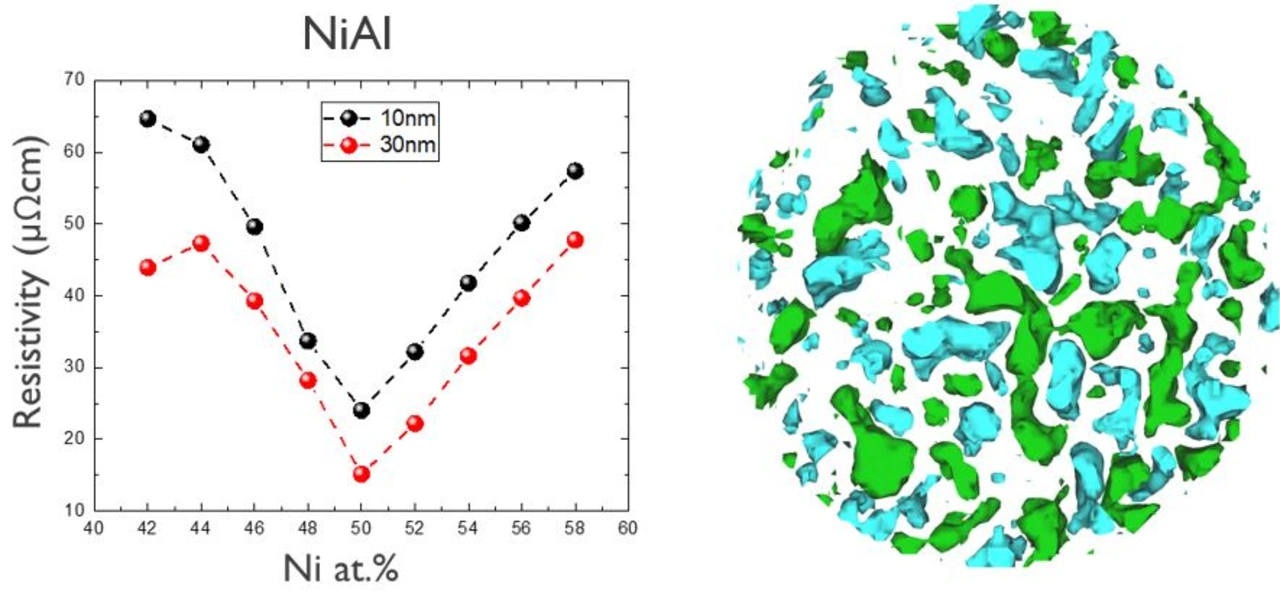

Da die Liste potenzieller Legierungen riesig ist, hat das imec eine einzigartige Methodik entwickelt, um mögliche Kandidaten auszuwählen und zu bewerten. Für den Vergleich mit Cu wurden zwei Kennzahlen ermittelt: die Kohäsionsenergie der Verbindung und das Produkt aus spezifischem Widerstand und der mittleren freien Weglänge der Ladungsträger. Mithilfe von Ab-initio-Simulationen wurde eine engere Auswahl von Kandidaten erstellt, darunter zum Beispiel intermetallische Aluminide, die als Ansatzpunkt für weitere experimentelle Arbeiten dienten.

Derzeit untersuchen Forschungsgruppen weltweit, wie sich der spezifische Widerstand dieser Legierungen bei miniaturisierten Abmessungen verhält. Dabei wurde beispielsweise festgestellt, dass bei der Abscheidung intermetallischer Aluminiden in dünnen Schichten Defektmechanismen, die während der Dünndschihtabscheidung auftreten, das Verhalten des spezifischen Widerstands beeinflussen. Das Verständnis dieses Zusammenhangs ist entscheidend, um den Widerstand gezielt kontrollieren zu können. Das imec hat außerdem herausgefunden, dass die globale und lokale Kontrolle der Zusammensetzung ein wichtiger Hebel zur Minimierung des Widerstands ist.

Sobald Wege gefunden wurden, um den Widerstand vielversprechender binärer und ternärer Legierungen zu optimieren, besteht der nächste Schritt darin, sie in relevante Metallisierungskonzepte zu integrieren und die Herausforderungen der Semi-Damascene-Verarbeitung zu lösen. Das imec lädt Universitäten und Forschungsgruppen dazu ein, gemeinsam Muster- und Ätzstrategien zu erforschen und Verfahren festzulegen.

Obwohl noch viel Arbeit zu leisten ist, bietet die Erforschung alternativer Metalle einen vielversprechenden Ansatz, der stetige Fortschritte zeigt. Eine noch intensivere Zusammenarbeit wird erforderlich sein, um diese Entwicklungen schließlich in die fünfte Generation des Semi-Damascene-Verfahrens einzuführen.

Fazit

Die Semi-Damascene-Metallisierung stellt möglicherweise den nächsten Wendepunkt in der BEOL-Fertigung dar, wobei die Branche derzeit über die Einführung des subtraktiven Ätzens in der ersten lokalen Verbindungsschicht diskutiert. Obwohl noch nicht einmal die erste Generation der Semi-Damascene-Technik in Produktion ist, richtet das imec auf Basis experimenteller Erkenntnisse bereits den Blick auf zukünftige Generationen der Semi-Damascene-Technik.

Der Schwerpunkt liegt dabei auf mehreren Metallschichten und Durchkontaktierungen, einer schrittweisen Erhöhung der Aspect-Ratios und der Einführung neuer Metalle. Damit diese nächsten Generationen Realität werden können, sind gemeinsame Anstrengungen und eine enge Zusammenarbeit zwischen Wissenschaft und Industrie erforderlich, unterstützt durch umfangreiche Datensammlungen auf beiden Seiten.

Autor:

Zsolt Tokei ist imec-Fellow und Programmdirektor für Nano-Verbindungen beim imec. Er kam 1999 zum imec und hatte seitdem verschiedene Positionen im technischen Bereich der Organisation inne. Zunächst war er als Prozessingenieur und Forscher im Bereich der Kupfer-Low-k-Verbindungen tätig, dann leitete er die Sektion Metall. Später wurde er leitender Wissenschaftler und Programmdirektor für Nano-Verbindungen. Er erwarb einen M.S. (1994) in Physik an der Universität Kossuth in Debrecen, Ungarn. Im Rahmen einer von der ungarischen Universität Kossuth und der französischen Universität Aix Marseille-III gemeinsam betreuten Doktorarbeit erwarb er 1997 seinen Doktortitel in Physik und Materialwissenschaften. 1998 nahm er eine Stelle als Postdoktorand am Max-Planck-Institut in Düsseldorf an. Nach seinem Wechsel zum imec arbeitete er weiter an einer Reihe von Verbindungsthemen, darunter Skalierung, Metallisierung, elektrische Charakterisierung, Modulintegration, Zuverlässigkeit und Systemaspekte.