Optimiert ist nicht immer optimal

Automatisierung des Entwurfs analoger ICs – Teil 1

Fortsetzung des Artikels von Teil 1

Das Dilemma von Optimierungsalgorithmen

Fast alle Verfahren der Entwurfsautomatisierung basieren auf dem Prinzip der Optimierung. Optimierungsalgorithmen, die im folgenden auch kurz »Optimierer« genannt werden, können daher als »Allzweckwaffe« der EDA gelten.

Grundlage optimierender Verfahren ist eine mathematische Modellbildung des realen Entwurfsproblems, aus der sich ein abstrakter Lösungsraum ergibt, in dem nun rechnergestützt eine Suche stattfindet.

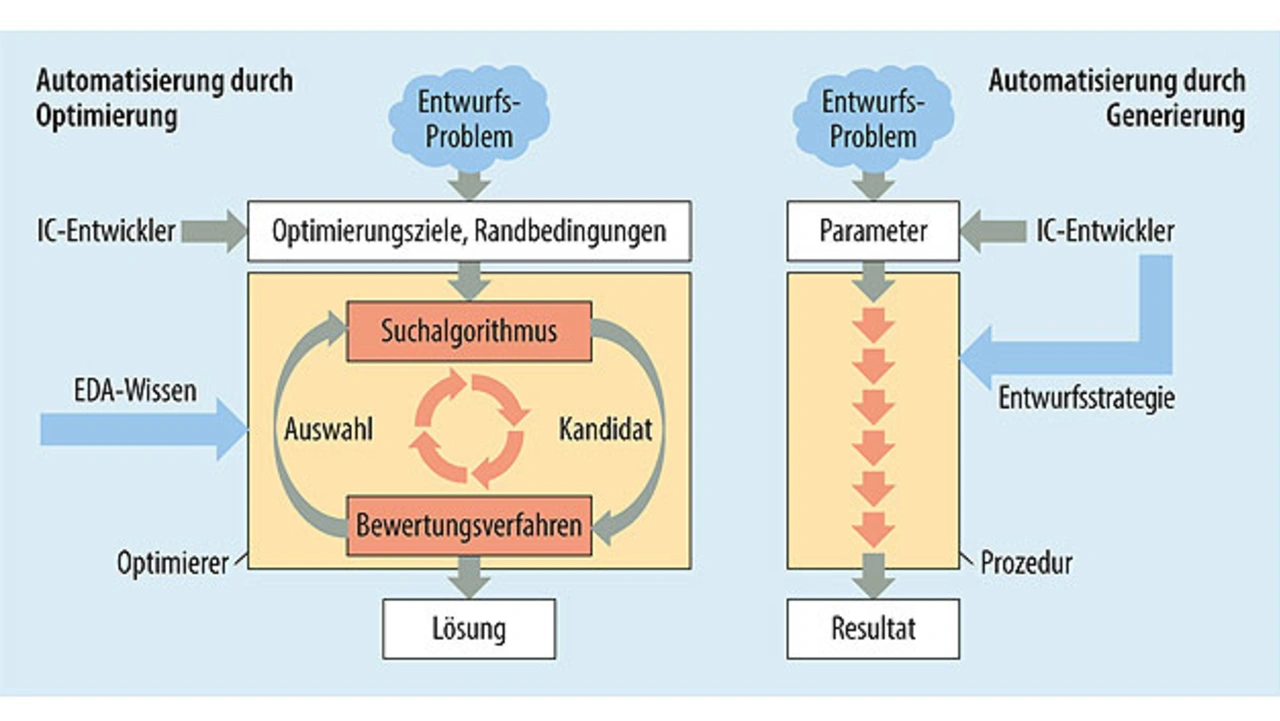

Die linke Seite des Bildes 3 zeigt das Grundprinzip: es werden fortlaufend Lösungsoptionen selektiert bzw. generiert (Suchalgorithmus), deren Güte anhand quantifizierter Optimierungsziele bewertet werden (Bewertungsverfahren) [1]. Nach Erreichen eines Abbruchkriteriums – entweder ein Laufzeit-Limit oder eine erreichte Lösungsqualität – wird die algorithmisch gefundene Lösung auf die reale Entwurfsaufgabe rücktransformiert und bildet die »reale« Lösung der Entwurfsaufgabe.

Jobangebote+ passend zum Thema

Die Effizienz dieses zumeist iterativen Vorgehens wird bestimmt durch die Fähigkeit des Suchalgorithmus, sich hinreichend schnell einer hinreichend guten Lösung anzunähern und durch die Schnelligkeit des Bewertungsverfahren. Mit hoher algorithmischer Effizienz lassen sich also gute, im besten Falle optimale Lösungen erzeugen.

Damit ist allerdings noch nichts über die Qualität der realen Lösung ausgesagt, denn diese hängt auch noch davon ab, inwieweit sich die Realität des Entwurfsproblems in der mathematischen Modellbildung widerspiegelt. Grundsätzlich kommt es bei der Modellbildung nämlich immer zu einer Abstrahierung von der Realität.

Hieraus ergibt sich ein grundlegendes Dilemma aller Optimierer [1]: Hohe algorithmische Effizienz wird regelmäßig dadurch erkauft, dass nur Teilaspekte des realen Problems abgebildet werden. In diesem Falle leidet die Qualität der realen Lösung unter der hohen Abstraktion bei der Modellbildung.

Versucht man andererseits die Realität möglichst detailgenau abzubilden, führt dies zu einer hohen Komplexität des Lösungsraums, in dem nun keine effiziente Lösungssuche mehr gelingt, was wiederum zulasten der Qualität der realen Lösung geht.

Fazit: Die Qualität der realen Lösung ist bei Optimierern prinzipiell begrenzt. Algorithmisch optimierte Entwurfslösungen werden daher in aller Regel von den Entwicklungsingenieuren keineswegs als optimal empfunden.

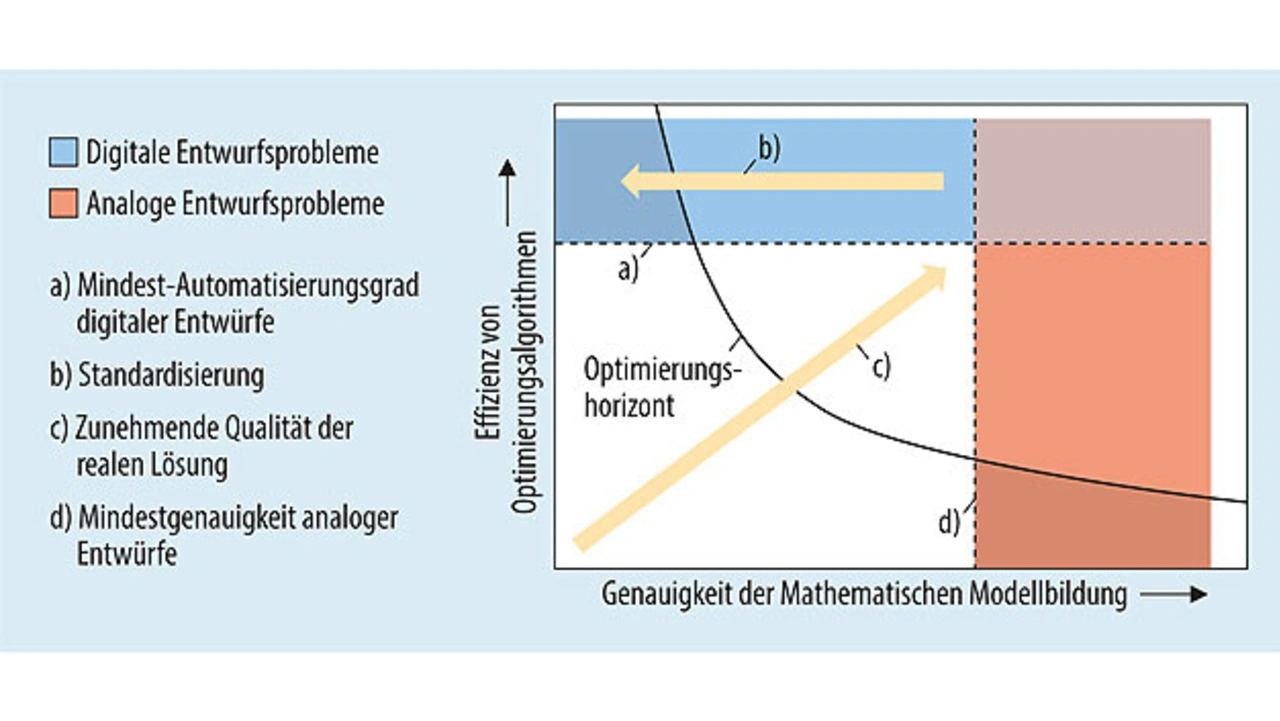

Bild 4 veranschaulicht diesen Zusammenhang qualitativ in einem Schaubild mit der Abbildungsgenauigkeit der Modellbildung auf der Abszisse und der Effizienz des Optimierers auf der Ordinate. Die Qualität der realen Lösung kann dabei als Produkt dieser beiden Größen aufgefasst werden, die also entlang der Winkelhalbierenden (Pfeil) den stärksten Zuwachs hat.

Die eingezeichnete Kurve zeigt den Verlauf des mit Optimierern prinzipiell erreichbaren Optimierungshorizonts als Folge des oben geschilderten Dilemmas. Entwurfsprobleme müssen also unterhalb (sozusagen diesseits) dieses Optimierungshorizonts liegen, damit mit Optimierern eine zufriedenstellende reale Lösung erreichbar ist [1].

Digital und analog – der entscheidende Unterschied

Digitale Schaltkreise sind elektrische Schaltungen die bekanntermaßen auf die Verarbeitung diskreter Signalwerte spezialisiert sind. Dies erlaubt in der elektrischen Realisierung eine Beschränkung auf zwei – prinzipiell beliebige – Spannungswerte, die schaltungstechnisch nicht exakt getroffen und nur sicher voneinander unterschieden werden müssen. Indem außerdem Lesevorgänge nur in bestimmten Zeitabschnitten zugelassen werden (Taktung), werden auch mögliche Probleme bei den Signalübergängen elegant ausgeblendet.

Dadurch vereinfacht sich aber nicht nur die technische Umsetzung. Die rigide Standardisierung auf wert- und zeitdiskrete Signale stellt eine so starke, bereits in der Entwurfsrealität vorgenommene Abstraktion dar, dass eine weitgehend exakte mathematische Modellbildung gelingt, die wiederum den Einsatz hocheffizienter Optimierer ermöglicht.

Aufgrund des extremen Funktionsumfangs digitaler ICs ist dieser hohe Automatisierungsgrad beim Entwurf zwingend notwendig. Digitale Entwurfsprobleme sind daher im Schaubild des Bildes 4 oberhalb einer Mindestautomatisierungsgrenze angesiedelt [2]. Ihre Charakteristik erlaubt nötigenfalls weitere Standardisierungsmaßnahmen, z.B. die Beschränkung auf sogenannte Standardzellen im IC-Layout, mit denen eine Entwurfsaufgabe so weit vereinfacht wird, dass sie links – also diesseits – des Optimierungshorizonts zu liegen kommt (oberer dunkler Bereich), wo eine hinreichend einfache Modellbildung und somit die Anwendung hocheffizienter Automatismen möglich werden. Bei Digital-IC-Entwürfen wird deshalb auch von Entwurfsproblemen mit hoher quantitativer Komplexität gesprochen [1].

Ganz anders ist die Situation bei analogen Schaltungen. Hier geht es um wert- und zeitkontinuierliche Signale, die möglichst verzerrungsfrei zu verarbeiten sind. Dies erfordert die gezielte Berücksichtigung aller physikalischer Wirkzusammenhänge, um die Vielzahl unterschiedlicher Störeinflüsse – beispielsweise Fertigungstoleranzen, Temperaturabhängigkeiten, Unsymmetrien, Rauschen, die zu einer Signalabweichung führen können, schaltungstechnisch aktiv zu unterdrücken. Im Unterschied zur Charakteristik digitaler IC-Entwürfe sind analoge Entwurfsprobleme also durch eine hohe qualitative Komplexität gekennzeichnet, deren Lösung einer gezielten Ausnutzung aller Entwurfsfreiheitsgrade bedarf, was eine Standardisierung und damit eine Abstraktion geradezu verbietet [1, 2].

Analoge Entwurfsprobleme befinden sich im Schaubild des Bildes 4 daher rechts einer (anspruchsvollen) Mindestgenauigkeitsgrenze für die Modellbildung. Analoge Entwurfsprobleme sind nur in simplen Einzelfällen durch Optimierungsverfahren zufriedenstellend lösbar (dunkler Bereich rechts unten). Im Allgemeinen liegen sie aber oberhalb – also jenseits – des Optimierungshorizonts und widersetzen sich damit einer Automatisierung durch Optimierung. Aus diesem Grund basiert der Entwurf analoger Schaltungen bis heute auf dem Expertenwissen erfahrener Schaltungsentwickler, die ihre weitgehend händisch erarbeiteten Ergebnisse durch Simulationen verifizieren.

Lösungsansatz: generieren statt optimieren

Ausgehend von diesen Beobachtungen und Erkenntnissen verfolgen die Forscher an der Hochschule Reutlingen die Idee, die Entwurfsautomatisierung analoger Schaltungen nicht mittels Optimierern anzugehen, sondern Wege zu erforschen, wie das erfahrungsbasierte Vorgehen der IC-Schaltungs- und Layoutentwickler mit Automatismen imitiert werden kann. Einen Ansatz bieten prozedurale Verfahren, die in der EDA auch als Generatoren bekannt sind.

Ein Generator ist, vereinfacht gesagt, ein Ablaufskript, das die von einem menschlichen Experten durchgeführten Entwurfshandlungen nachempfindet. Es handelt sich dabei um eine ausführbare Prozedur, die in aller Regel parametergesteuert eine bestimmte, eng umrissene Entwurfsaufgabe löst. Die seit den 1990er-Jahren eingesetzten Layoutgeneratoren zur Erzeugung individuell dimensionierter Bauteile sind ein weithin bekanntes Beispiel hierfür.

Im Unterschied zu Optimierern, die eine »eigenintelligente« Lösungsfindung vornehmen, reproduzieren Generatoren die von Experten vorausgedachten Lösungswege [1].

Ein Generator kann somit als die Wiederverwendung einer Lösungsstrategie angesehen werden. In dieser Lösungsstrategie steckt das Expertenwissen zur Lösung der oben erwähnten qualitativ komplexen analogen Entwurfsaufgabe. Dieses Know-how muss nun nicht mehr formalisiert werden, sondern ist implizit enthalten. Es ist in aller Regel auch immer schaltungstypspezifisch.

Im zweiten Teil stellen die Autoren zwei Entwurfsverfahren vor, die auf diesem Paradigma der prozeduralen Automatisierung aufbauen:

- Expert Design Plan (EDP) zum automatischen Entwurf analoger integrierter Schaltungen und

- Self-organized Wiring and Arrangement of Responsive Modules (SWARM) zur automatischen Layouterzeugung analoger integrierter Schaltungsmodule.

Teile der hier vorgestellten Forschungsarbeiten entstanden im Forschungsvorhaben GenerIC, unterstützt durch das Bundesministerium für Bildung und Forschung (BMBF) unter dem Förderkennzeichen 13FH051PX5.

Literatur

[1] Scheible, J.; Lienig, J.: Automation of Analog IC Layout – Challenges and Solutions. International Symposium on Physical Design (ISPD‘15), 29.03.–1.4.2015, Monterey, Kalifornien, USA, Konferenzband, S. 33–40, DOI: 10.1145/2717764.2717781.

[2] Marolt, D.: Layout Automation in Analog IC Design with Formalized and Nonformalized Expert Knowledge. Dissertation, Universität Stuttgart, 2019, https://elib.uni-stuttgart.de.

Die Autoren

Prof. Dr.-Ing. Jürgen Scheible

hat an der TH Karlsruhe (heute KIT) Elektrotechnik studiert und dort im Jahr 1991 mit

einer Arbeit im Bereich der Entwurfsautomatisierung zum Dr.-Ing. promoviert. Von 1992 bis 2010 arbeitete er bei Robert Bosch im Bereich Automobilelektronik in Reutlingen. Neben anderen Positionen war er dort als Gruppenleiter in der Vorentwicklung für die Entwurfswerkzeuge der IC-Entwicklung zuständig und leitete sieben Jahre die Abteilung für den IC-Layoutentwurf.

Seit 2010 lehrt und forscht er als Professor für Electronic Design Automation am Robert Bosch Zentrum für Leistungselektronik der Hochschule Reutlingen, wo er den Masterstudiengang Leistungs- und Mikroelektronik leitet. Sein Forschungsinteresse gilt der Automatisierung des Entwurfs analoger integrierter Schaltkreise.

juergen.scheible@reutlingen-university.de

Dr.-Ing. Daniel Marolt

wurde in Reutlingen geboren und studierte Mechatronik an der dortigen Hochschule, Abschlüsse B. Eng. 2008 und M. Sc. 2009. 2010 begann er als wissenschaftlicher Mitarbeiter an der Hochschule Reutlingen, wo er sich seit 2011 am Robert Bosch Zentrum für Leistungselektronik mit der Automatisierung des Schaltungs- und Layoutentwurfs analoger ICs beschäftigt.

2018 hat er an der Universität Stuttgart mit seinen Arbeiten zu SWARM zum Dr.-Ing. promoviert. Die Dissertation wurde dort mit dem Forschungspreis der Anton- und Klara-Röser-Stiftung ausgezeichnet.

daniel.marolt@reutlingen-university.de

Matthias Schweikardt, M. Sc.,

ist gebürtiger Reutlinger. Schweikardt studierte Elektro- und Informationstechnik – Bachelor und Master – an der Universität Stuttgart von 2011 bis 2016.

Seit 2017 ist er Doktorand beim Robert Bosch Zentrum für Leistungselektronik an der Hochschule Reutlingen und beschäftigt sich dort mit der Entwurfsautomatisierung des analogen IC-Entwurfs.

matthias.schweikardt@reutlingen-university.de

Dr.-Ing. Husni Habal

erhielt einen B.-Sc.-Abschluss in Informatik im Jahr 2001 und einen M.-Sc.-Abschluss in Elektro- und Informationstechnik im Jahr 2004 von der Oregon State University und den Grad Dr.-Ing. von der Technischen Universität München (TUM) im Jahr 2013. Anschließend forschte er als Postdoc am Institut für Electronic Design Automation der TUM bis 2016 an Alterungsmodellen von Transistoren zur numerischen Simulation und an Optimierung von analogen Schaltungen.

Derzeit beschäftigt er sich bei der Infineon Technologies AG mit der Entwicklung von analogen Schaltungen und dazugehörigen Verifikationsmethoden. Seine Hauptinteressen liegen im Bereich der Analog-IC-Entwicklung und der Analogsynthese.

husni.habal@infineon.com

- Automatisierung des Entwurfs analoger ICs – Teil 1

- Das Dilemma von Optimierungsalgorithmen