Check-Funktionen von EDA-Tools

Richtig verbunden – mit Stromversorgung und Masse

In der IC-Entwicklung sind Stromversorgungs- und Masseverbindungen entscheidend für die Funktionsfähigkeit der Komponenten. Soft-Checks helfen, um Verbindungsprobleme zwischen Diffusionsschichten und Substrat-Regionen (Well) im IC-Layout zu finden und zu lösen.

Zu den vielen Problemen, die bei der Stromversorgung und Masseverbindung auftreten können, gehören die Verbindungen zu den „Well“-Regionen eines IC-Entwurfs, die alle Hauptverbindungen zu den Komponenten mit Strom versorgen. Der Anschluss von Well-Regionen wird oft bis zu einem späteren Zeitpunkt im Entwicklungszyklus ignoriert. Aber bis dahin können andere Verbindungen Fehler in den Stromversorgungs- und Masseverbindungen verdecken. Die gebräuchlichste Methode zur Überprüfung dieser Verbindungen ist ein ERC (Electrical Rules Check), auch „Soft Check“ genannt. Der ERC-Soft-Check-Prozess bietet eine Methodik zur effizienten Lösung von Problemen mit dem Anschluss von Well-Regionen.

Jobangebote+ passend zum Thema

Festlegung der Verbindungen

In modernen IC-Entwürfen werden oft mehrere Spannungsversorgungen verwendet. Dies erhöht die Komplexität und macht die Überprüfung der Anschlüsse der Well-Regionen zu einem wichtigen Thema. Entwickler analoger ICs legen das Augenmerk oft mehr auf die Details der Beiträge, die die Well-Layer zur Funktion und Leistung des ICs leisten. Durch diese stärkere Fokussierung wird die Notwendigkeit einer genauen Definition dieser Verbindungen noch deutlicher. Außerdem wird jeder Aspekt des IC-Entwurfs durch die analogen Effekte stärker beeinflusst, wenn die Prozessgröße abnimmt.

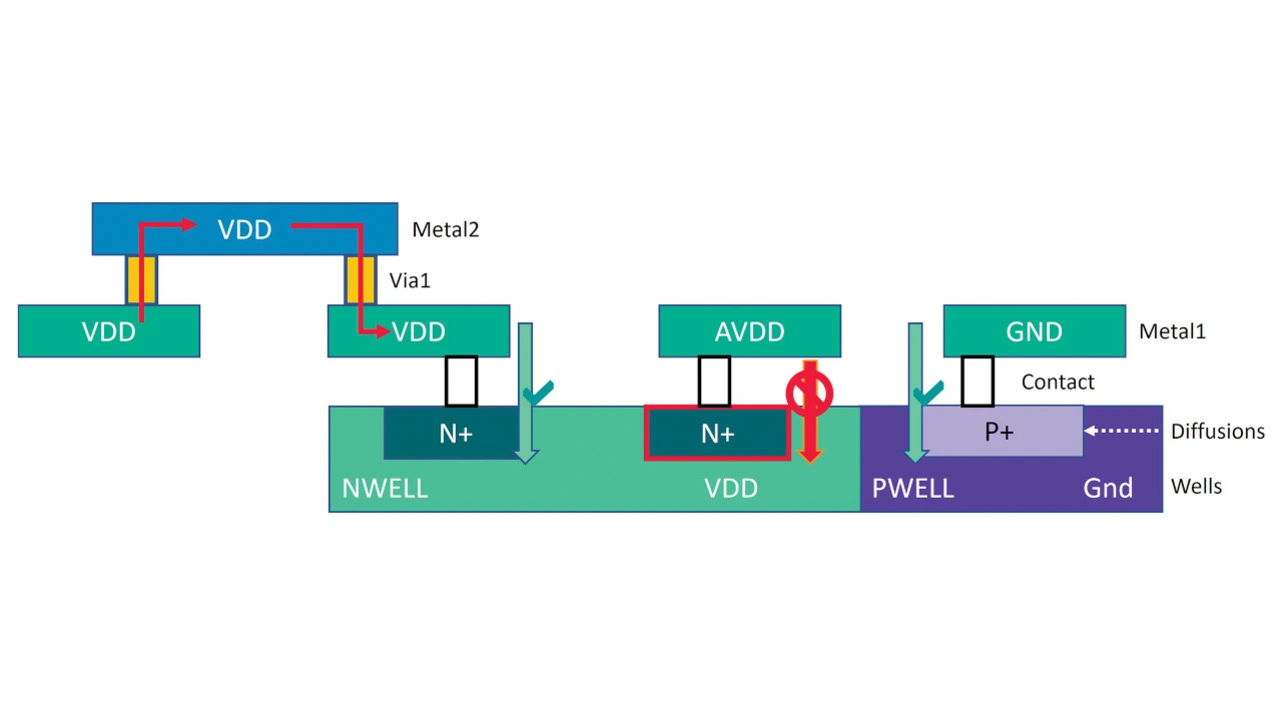

IC-Entwickler sollten Well-Layer nicht zur Leitung von Signalen verwenden, da sie eine geringere Dotierungskonzentration aufweisen als Diffusionsschichten. Es besteht eine umgekehrte Beziehung zwischen Dotierstoffdichte und Widerstand, was darauf hindeutet, dass Well-Layer mit einem höheren Widerstand modelliert werden als Diffusionsschichten. Dieses Attribut schreibt die Verwendung eines anderen Verbindungsschemas vor, um hochohmige Verbindungen zu vermeiden. Die als „Stamping“ bezeichnete einseitige Verbindungsfunktion verbindet die obere Schicht mit der unteren Schicht, ohne dass der Anschluss der unteren Schicht andere Polygone der oberen Schicht beeinträchtigen kann. Aus dieser einseitigen Verbindung können durch einen Soft Check kollidierende Formen ermittelt und gemeldet werden. Bild 1 zeigt einen Querschnitt von Verbindungsmaterialien und einen Verbindungsfehler zum Well-Layer, der durch einen Soft Check gemeldet würde.

Die Verbindung von den Diffusionsschichten zu den Well-Layern ist ein direkter, zweischichtiger Vorgang. Eine „N+“-implantierte Diffusion innerhalb einer „N–“-implantierten Well-Region leitet Strom. Ebenso leitet eine „P+“-implantierte Diffusion innerhalb einer „P–“-implantierten Well-Region Strom. Diese physikalische Realität erfordert, dass die Diffusionspolygone in ausgewählte Teilmengen aufgeteilt werden, um die Formen, die diese Verbindung definieren, genau anzuwenden.

Die Metallschicht, die sich am nächsten zu den Diffusionsformen des „Tap“ befindet, ist über eine Kontaktöffnungsschicht verbunden und liegt über der Diffusionsschicht. Die Metall- und Kontaktschichten sind nicht direkt an der Verbindung zur Well-Region beteiligt, sondern tragen zum Anschluss der Diffusionsschicht bei.

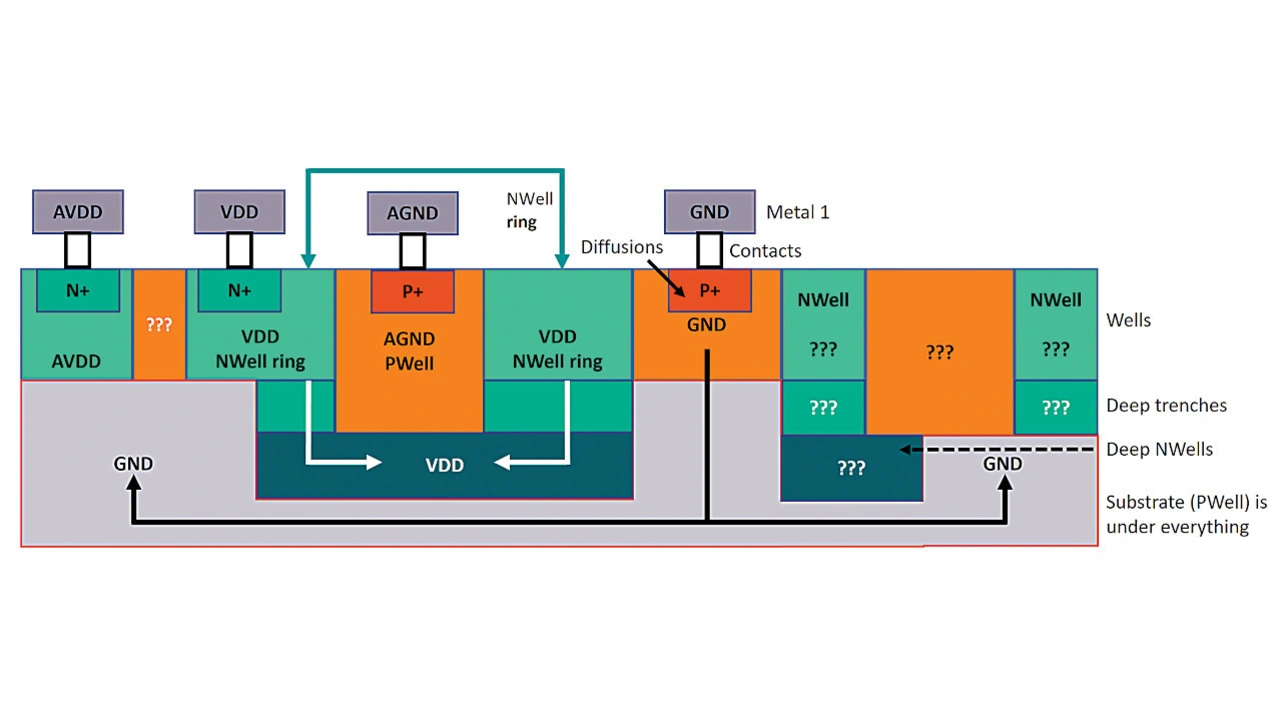

Bei der Entwicklung analoger ICs, bei denen der Anteil der Well-Layer im Vordergrund steht, kann die Verbindung unterhalb der Diffusionsschicht komplex sein. Die genaue Fertigstellung der erforderlichen Anschlüsse für diese IC-Entwürfe ist nicht einfach. Bild 2 veranschaulicht die komplexe Verbindungsführung eines analogen ICs.

Auch hier besteht eine direkte Verbindung zwischen Diffusionsschicht und Well-Region. Die Definition einer Verbindungsschicht ist in der Regel nicht erforderlich. Mehrere optionale Funktionen der Soft-Connection-Prüfungen im Calibre-nmLVS-Tool von Siemens EDA zum Beispiel können in komplexeren Situationen bei der Entwicklung analoger ICs nützlich sein [1].

Definition von Soft Checks

Die meisten Soft-Check-Definitionen sind Foundry-Regeln. Wenn ein IC-Entwurf jedoch über benutzerdefinierte Regeln verfügt, hat es sich bewährt, diese so präzise wie möglich zu halten. Dies erhöht die Robustheit und Effizienz der Soft-Connection-Definitionen und ihrer Verarbeitung.

Die Erkennung von Verbindungkonflikten wird durch One-Way- oder „Soft“-Connect-Definitionen in den Regeln ermöglicht. Darüber hinaus sind die entsprechenden Soft-Check-Anweisungen erforderlich, um festzulegen, für welche untere (Well-)Schichten Ergebnisse geliefert werden sollen. So gibt es beispielsweise in der Regel zwei Soft-Connection-Definitionen, eine für die NWELL-Schicht und eine für die PWELL-Schicht. Die Soft-Check-Definitionen basieren auf den Soft-Connection-Definitionen und melden die widersprüchlichen Formen.

Soft-Check-Berichte

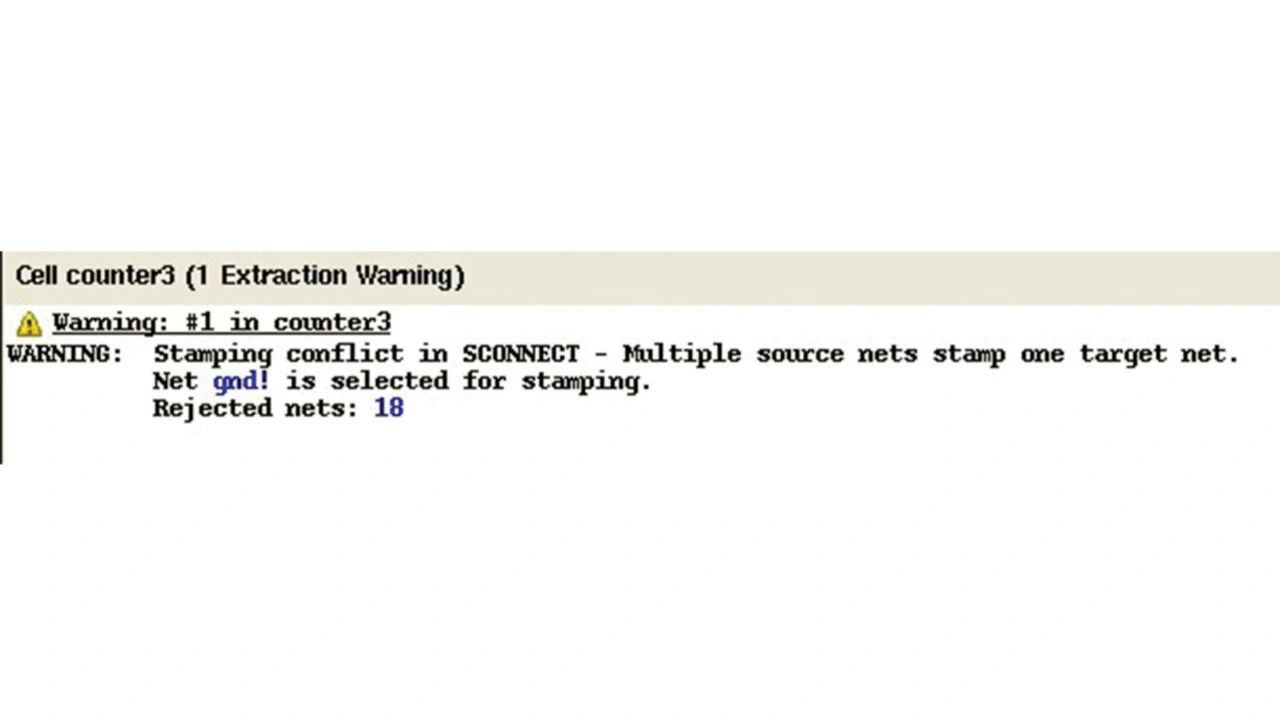

Bei Calibre beispielsweise führt das Vorhandensein der Soft-Connect-Anweisungen dazu, dass Stamping-Konflikte im Extraktionsbericht kurz und bündig gemeldet werden. Wenn die Option zum Melden von Soft Checks hinzugefügt wird, wird diese Meldung in der LVS-Berichtsdatei, der Extraktionsberichtsdatei und in Calibre RVE angezeigt – mit weiteren Details, wie in Bild 3 dargestellt.

Dieser erweiterte Bericht enthält den Namen des ausgewählten Netzes und den/die Namen oder Kennungen der abgelehnten Netze. In Calibre RVE sind diese Netznamen Hyperlinks, mit denen der IC-Entwickler diese Netze in einer Entwicklungsumgebung hervorheben kann.

- Richtig verbunden – mit Stromversorgung und Masse

- Soft-Check-Debugging

- Literatur