Check-Funktionen von EDA-Tools

Richtig verbunden – mit Stromversorgung und Masse

Fortsetzung des Artikels von Teil 1

Soft-Check-Debugging

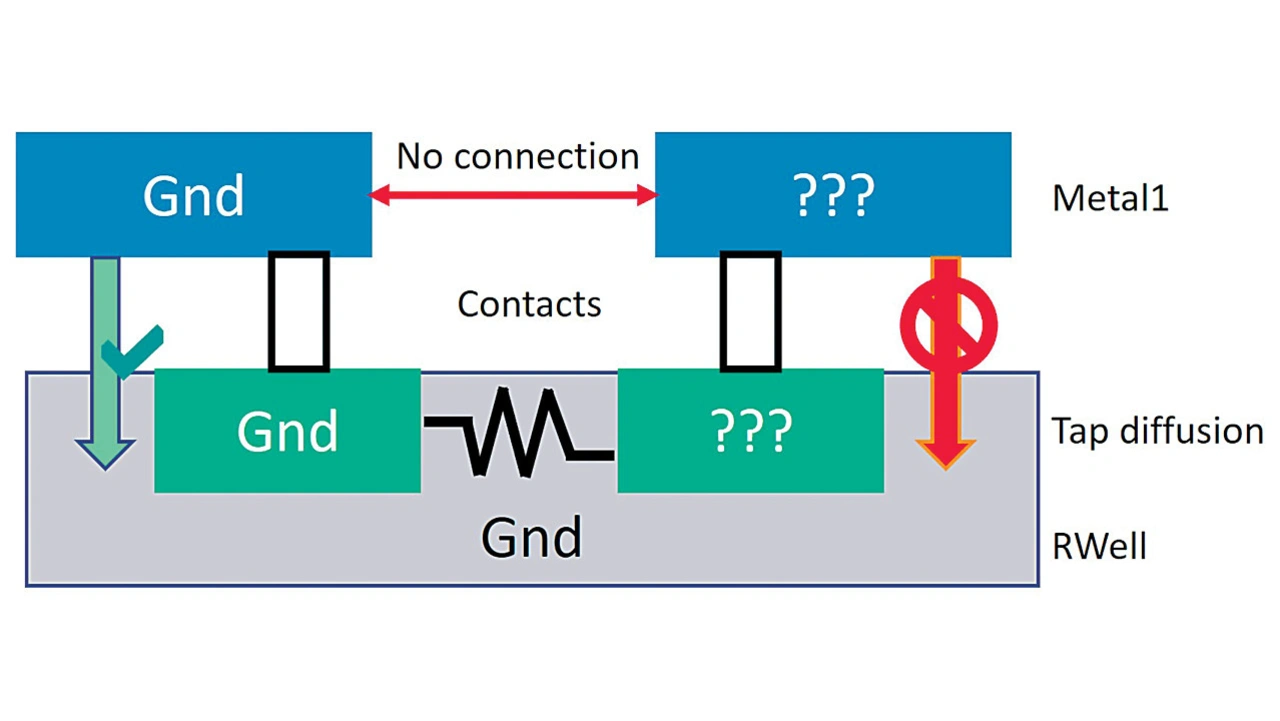

Um ein Soft-Check-Problem zu beheben, muss der Entwicklungsingenieur verstehen, was ein Soft Check meldet. Es gibt mehr als ein Netz – auf der oberen Schicht –, das versucht, auf die Form der unteren Schicht (Well) aufgebracht zu werden. Typischerweise wird dieses Problem durch ein offenes Netz in den Verbindungen der oberen Schichten verursacht. Bild 4 zeigt ein Beispiel für einen Soft-Check-Fehler der oberen Schicht.

In dem in Bild 4 gezeigten Beispiel wird durch die Verbindung der beiden Metall-1-Formen das obige Netz in ein einziges Netz aufgelöst und das Problem des Soft Check gelöst. Eine weitere mögliche, aber weniger häufige Ursache für Konflikte könnte ein falsch platzierter oder falsch beschrifteter Text sein.

Ein Aspekt, der bei der Fehlerbehebung von Soft-Check-Ergebnissen zu berücksichtigen ist, ist die Art der betroffenen Well-Layer. Versucht die widersprüchliche obere Diffusionsschicht, sich mit einer NWell- oder PWell-Schicht zu verbinden? In der Regel ist NWell eine gezeichnete Schicht, daher ist jede Insel von NWell isoliert und ein kleinerer Teil des Layouts. Ein kleinerer Bereich bedeutet in der Regel weniger mögliche Verbindungen und ist einfacher zu lösen. PWell wird in diesem Beispielverfahren als überall dort bestimmt, wo NWell nicht im gesamten IC-Entwurf zu finden ist. Da PWell typischerweise ein größerer Bereich ist, besteht mehr Potenzial für Verbindungen und damit für Konflikte.

Jobangebote+ passend zum Thema

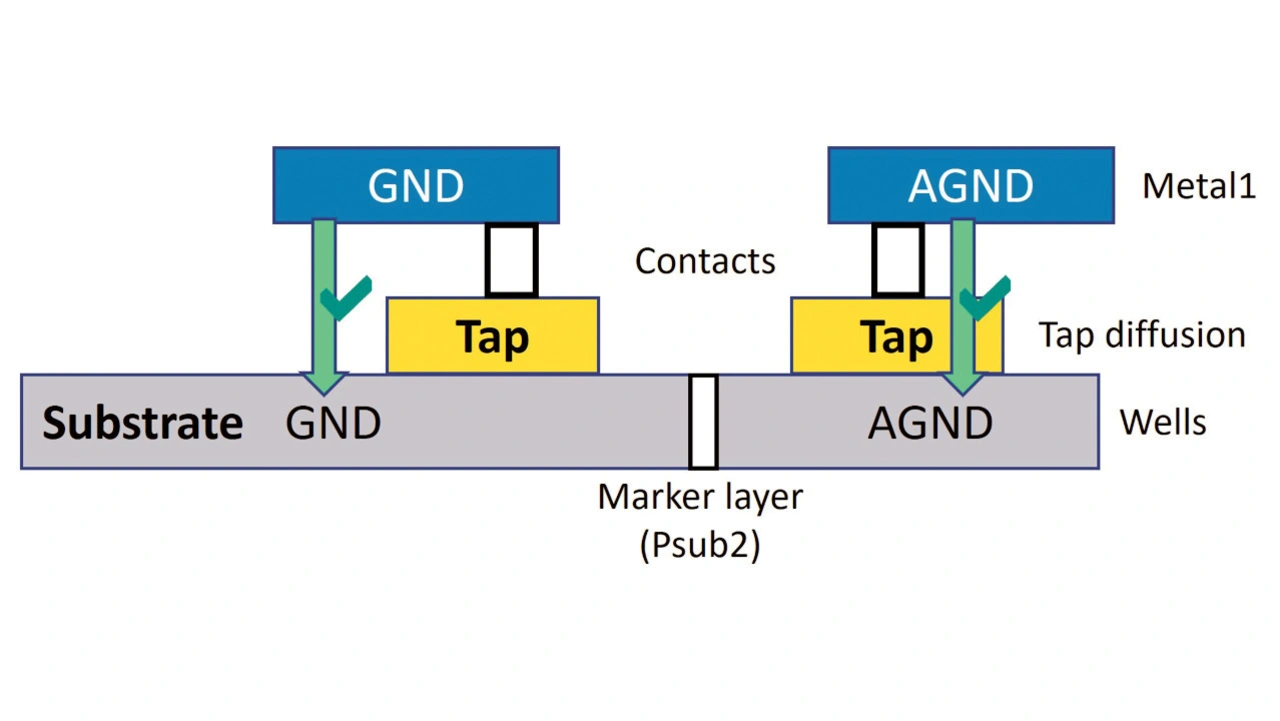

Wenn die Verbindung der oberen Schicht korrekt ist, liegt die Ursache für den Soft-Check-Fehler in einem Problem mit der Trennung der unteren Schicht. Bild 5 zeigt ein Beispiel für einen Soft-Check-Fehler der unteren Schicht.

Daher gibt es nur zwei Schritte, um herauszufinden, wie ein Soft-Check-Fehler zu beheben ist:

- Die Überprüfung der Verbindung der oberen Schicht.

- Wenn in Schritt 1 nichts gefunden wird, muss die Trennung der unteren Schicht untersucht werden.

Die Calibre-RVE-Ergebnisanzeige erleichtert diese Prüfung, wie in Bild 6 dargestellt.

Anhand des gemeldeten Fehlers lassen sich die Verbindungen des ausgewählten Netzes und der abgelehnten Netze untersuchen. Dazu muss der IC-Entwickler mit der rechten Maustaste auf die mit Hypertext versehenen Netznamen bzw. Kennungen klicken. Über ein Popup-Menü kann er das Fenster „Net Info“ für das interessierende Netz aufrufen.

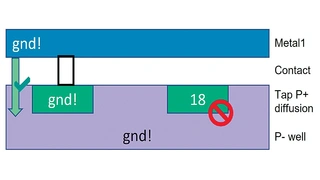

Das Fenster Netzinformationen zeigt, dass das abgelehnte Netz 18 nur eine einzelne Schicht (ptie) enthält. Dies ist ein Schnelltest, um festzustellen, ob die Verbindung zu den Materialien oberhalb der oberen Diffusions-Schicht fehlt.

Wie in der Liste der Schichten für das ausgewählte „gnd!“-Netz zu sehen ist, besteht eine Verbindung zu allen Materialien bis zu Metal 3. Zusätzlich steht die untere Well-Schicht (Psub) zur Hervorhebung zur Verfügung. Bild 7 zeigt eine Querschnittsdarstellung.

Die visuelle Anpassung der betrachteten Schichten bestätigt die Einschätzung für dieses einfache Beispiel. Bild 8 zeigt, dass dieser ptie-Form (Diffusion) der Kontakt fehlt, der sie mit den Schichten Metall 1 und darüber verbinden würde. Dies bestätigt, dass dieses Beispiel ein Problem mit dem Anschluss der oberen Schicht hat.

Ein weiteres Beispiel: Wenn die Verbindung der oberen Schicht korrekt hergestellt zu sein scheint, ist es an der Zeit, die Trennung der unteren Schicht auf Probleme zu untersuchen. Für die Analyse von Soft-Check-Problemen in der unteren Schicht gilt der gleiche Ansatz wie im vorherigen Fall.

Richtig verbunden – mit Stromversorgung und Masse Bilder 6-10

Im Netzinformationsfenster für die abgelehnten Netze (Bild 9) ist zu sehen, dass eine Verbindung durch die Materialien der oberen Schicht bis hin zu Metall 7 besteht.

Daher erscheint der Anschluss der oberen Schicht ausreichend. Wenn jedoch, wie in Bild 10 gezeigt, die oberen Diffusions-Formen mit der Isolierschicht der Well-Layer (hellbraun dargestellt) betrachtet werden, ist zu erkennen, dass einige der Formen der oberen Diffusions-Schicht innerhalb des Isolierbereichs eingeschlossen sind (in gelb) und die widersprüchlichen Formen nicht (grün dargestellt). Daher lässt sich ableiten, dass die widersprüchlichen Formen innerhalb eines Isolierbereichs der Well-Layer liegen müssen.

Diese Beispiele zeigen sehr einfache Fälle von Verbindungsproblemen, die mithilfe von Soft Checks gefunden werden können. Um die gemeldeten Soft-Check-Probleme eines IC-Entwurfs zu verstehen und zu lösen, sind Grundkenntnisse über die Definition der Regeln erforderlich. Werden vordefinierte Regeln verwendet, sind diese Beispiele gut geeignet, um zu zeigen, was diesen Anweisungen zugrunde liegt. Verfasser von physikalischen Prüfregeln können diese Informationen als Leitfaden für ihre Entwicklung verwenden.

Der Autor

Terry Meeks

ist Product Engineering Director für die Calibre-LVS-Anwendungen bei Siemens EDA, einem Teil von Siemens Digital Industries Software. Er arbeitet mit Kunden und Ingenieuren an der Entwicklung neuer und verbesserter EDA-Tools, um die wachsenden Herausforderungen in den Bereichen physikalische Verifikation, Schaltungsmodellierung und -analyse zu bewältigen. Meeks verfügt über mehr als 27 Jahre Erfahrung mit Calibre-Tools und ist seit mehr als 45 Jahren in der Branche tätig. Er hat einen Bachelor- und einen Master-Abschluss von der California State University in Fullerton.

terry.meeks@siemens.com

- Richtig verbunden – mit Stromversorgung und Masse

- Soft-Check-Debugging

- Literatur