Für IGBT- und SiC-MOSFET-Treiber

DC/DC-Wandler für robustere Leistungsstufen

Neben IGBTs werden in der Leistungselektronik für anspruchsvollere Aufgaben vermehrt SiC-MOSFETs eingesetzt. Beiden Transistortypen ist eines gemeinsam: Sie sollten optimal angesteuert und beschaltet werden, damit sie auch unter rauen Bedingungen über Jahre hinweg zuverlässig ihren Dienst tun.

Applikationen für IGBTs und SiC-MOSFETs finden sich in der gesamten Leistungselektronik – von Wechselrichtern in Wind- und Solaranlagen über Motorsteuerungen, Induktionsöfen, Schweißanlagen und vielem mehr bis hin zu Elektrofahrzeugen.

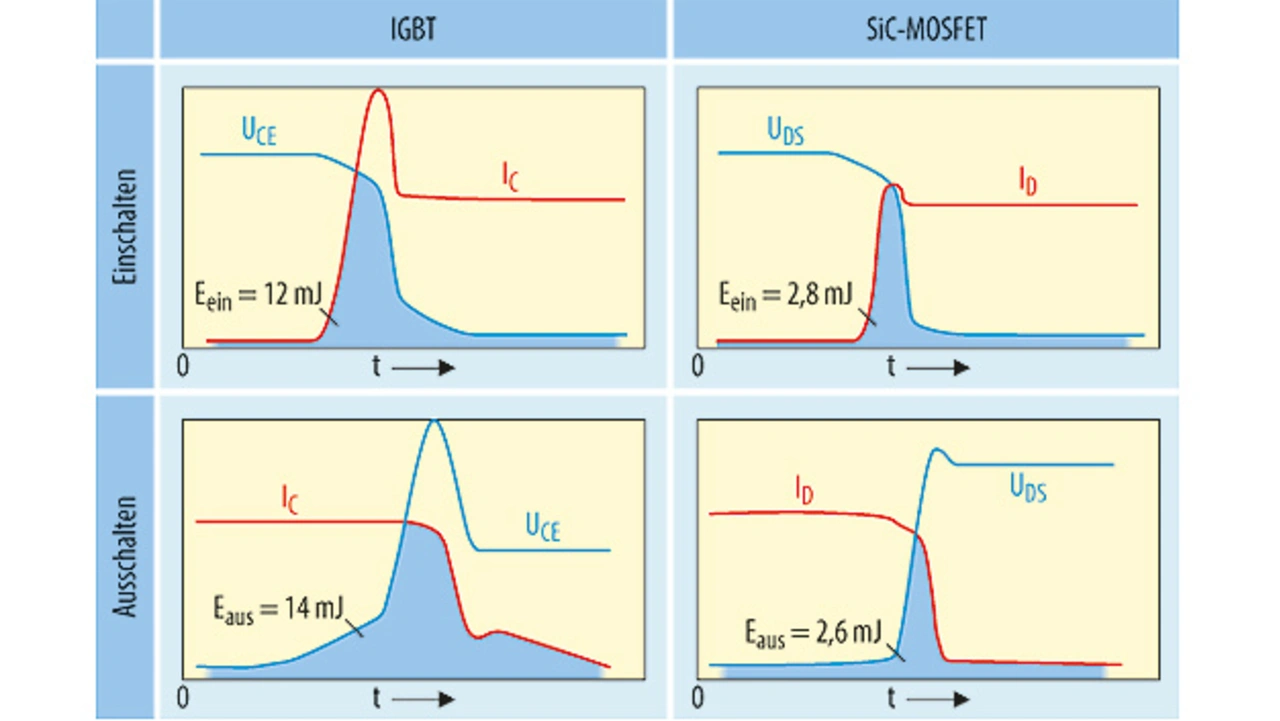

IGBTs sind aus monokristallinem Silizium gefertigt und gelten generell als preisgünstiger Standard-Leistungstransistor. Bei SiC-MOSFETs kommt Siliziumcarbid zum Einsatz, das höhere Sperrschichttemperaturen und dünnere Isolationsschichten am Gate erlaubt. Dies verbessert die thermische Leitfähigkeit und damit auch die Leistungsdichte. Die Schaltverluste von SiC-MOSFETs sind gegenüber IGBTs um mindestens Faktor vier geringer (Bild 1). Vor allem zeigt sich beim Ausschalten nicht der von IGBTs bekannte Schweifstrom (current tail) – ein Vorteil, besonders im oberen Leistungsbereich und bei höheren Schaltfrequenzen. So lässt sich durch den Einsatz von SiC-MOSFETs beispielsweise in Brückenschaltungen der Wirkungsgrad merklich erhöhen. Alternativ können durch Steigerung der Schaltfrequenz bei konstantem Wirkungsgrad Kosten und Gewicht bei den passiven Bauelementen eingespart werden, insbesondere bei Induktivitäten. Der höheren Kosten wegen werden SiC-MOSFETs bevorzugt für anspruchsvolle und hochwertige Schaltungen eingesetzt, wogegen Standard-Leistungsstufen, die in hoher Stückzahl produziert werden, von IGBTs dominiert werden.

Wie unerwünschtes Schalten unterbunden werden kann

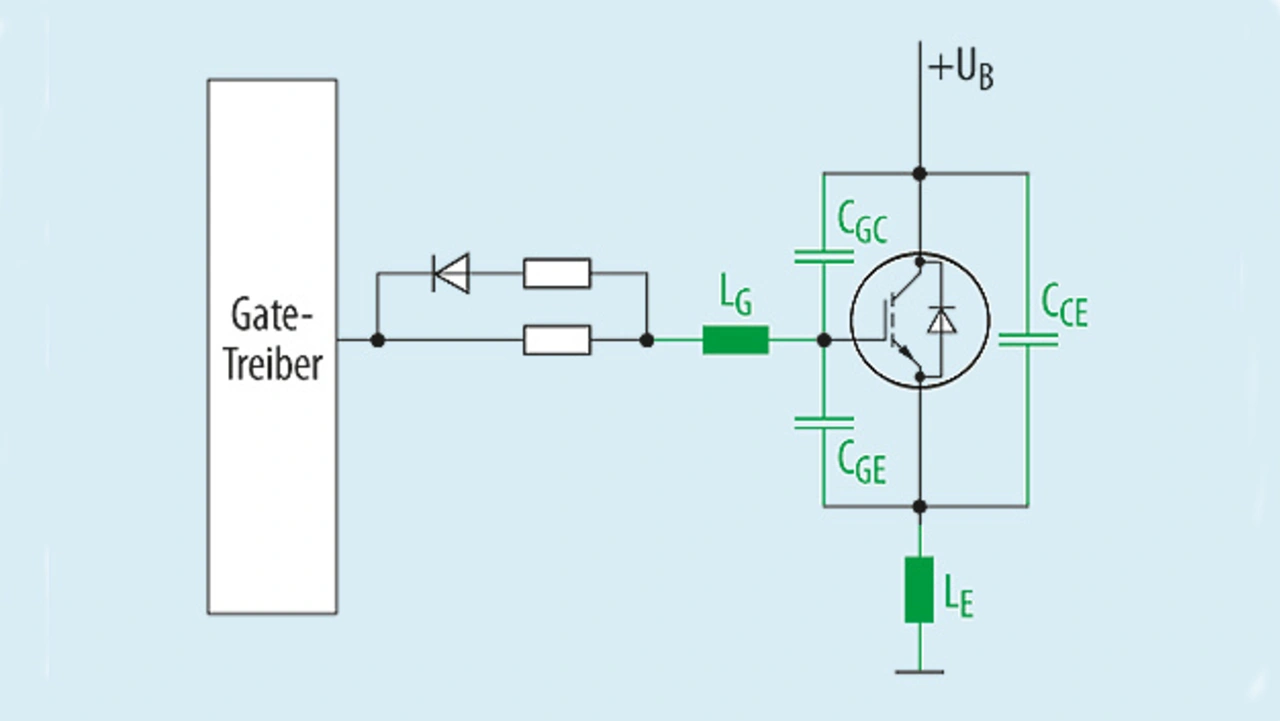

Bei der Beurteilung der Robustheit einer IGBT- oder SiC-MOSFET-Schaltung laufen Entwickler leicht Gefahr, sich zu sehr auf die Spezifikationen des Leistungstransistors zu konzentrieren und den Blick auf die Treiberstufe und das Schaltungslayout zu vernachlässigen. Denn wie so oft in der Analogtechnik steckt der Teufel im Detail – in parasitären Komponenten, die im Schaltplan nicht zu finden sind. Um zu verdeutlichen, womit sich der Entwickler in der Praxis auseinandersetzen muss, sind in Bild 2 die parasitären Kapazitäten und Induktivitäten, die rund um einen IGBT von Bedeutung sind, in grün eingezeichnet.

Die Leistungsstufe muss so dimensioniert werden, dass auch in extremen Situationen unter allen Betriebsbedingungen ein fehlerhaftes Einschalten eines Leistungstransistors vermieden wird. Käme es durch sporadisches Einschalten eines Leistungstransistors zu Kurzschlüssen – beispielsweise in einer Brückenschaltung – wären elektromagnetische Störsignale (EMI) und verminderte Lebenserwartung bis hin zur Zerstörung von Bauteilen die Folge.

Deshalb gilt es, die beiden wesentlichen Ursachen für unerwünschtes Einschalten in den Griff zu bekommen:

- 1. die Einflüsse parasitärer Kapazitäten wie Gate-Kollektor-Kapazität (CGC, Miller-Kapazität) und Gate-Emitter-Kapazität (CGE),

- 2. die Einflüsse parasitärer Induktivitäten wie Gate-Induktivität (LG) und Emitter-Induktivität (LE).

Parasitäre Kapazitäten

Steigt die Kollektor-Emitter-Spannung, weil der IGBT ausschaltet, muss CGC geladen werden. Der Ladestrom lässt sich grob nach folgender Formel abschätzen

Dabei ist zu beachten, dass der Wert von CGC nicht nur stark von der Spannung abhängig ist, sondern zusätzlich von der Temperatur und von der Stromstärke. Da diese Kapazität in den meisten Datenblättern nur unzureichend definiert ist, sind Messungen unter realen Bedingungen sinnvoll.

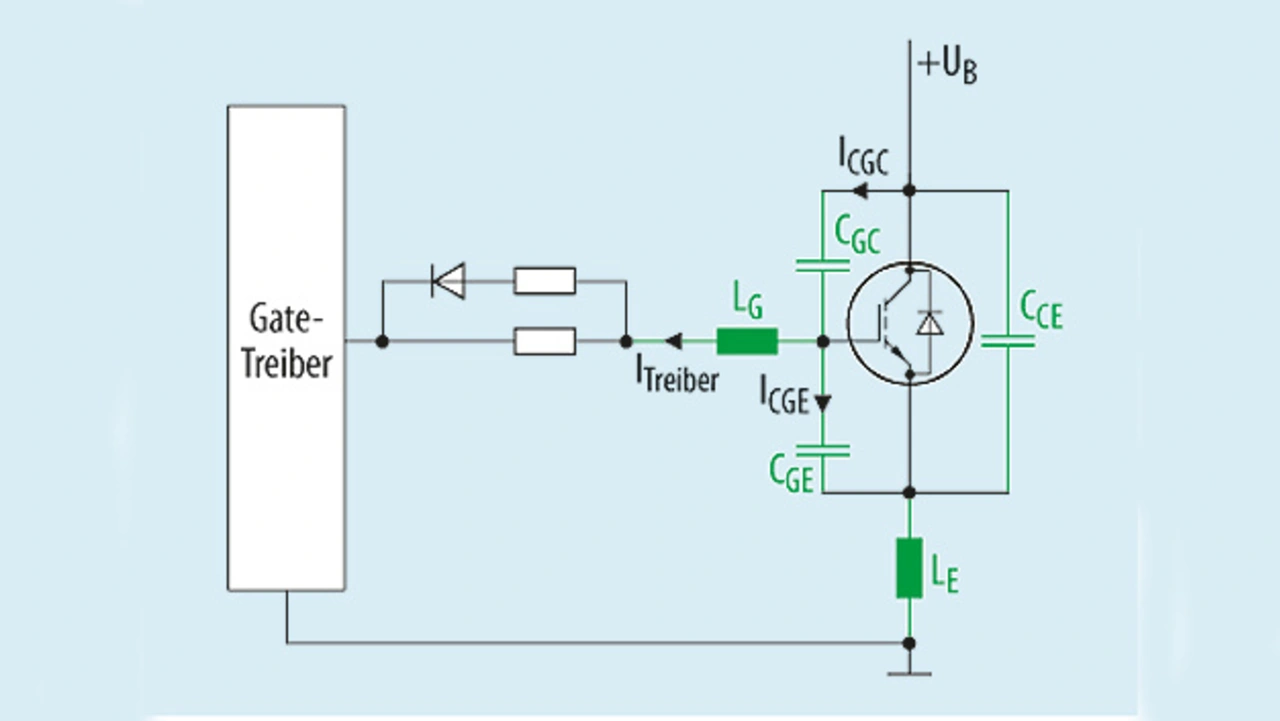

Das Laden der Miller-Kapazität CGC stellt noch nicht das eigentliche Problem dar. Ein Problem entsteht erst, wenn, bedingt durch den Ladestrom der Miller-Kapazität, die Eingangskapazität CGE so weit aufgeladen wird, dass die Schwellenspannung des IGBT erreicht oder gar überschritten wird (Bild 3).

Der Ladestrom von CGC kann dabei wie folgt definiert werden:

Der Treiberstrom (ITreiber) ist abhängig von den Gate-Widerständen und im dynamischen Betrieb von der Gate-Induktivität LG, die vom Schaltungslayout und vom Transistorgehäuse abhängt.

Um ein fehlerhaftes Einschalten, verursacht durch die Miller-Kapazität, zu verhindern, kann der Entwickler mehrere Ansätze wählen:

- Den Spannungsanstieg am Kollektor (dUCE/dt) begrenzen, um durch die geringere Flankensteilheit den Strom durch CGC (IC,GC)zu reduzieren. Als unerwünschte Nebenwirkung steigen allerdings die Schaltverluste.

- Verringern der parasitären Gate-Induktivität LG durch Optimierung des Schaltungslayouts, wodurch der Spannungsanstieg am Gate reduziert wird.

- Verwendung einer negativen Gate-Emitter-Spannung zum Sperren des Transistors, wodurch der Sicherheitsabstand zur Schwellenspannung erhöht wird.

Letzteres ist die elegantere Methode, da sie technisch einfach zu realisieren ist und die Verlustleistung nicht erhöht.

Parasitäre Induktivitäten

Im eingeschalteten Zustand fließt der Laststrom durch den Transistor und damit durch die Emitter-Induktivität. Wird dieser Stromfluss unterbrochen, entsteht an LE eine negative Spannung nach der Formel:

Die Spannung am Emitter wird also negativer als das Massepotenzial. Da das Gate aber über die Treiberstufe auf Masse gezogen wird, entsteht eine positive Gate-Emitter-Spannung. Wird dabei die Schwellenspannung überschritten, schaltet der Transistor fehlerhaft ein.

Bei Brückenschaltungen sind zusätzlich noch die parasitären Induktivitäten der anderen Brückenzweige und des Layouts zu berücksichtigen. Ist die Treiberschaltung nicht isoliert, hat die Verbindung der Masse-Anschlusspunkte – Masse der Leistungsstufe mit Masse der Treiberschaltung – zusätzlich einen erheblichen Einfluss auf die parasitären Induktivitäten und damit auf das Risiko eines fehlerhaften Einschaltens der Leistungstransistor-Brücke.

Was kann der Entwickler tun, um den Einfluss parasitärer Induktivitäten zu minimieren? Er könnte

- den Stromanstieg dI/dt reduzieren, da langsamere Stromabrisse die induzierte Spannung zwischen Gate und Emitter verringern. Allerdings erhöhen sich dadurch die Schaltverluste.

- die Leiterbahn-Induktivitäten durch optimiertes Schaltungslayout reduzieren. Je kürzer die Leiterbahnen, desto geringer die parasitäre Induktivität und desto niedriger auch die induzierten Spannungen.

- eine negative Gate-Emitter-Spannung zum Sperren der Transistoren verwenden. Dadurch erhöht sich der Sicherheitsabstand zur Schwellenspannung.

- die Treiberschaltung galvanisch von der Leistungsstufe trennen und zur Versorgung der Treiberstufe galvanisch isolierende DC/DC-Wandler verwenden. Wird der Masseanschluss der Treiber-Stromversorgung direkt am jeweiligen Emitter des Leistungstransistors angeschlossen, werden die Einflüsse der Layout-Induktivitäten weitestgehend eliminiert.

- IGBTs mit zweitem, separatem Emitter-Anschluss (Kelvin-Kontakt) für die Treiberschaltung verwenden. Zwar hat auch dieser zweite Emitter-Anschluss eine parasitäre Induktivität, die wird aber nicht vom Laststrom durchflossen und ist deshalb vernachlässigbar

- DC/DC-Wandler für robustere Leistungsstufen

- Lässt sich die Robustheit einer Schaltung messtechnisch erfassen?