Neue MOSFET-Technologie

Schnelles, homogenes Ein- und Ausschalten

Leistungs-MOSFETs der jüngsten OptiMOS-Technologie von Infineon bieten Verbesserungen bei allen wichtigen Parametern. Ihr Design verbindet ein dreidimensionales Ladungskompensationsprinzip mit einem Gate-Gitter und realisiert damit eine sehr gute Homogenität des Schaltverhaltens über dem Chip.

MOSFETs sind ausgezeichnete Schalter für viele verschiedene Anwendungen mit unterschiedlichsten Anforderungen, darunter Leistungsmanagement-Schaltungen und Motorantriebe. Insbesondere die Einführung vertikal diffundierter MOSFET-Strukturen mit einem lateral an der Oberfläche verlaufendem Kanal lieferte eine interessante Alternative zu bipolaren Technologien. Allerdings schränkte der hohe Durchlasswiderstand die Strombelastbarkeit dieser Bauteile und damit ihren Einsatz in leistungselektronischen Anwendungen ein.

Einen Meilenstein für den breiten Einsatz von Feldeffekttransistoren in der Leistungselektronik stellte die Einführung der ersten Trench-Gate-MOSFETs dar. Durch den jetzt vertikal verlaufenden Kanal wurde der den Stromfluss einschnürende JFET-Bereich quasi beseitigt. Zudem erhöhte sich durch Fortschritte in der Fertigungstechnologie die Zelldichte und damit die Kanalweite. Beides zusammen führte zu immer niedrigeren Durchlasswiderständen. Aber die höhere Zelldichte brachte auch Nachteile mit sich, da sowohl die Gate-Drain- als auch die Gate-Source-Kapazität linear mit der Anzahl der Trenches, also mit der Zelldichte, ansteigen.

Warum ist dies ein Problem? Ein MOSFET wird ausschließlich über seinen Gate-Anschluss gesteuert. Aus diesem Grund muss die Gate-Treiberschaltung die gesamte Gate-Ladung (QG) bereitstellen, die zum Einschalten des Transistors erforderlich ist. Bei Anwendungen mit hoher Schaltfrequenz, wie beispielsweise in Schaltnetzteilen, ist eine möglichst geringe Gate-Ladung wünschenswert, um die Treiberverluste zu reduzieren. Größere Gate-Drain-Ladungen (QGD) wirken sich dagegen auf die Einschaltgeschwindigkeit aus, was zu erhöhten Schaltverlusten führt und längere Totzeiten zur Folge hat.

Optimierte Leistungswerte durch neue Strukturen

Den Beginn einer neue Ära markierte die Einführung von ladungskompensierten Strukturen, welche das gleiche Prinzip wie Superjunction-MOSFETs nutzen. Dabei verwendeten die ersten Bauteile dieser Art eine isolierte tiefe Feldplatte als Verlängerung des Gates. Dadurch wurde eine laterale Verarmung des Driftbereichs im ausgeschalteten Zustand ermöglicht, was eine höhere Dotierung des Driftgebiets erlaubt und damit zu einer klaren Reduktion des Durchlasswiderstandes führte. Doch erst durch die Isolation der Feldplatte vom Gate, und deren Verbindung mit der Source, konnten Bauteile mit deutlich verringerten Gate- und Gate-Drain-Ladungen umgesetzt werden. Neben einer hohen Schaltgeschwindigkeit zeichnen sich diese Bauteile auch durch eine hohe Robustheit aus und entwickelten sich schließlich zum Industriestandard.

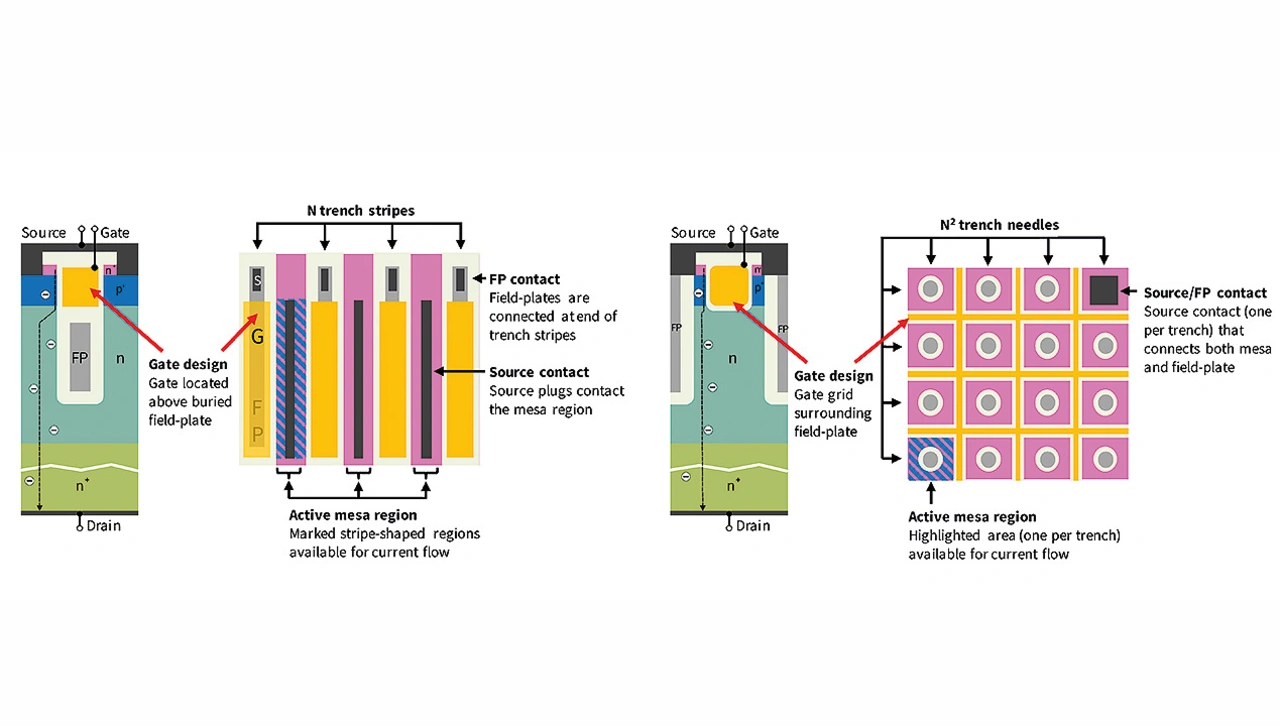

Üblicherweise kombinieren diese Bauelementstrukturen eine isolierte Feldplatte in einem tiefen Trench, welche von der darüber liegenden Gate-Elektrode getrennt ist, mit einem Streifen-Layout (Bild 1, links). In der neuesten Generation dagegen wird der Feldplatten-Trench, der jetzt eine nadelförmige Struktur bildet, vom Gate Trench getrennt. Dieser bildet nun ein Gitter, welches die Nadeln umgibt (Bild 1, rechts). Auf diese Weise kann die für die Stromleitung verfügbare Siliziumfläche vergrößert und der Gesamtwiderstand im eingeschalteten Zustand erneut verringert werden.

Damit die dynamischen Kennwerte FOMG = RDS(on) × QG (Figure of Merit) und FOMGD = RDS(on) × QGD noch weiter reduziert werden können, musste der Gate-Trench komplett neu gestaltet und vor allem seine laterale Ausdehnung minimiert werden. Keine leichte Aufgabe, da das üblicherweise als Gate-Material verwendete Polysilizium bei den resultierenden kleinen Dimensionen zu einem stark ansteigenden internen Gate-Widerstand führt. Mit üblicherweise verwendeten Gate-Fingern kann die Länge der Gate-Elemente jedoch verkürzt und damit der Gesamtwiderstand des verteilten Gates reduziert werden. Derartige Fingerstrukturen haben jedoch einen großen Platzbedarf, was dazu führt, dass sich der Einschaltwiderstand des Chips wieder erhöht. Um dies zu vermeiden, wurde ein Metall-Gate-System eingeführt. Damit ist es möglich, nicht nur den internen Gate-Widerstand zu verringern, sondern gleichzeitig auch die Verteilung des Gate-Widerstands auf dem Chip zu verbessern.

Zusammen mit der direkten Verbindung der Feldplatten zur Source-Metallisierung des Transistors ergibt sich ein vollkommen neuer Aufbau des Bauteils, welcher ein sehr schnelles und homogenes Ein- und Ausschalten ermöglicht. Dadurch lassen sich sowohl die Schaltverluste senken als auch das Risiko eines unerwünschten, dv/dt-induzierten parasitären Einschaltens des MOSFETs verringern. Die direkte Verbindung der Feldplatten zur Source beseitigt auch nahezu vollständig den internen Serienwiderstand zur Ausgangskapazität, wodurch damit verbundene Leitungsverluste beim Laden und Entladen der Ausgangskapazität während des Schaltens minimiert werden.

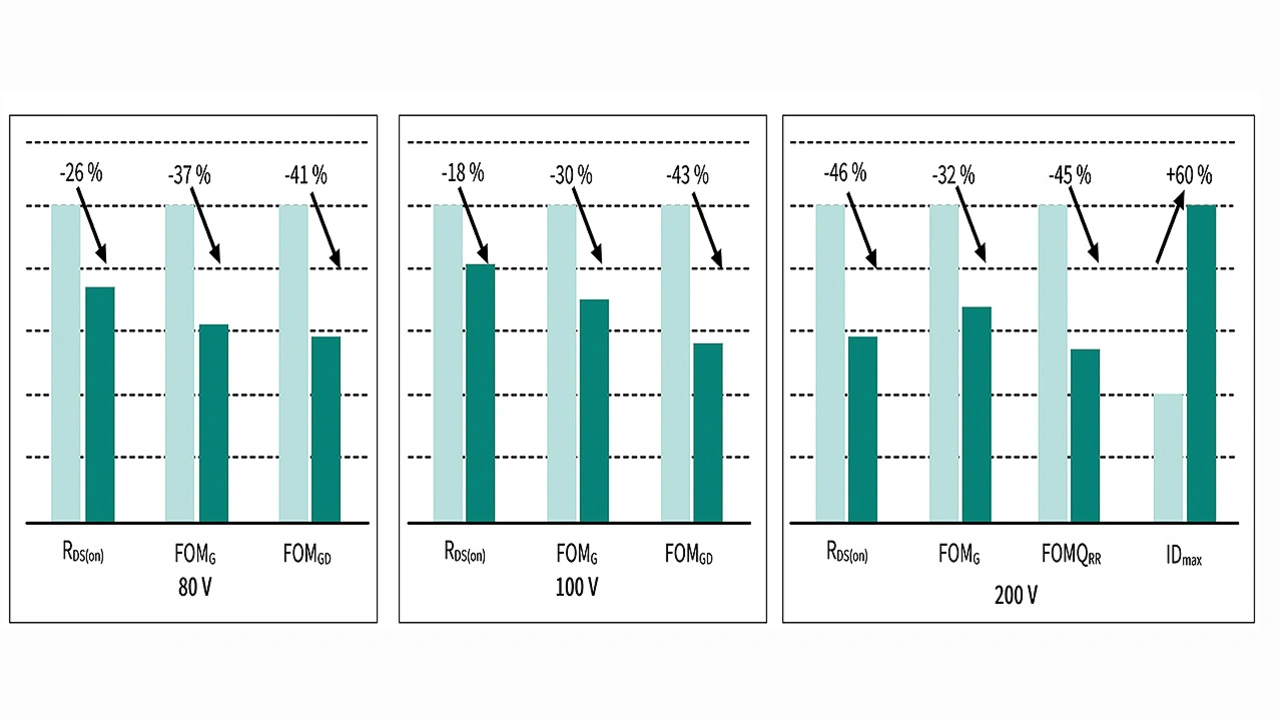

Bild 2 gibt einen Überblick über die Verbesserung der Bauteilparameter für verschiedene Spannungsklassen gegenüber der Vorgängertechnologie. Mit der Reduktion der FOMG verbessert sich die Effizienz insbesondere bei geringer Last, da hier die Ansteuerverluste reduziert werden. Dies ist insbesondere für Schaltnetzteile mit hohen Schaltfrequenzen, aber auch bei Motorantrieben mit vielen parallel geschalteten MOSFETs von Vorteil.

Bei der neuen 200-V-Technologie konnte gegenüber der Vorgängergeneration außerdem die Reverse-Recovery-Ladung deutlich reduziert werden. Dies ist wichtig, um auch hier die Schaltverluste zu senken, das EMI-Verhalten zu verbessern und eine hohe Kommutierungsfestigkeit zu ermöglichen.

- Schnelles, homogenes Ein- und Ausschalten

- Anwendung in der TK- und IT-Stromversorgung