Effiziente DC-DC-Wandler

Mehr Power für KI

Fortsetzung des Artikels von Teil 1

Treiberstufe auf Punktgröße verkleinern

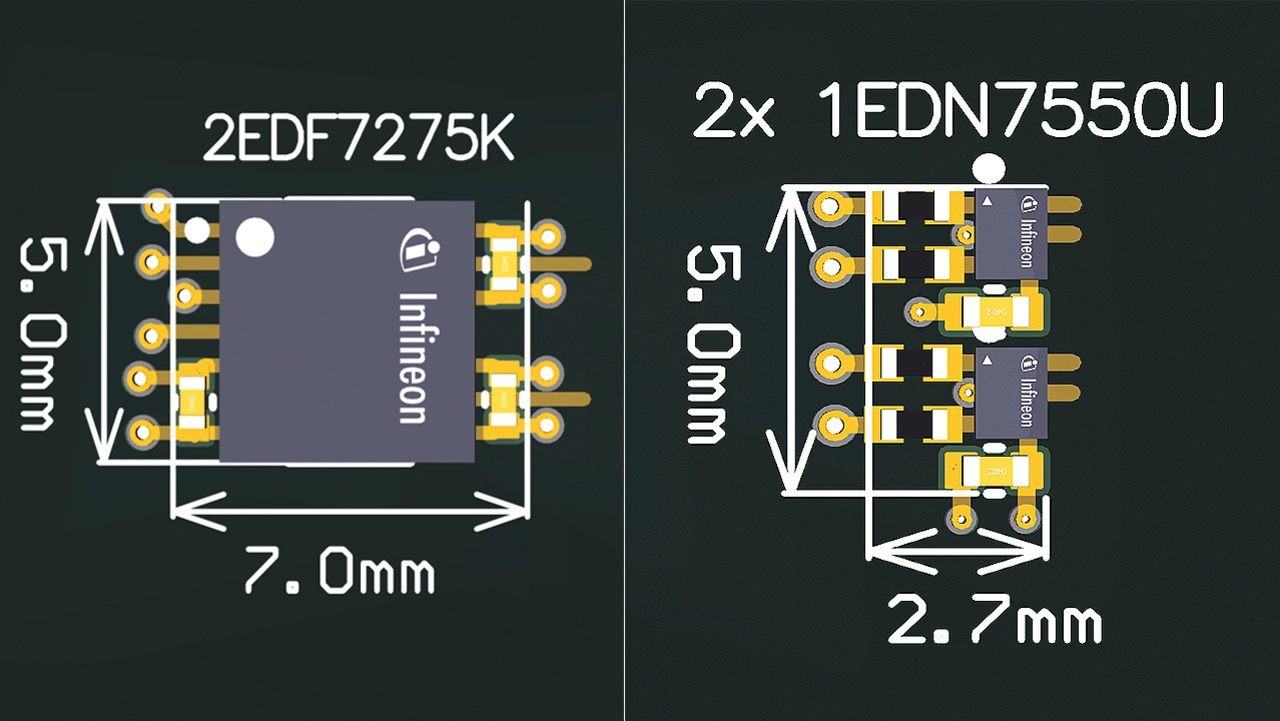

Ein Flächenvergleich zwischen dem isolierten zweikanaligen Baustein 2EDF7275K und dem einkanaligen 1EDN7550U verdeutlicht die Platzvorteile von TSNP-Gehäusen auf Systemebene. Beide Bausteine können die High-Side-Schalter in der HSC-Topologie ansteuern. Die Schalter Q1, Q2, Q4 und Q5 können entweder mit zwei isolierten Zweikanaltreibern wie dem 2EDF7275K oder mit vier nicht isolierten Einkanal-TDI-Treibern wie dem 1EDN7550U betrieben werden.

Die für zwei Schalter erforderliche Treiberfläche beträgt insgesamt 35 mm² für einen 2EDF7275K einschließlich aller passiven Bauelemente und 13,5 mm² für zwei 1EDN7550U einschließlich aller passiven Bauelemente und Eingangswiderstände. Damit halbiert sich die Fläche der Treiberstufe mit dem 1EDN7550U. Zudem lassen sich sowohl das Layout als auch die Anordnung der Transformatoren und die Wärmeableitung in DC-DC-Wandlern mit hoher Leistungsdichte verbessern (Bild 7).

Da es sich bei dem 1EDN7550U um einen einkanaligen Baustein handelt, lassen sie sich in diesem Fall flexibler platzieren. Für den Entwickler ergibt sich dadurch ein weiterer Freiheitsgrad, wobei die Hardware anschließend entsprechend der Flächenbelegung, der Treiberschleife oder beidem optimiert werden kann.

Chipgehäuse mit geringem Wärmewiderstand

In vielen Stromversorgungsdesigns werden die inneren Kupferschichten der Leiterplatte verwendet, um die Wärme von den Leistungs-MOSFETs abzuleiten und den Temperaturanstieg in der Leistungsstufe zu mindern. Das gilt insbesondere für die Masseflächen, wenn zur Synchrongleichrichtung Source-down-MOSFETs wie der IQE006NE2LM5CG aus der OptiMOS-Familie von Infineon verwendet werden.

Von dieser weit verbreiteten Technik der Temperaturverteilung profitiert das gesamte System, da die Zuverlässigkeit und der Gesamtwirkungsgrad steigen. Allerdings erhöht sich dadurch die Temperatur der Kupferebenen, bei der es sich um die Referenz-temperatur der Leiterplatte sowohl für die Leistungs-MOSFETs als auch für die Gate-Treiber handelt.

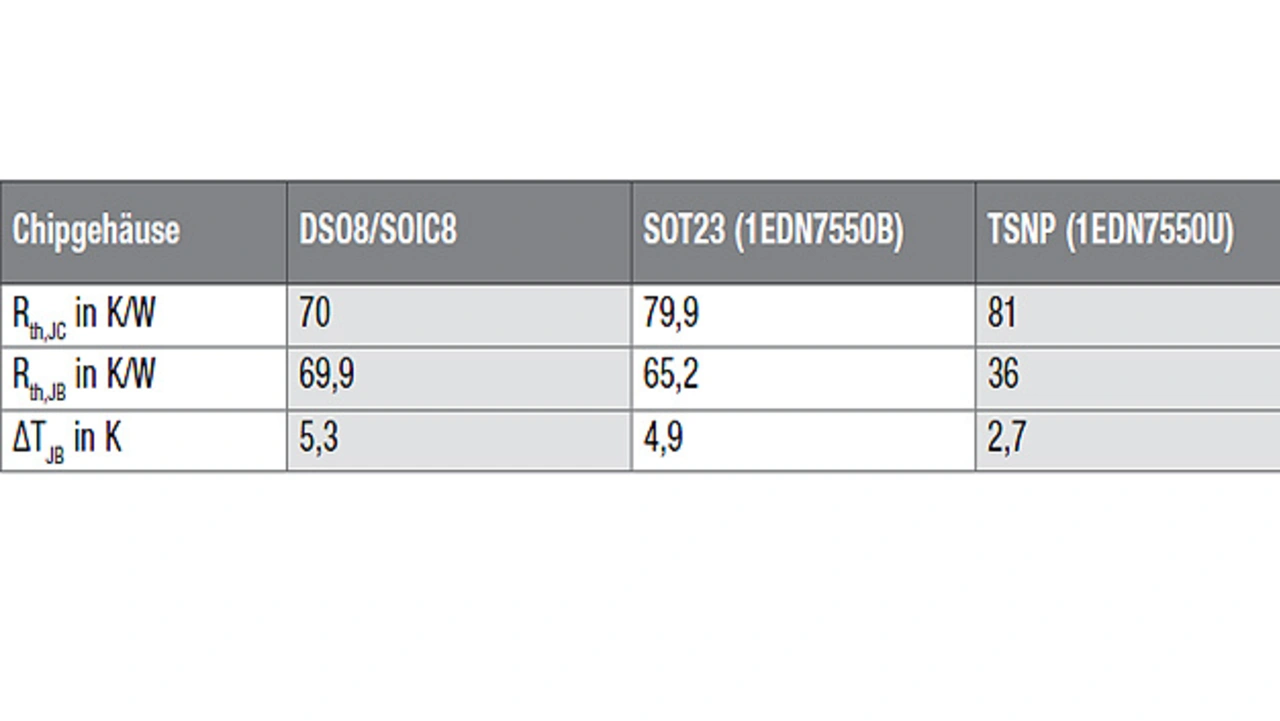

Um eine niedrige Sperrschichttemperatur TJ für die Gate-Treiber-ICs zu erreichen, muss der thermische Widerstand zwischen Sperrschicht und Leiterplatte Rth,JB möglichst niedrig sein, um eine möglichst niedrige Temperaturdifferenz zur Platine ΔTJB zu erreichen. Dies gelingt durch die hohe thermische Performance des TSNP-Gehäuses (Tabelle 2).

Fazit

Das Gate-Treiber-IC 1EDN7550U der EiceDRIVER-Familie von Infineon bietet in Kombination mit dem Source-down-MOSFET IQE006NE2LM5CG aus der OptiMOS-Familie eine zuverlässige Lösung für HSC-HD-Wandler mit ultrahoher Leistungsdichte.

Durch Kombinieren von High-Side-Treibern, einer hohen thermischen Performance, einer niederohmigen Ausgangsstufe und einem kleinen Gehäuse ist es möglich, die Fläche der Treiberschaltung zu reduzieren. Gleichzeitig lässt sich die elektrische Performance von DC-DC-Wandlern mit ultrahoher Leistungsdichte für Rechenzentren und Computer-anwendungen der künstlichen Intelligenz (KI) verbessern.

Die Autoren

Antonello Laneve

arbeitet seit 2020 für Infineon und ist derzeit als Staff System Application Engineer für isolierte IC-Produkte tätig. Laneve erwarb 2012 einen Bachelor in Elektronik- und Telekommunikationstechnik an der Polytechnischen Universität Bari und 2016 einen Master in Elektrotechnik an der Polytechnischen Universität Turin

Dr. Roberto Rizzolatti

ist seit 2018 als System Innovation Engineer bei Infineon tätig und leitet derzeit das Team des »Innovation Lab for Power Systems and Integration«. Rizzolatti studierte Elektrotechnik an der Universität Udine, Italien, wo er sowohl den Bachelor als auch den Master erwarb. Anschließend promovierte er in Wirtschaftsingenieurwesen und Informationstechnik. Rizzolatti hält mehrere Patente im Zusammenhang mit der 48-V-Data-Center-Architektur

- Mehr Power für KI

- Treiberstufe auf Punktgröße verkleinern