Effiziente DC-DC-Wandler

Mehr Power für KI

In Rechenzentren ist künstliche Intelligenz (KI) auf dem Vormarsch. Dadurch steigen die Leistungsanforderungen des Systems, während der Platz für die Stromversorgung gleich bleibt. Eine mögliche Lösung sind Hybrid-Switched-Capacitor-Wandler und spezielle Gate-Treiber-ICs.

Die Entwicklung KI-fähiger Computer für Rechenzentren birgt eine große Herausforderung: Zwar steigt die Rechenleistung, doch das Platzangebot für die Stromversorgungen bleibt unverändert. Aufgrund der hohen Leistungsanforderungen überschreiten die Leistungsstufen von Serverschränken (Racks) den 30-kW-Bereich. Das Open Compute Project (OCP) will diese Hürde überwinden, indem es neue Standards auf der Ebene der Stromversorgungsarchitektur definiert und auf Rack-Ebene von der bisherigen 12-V-Stromverteilung auf 48 V migriert. Bei diesen Spannungsbereichen ist eine galvanische Trennung nicht notwendig, weshalb neue DC-DC-Wandlertopologien und -Bausteine erforscht werden.

Heutige 48-V-Stromversorgungsarchitekturen nutzen üblicherweise einen zweistufigen Ansatz, um sowohl die Anforderungen an ein hohes Übersetzungsverhältnis als auch an das Einschwingverhalten zu erfüllen. Als erste Stufe kommt typischerweise ein Zwischenbuswandler (Intermediate Bus Converter, IBC) mit festem Wandlungsverhältnis zum Einsatz und als zweite Stufe ein Spannungsregelungsmodul (Voltage Regulation Module, VRM), das als mehrphasiger Tiefsetzsteller (Buck Converter) die Spannung genau regelt.

Auf einer herkömmlichen KI-Beschleunigerkarte für Rechenzentren und Computeranwendungen ist die verfügbare Grundfläche für beide Wandlerstufen begrenzt. Daher müssen beide mit hoher Schaltfrequenz laufen, damit die passiven Komponenten kleiner ausfallen können. Hohe Schaltfrequenzen in der VRM-Stufe würden jedoch zu hohen Verlusten führen, unter anderem zu erhöhten Schalt-, Treiber-, Kern- und Leitverlusten. Um die volle Systemeffizienz und Leistungsdichte zu erhalten, ist daher ein DCX-Wandler mit hohem Übersetzungsverhältnis erforderlich.

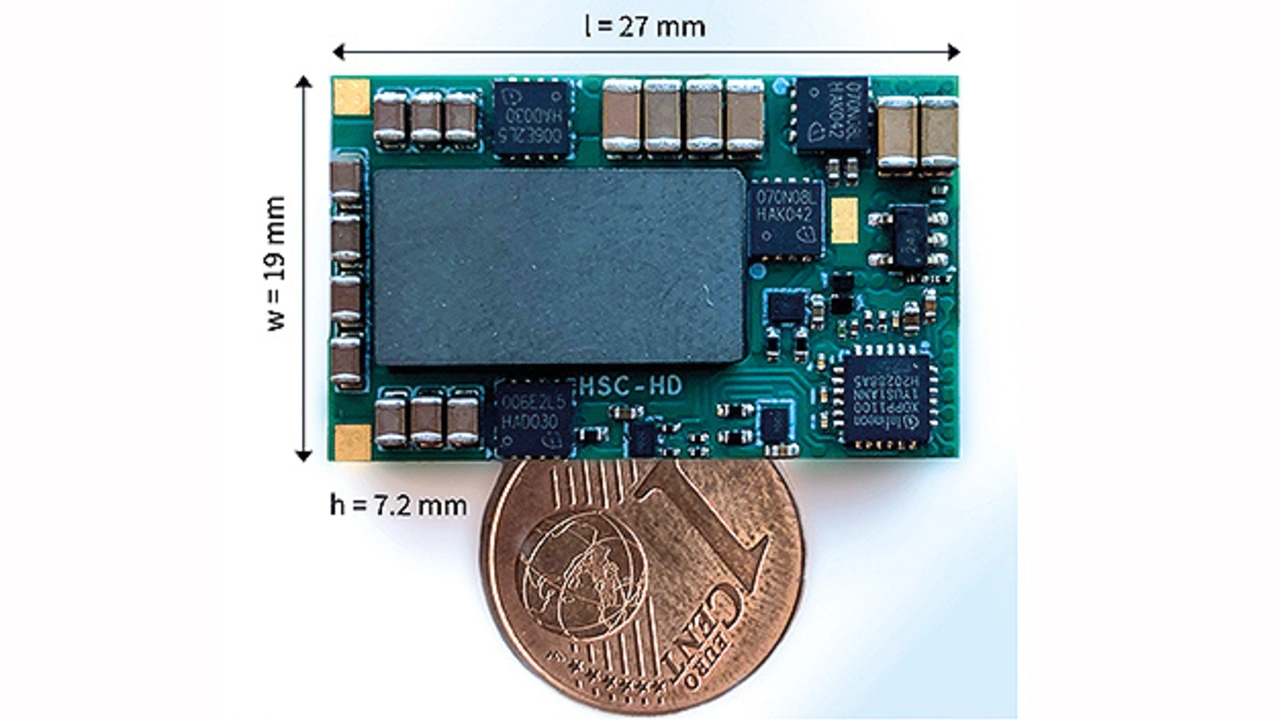

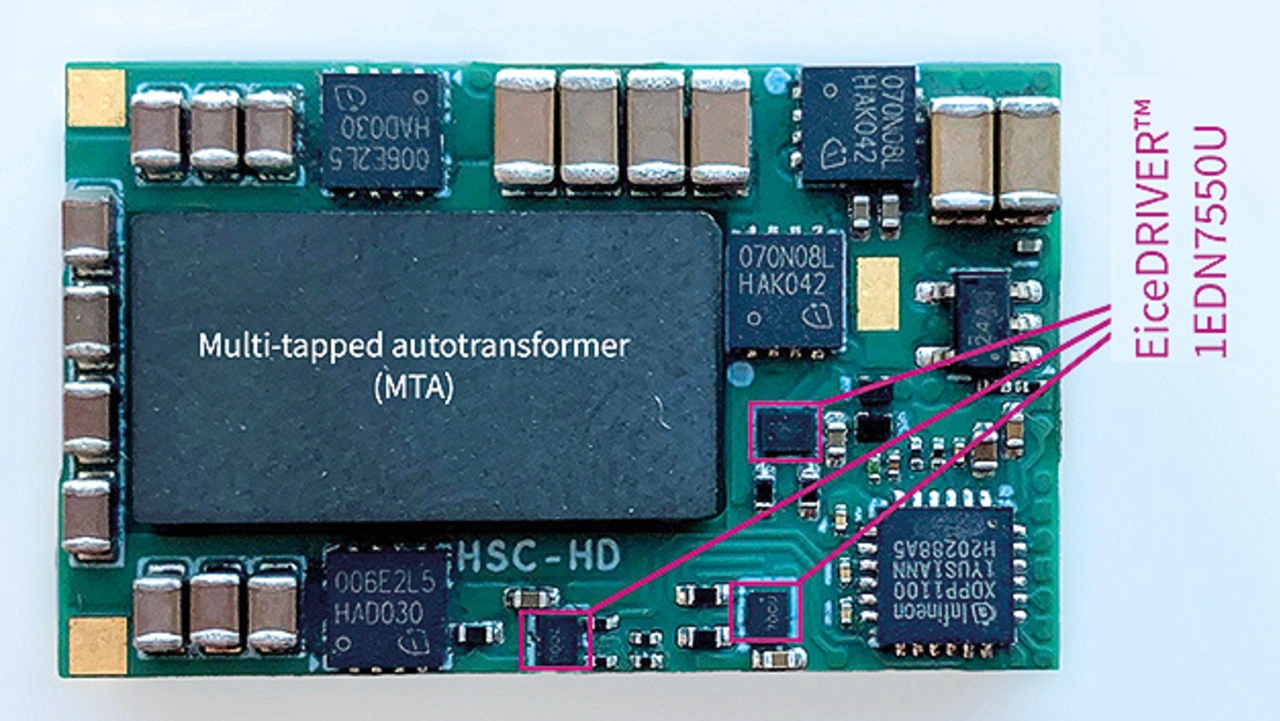

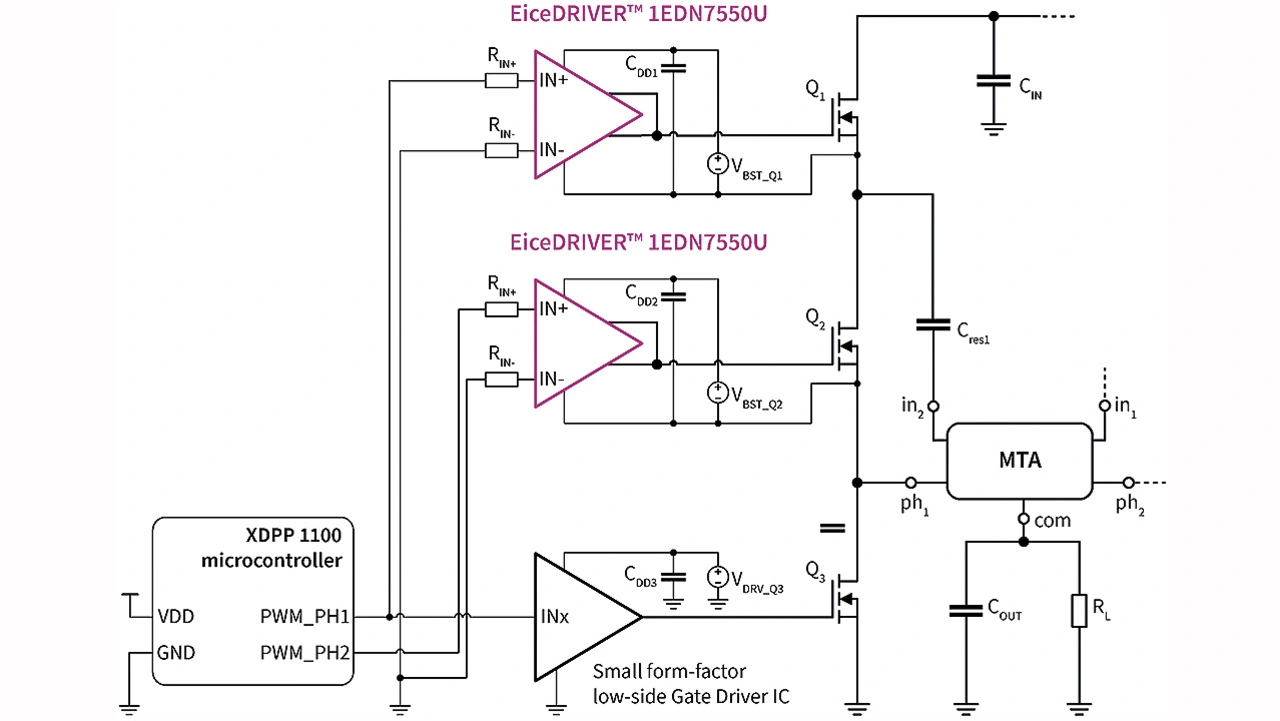

Dafür hat Infineon vor Kurzem einen HSC-Wandler (Hybrid Switched Capacitor) vorgestellt (Bild 1). Dieser kombiniert die Vorteile eines nicht isolierten Wandlers mit der Fähigkeit, die großen Übersetzungsverhältnisse eines Auto-Transformators mit Mehrfachabgriff (Multi-Tapped Autotransformator, MTA) bereitzustellen. Der HSC-Wandler bietet eine hohe Leistung, da er die Energie über Kondensatoren und einen Transformator überträgt, was die Gesamtbelastung des Transformators und der Leistungs-MOSFETs reduziert.

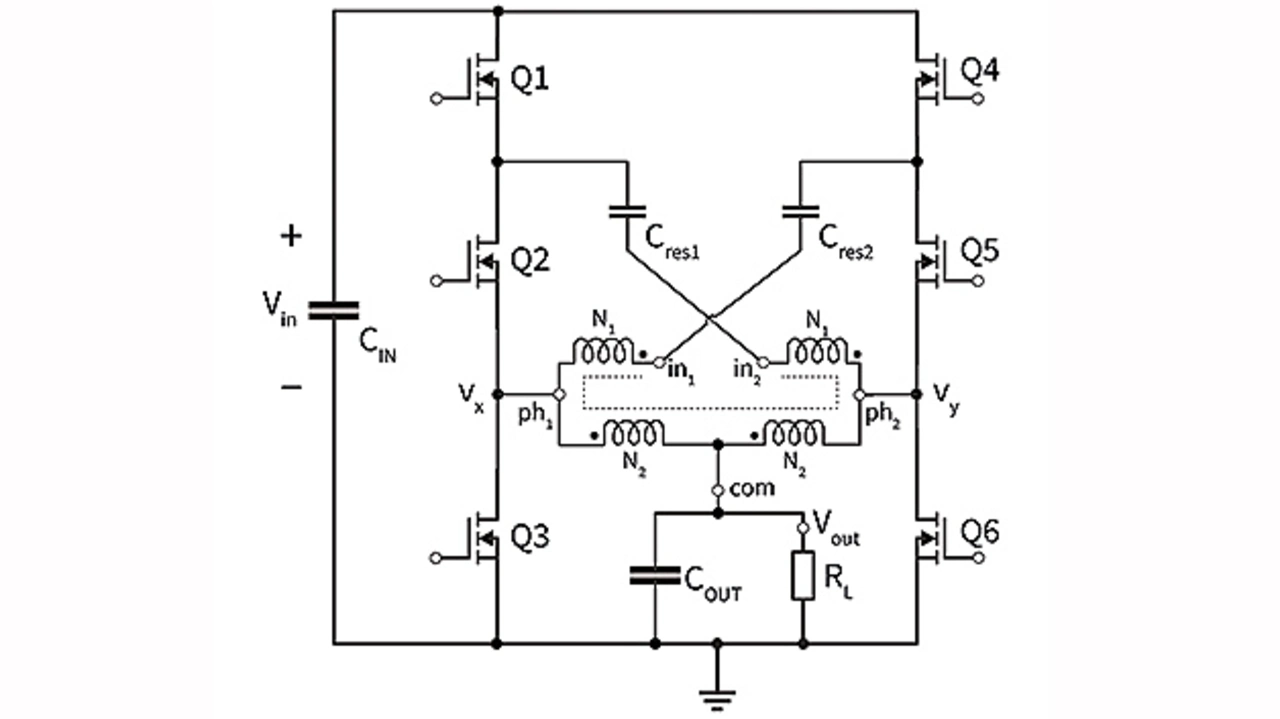

Allerdings kann diese neue Topologie (Bild 2) nicht allein die Leistungsdichte erreichen, die für KI-Anwendungen erforderlich ist. Erst in Kombination mit OptiMOS-Leistungs-MOSFETs und den neuen Gate-Treiber-ICs mit echten Differenzeingängen aus der EiceDRIVER-Familie wird der Wandler den KI-Trends gerecht.

Gate-Treiber bereitet den Weg

Bei dem HSC-HD-Wandler handelt es sich um einen 500 W starken Doppelphasen-Mehrstufen-Resonanzwandler mit einem maximalen Wirkungsgrad von 98 Prozent und einer Leistungsdichte von 341 W/cm2 (2,2 kW/Zoll2). Um diesen Wert zu erreichen, sind vier einkanalige Gate-Treiber-ICs in einem kleinen Formfaktor auf der High-Side erforderlich. Aus diesem Grund hat Infineon vor Kurzem den nicht isolierten EiceDRIVER 1EDN7550U mit echtem Differenzeingang (True Differential Input, TDI) in einem ultrakleinen Gehäuse auf den Markt gebracht (Bild 3).

Durch die TDI-Funktion können diese Treiber-ICs sowohl die High-Side- als auch die Low-Side-MOSFETs ansteuern und ermöglichen im Vergleich zu anderen Gate-Treiber-Lösungen die kleinsten Abmaße für einen Einkanaltreiber.

Das Gate-Treiber-IC bietet verschiedene Vorteile für den HSC-HD-Wandler und allgemein für andere Multi-Level-Topologien:

- Direkte Ansteuerung von High-Side-Schaltern mithilfe von TDI.

- Das TSNP-Gehäuse ist 1,1 mm × 1,5 mm groß. Die gesamte Layoutfläche beträgt weniger als 14 mm² pro Schalter, einschließlich der Widerstände für die weniger als 14 mm² pro Schalter, einschließlich der Widerstände für die Gleichtaktunterdrückung und des Versorgungs-Bypass-Kondensators.

- Vielseitige Platzierungsmöglichkeiten des Treibers für eine bessere Optimierung der Fläche, der Treiberschleife oder von beidem.

- Rth,JB im Vergleich zu allen anderen auf dem Markt erhältlichen Gehäusen halbiert.

- Beträchtliche Kosteneinsparung im Vergleich zu galvanisch isolierten Gate-Treiber-ICs.

Mit TDI die High-Side treiben

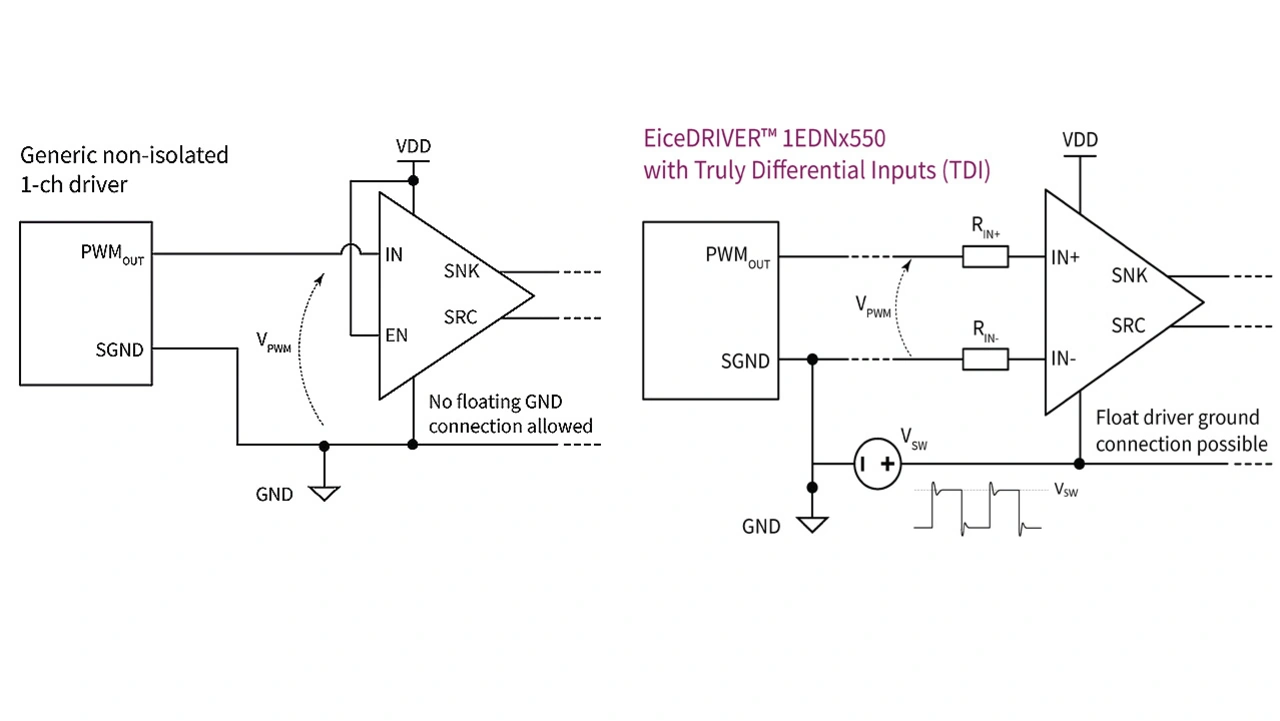

Durch die TDI-Stufe entfallen sperrige, teure und überspezifizierte isolierte Funktionstreiber. Ihr Funktionsprinzip ähnelt dem eines Differenzverstärkers. Durch die differenzielle Eingangsstufe kann man mit dem Treiber kommunizieren, ohne dass eine Pegelverschiebung (Level Shift) notwendig ist (Bild 4).

Daher kann sie Gleichtaktspannungen in Bezug auf Masse bis zur konfigurierten Gleichtaktunterdrückung (Common-Mode Rejection, CMR) abblocken.

Somit kann der Treiber High-Side-Schalter zuverlässig ansteuern, da die TDI-Stufe die Schaltknotenspannung VSW als Gleichtaktrauschen unterdrückt.

Bild 5 zeigt die Treiberkonfiguration für die Leistungs-MOSFETs Q1, Q2 und Q3 in der HSC-Topologie; die Treiberstufe für die Leistungs-MOSFETs Q4, Q5 und Q6 ist symmetrisch. Über kleine Vorwiderstände lassen sich die digitalen Ausgänge des Reglers direkt an den 1EDN7550U anschließen.

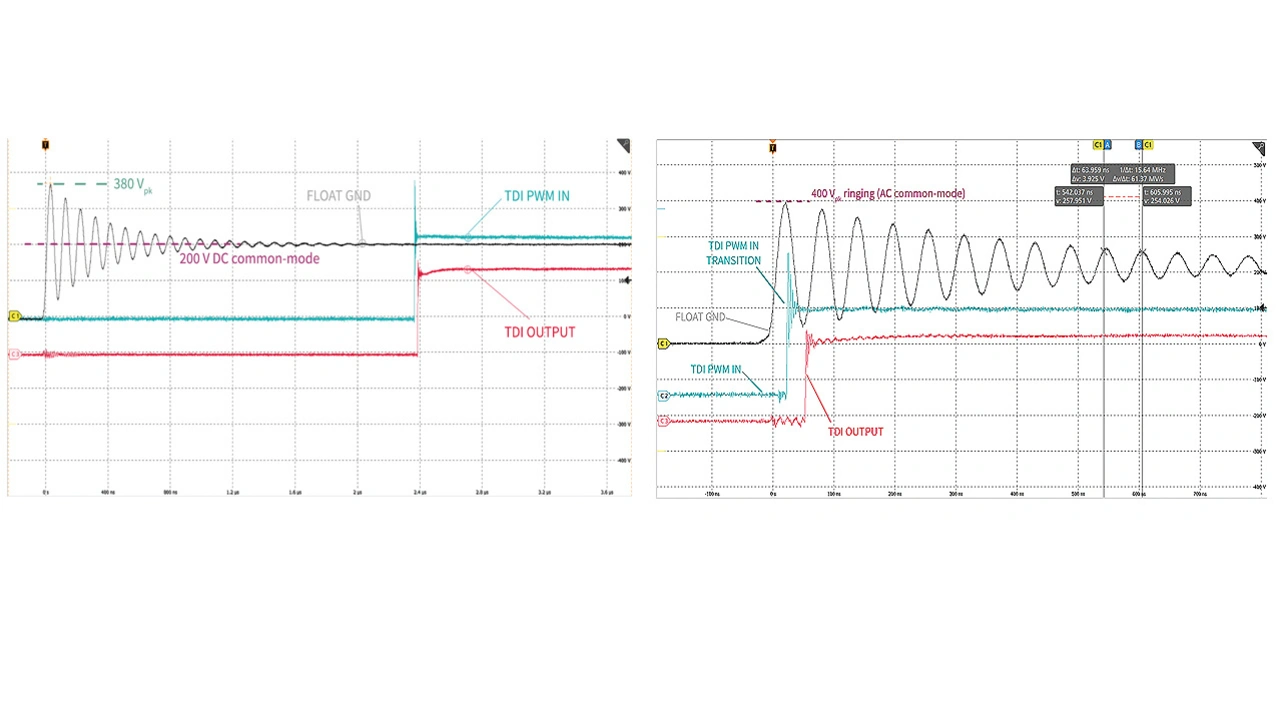

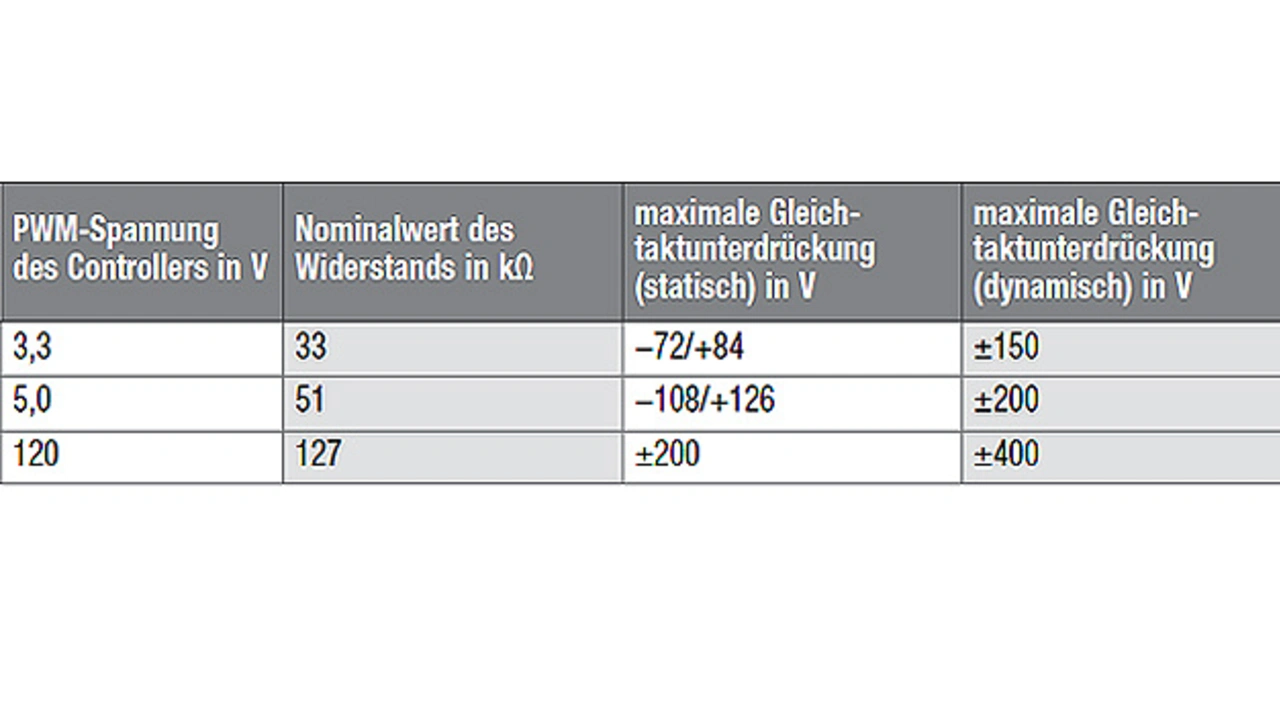

Der CMR-Wert definiert die maximale Gleichtaktspannung, die die TDI-Stufe unterdrücken kann. Der Parameter lässt sich konfigurieren, indem man die beiden kleinen Widerstände RIN+ und RIN- vor die Eingangspins schaltet. Durch Auswahl des richtigen Wertes, der Toleranz und des Formfaktors lässt sich ein CMR von bis zu ±200 V statisch und ±400 V dynamisch erreichen (Bild 6; Tabelle 1). Bild 6 zeigt die CMR-Fähigkeiten des 1EDN7550U. Der Treiber schaltet sauber (TDI-PWM-Eingang in Cyan, TDI-Ausgang in Rot), wenn mithilfe eines LC-Resonators ein 400-V-Schwingen oder ein 200-V-Offset an die schwebende Masse des Treibers (schwarze Farbe) angelegt wird.

In der HSC-Topologie entspricht die maximale Gleichtaktspannung, die jeder Gate-Treiber an der schwebenden Masse sieht, der Source-Spannung der Transistoren Q1, Q4, Q2 und Q5, da die treibenden PWM-Signale zusammen mit dem Mikrocontroller auf Masse bezogen sind. Für Q1 und Q4 entspricht die Gleichtaktspannung der maximalen Eingangsspannung VIN von 60 V, während sie für Q2 und Q5 den Spannungen Vx und Vy (siehe Bild 2) beim Ausschalten von Q3 und Q6 entspricht, also VIN,max/4 und damit 15 V. Sobald die maximale Gleichtaktspannung und die PWM-Spannung des Reglers bekannt sind, lässt sich der erforderliche statische CMR-Parameter der TDI-Stufe konfigurieren, um die High-Side-Schalter anzusteuern.

- Mehr Power für KI

- Treiberstufe auf Punktgröße verkleinern