Baugruppenfertigung

Boundary Scan für den effizienten RAM-Test

Hochkomplexe Komponenten wie etwa RAM-Speicherbausteine stellen im Baugruppentest besondere Anforderungen. Hier spielt Boundary Scan seine Vorteile aus. Einen Ansatz, der noch einen Schritt weiter geht, bietet die Embedded-JTAG-Solutions-Plattformsoftware System Cascon von Göpel Electronic.

Die Entwicklung hin zu immer höher integrierten Elektronikkomponenten stellt auch die Testingenieure in der Baugruppenfertigung vor neue Herausforderungen; die Miniaturisierung lässt oft nur wenig Spielraum bei der Auswahl der möglichen Testverfahren.

Über Jahrzehnte bewährte Testsysteme,...

...wie beispielsweise der In-Circuit- oder der Flying-Probe-Test stoßen immer mehr an Grenzen, weil eine Kontaktierung der Baugruppen über Testpunkte kaum noch möglich ist. Höhere Schnittstellen-geschwindigkeiten stellen auch die Entwickler von funktionalen Tests vor neue Aufgabenstellungen.

Um frühzeitig auf Fertigungsfehler reagieren zu können...

...und damit Folgekosten zu minimieren, müssen die Baugruppentests möglichst rechtzeitig, idealerweise schon beim Bestückungsprozess, durchgeführt werden. Dabei treten typischerweise bei der Fertigung eher Bestückungs-, d. h. Löt- und Handling-Probleme (z. B. falsches Bauteil) auf. Reale Bauteildefekte machen einen äußerst geringen Anteil im Fehlerspektrum aus, weil die Bauteilhersteller schon intensive Tests ihrer Bauteile durchgeführt haben.

Gerade in heutigen Baugruppen...

...mit immer höheren Signalgeschwindigkeiten, die oft nur mit elektrischen Testverfahren geprüft werden können, sind aber fehlerfreie Lötverbindungen für ein zuverlässiges Produkt entscheidend. Am Beispiel aktueller flüchtiger Speicherbausteine (RAM) lässt sich sehr gut aufzeigen, dass etablierte Testverfahren diese Aufgabe auch heute noch sehr gut lösen können.

Jobangebote+ passend zum Thema

Elektrische Tests im Fertigungsprozess

Boundary-Scan-Tests sind strukturelle und eher statische elektrische Tests, die über das sogenannte JTAG-Interface, eine 4-Draht-Verbindung, ausgeführt werden. Strukturell heißt in dem Zusammenhang, dass die Verbindungen der Pins nach außen überprüft werden und nicht die Funktion des Bausteins im Inneren. Statisch bedeutet, dass die Testausführung wesentlich langsamer stattfindet als mit der nominalen Geschwindigkeit des Bausteins oder der Baugruppe. Sämtliche Boundary-Scan-fähigen Bauteile werden für den Test in eine serielle Kette geschaltet, was das Routing auf der Baugruppe stark vereinfacht.

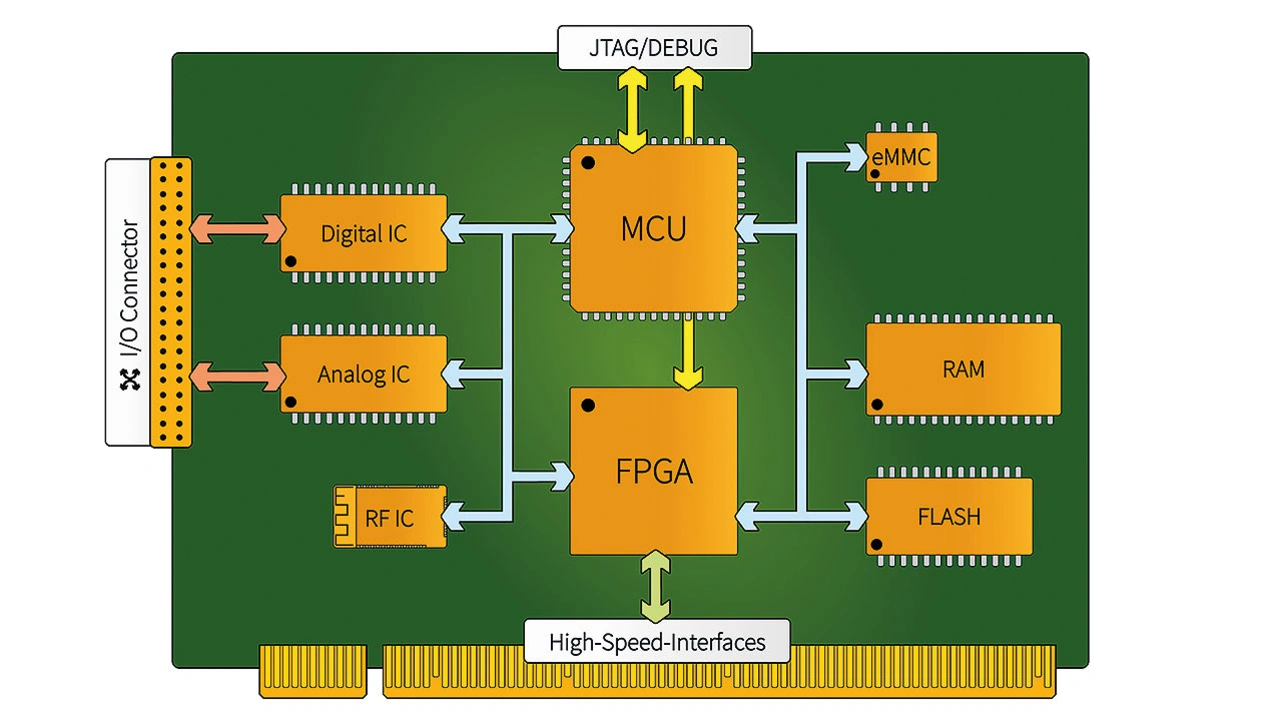

Mit Hilfe der Boundary-Scan-Technologie...

...werden nicht nur Verbindungstests zwischen kompatiblen Bausteinen durchgeführt, sondern auch angeschlossene nicht Boundary-Scan-fähige Bausteine funktional angesteuert, wie in Bild 1 schematisch dargestellt. Aufgrund des Prinzips eignet sich dieses Testverfahren sehr gut, um Fehler exakt zu lokalisieren, d. h. Lötbrücken zwischen zwei Pins lassen sich präzise aufspüren. Das ist ein großer Vorteil gegenüber den meisten Funk- tionstests. Durch die oft vorhandene bidirektionale Wirkungsweise der Boundary Scan Pins lässt sich ein Logikpegel treiben und gleichzeitig der auf dem Netz entstandene Pegel zurückmessen. Damit lassen sich schon sogenannte »Stuck-At«-Fehler, also Lötbrücken zu Betriebsspannung oder Masse, direkt lokalisieren. Das ist bei funktionalen Tests oft gar nicht möglich.

RAM-Speicher auf Fertigungsfehler testen

Im Gegensatz zu funktionalen Tests werden beim Boundary-Scan-RAM-Test nur die Verbindungen zum RAM geprüft und nicht der RAM-Speicher selbst. Aufgrund der seriellen Schiebekette, dem Grundprinzip des Boundary Scan, reduziert sich bei großen Boundary-Scan-ICs mit vielen Pins der erzielbare Datendurchsatz, sodass komplette RAM-Zellen-Tests viel zu lange dauern würden. Aber in der Baugruppenfertigung interessiert primär die korrekte Lötverbindung.

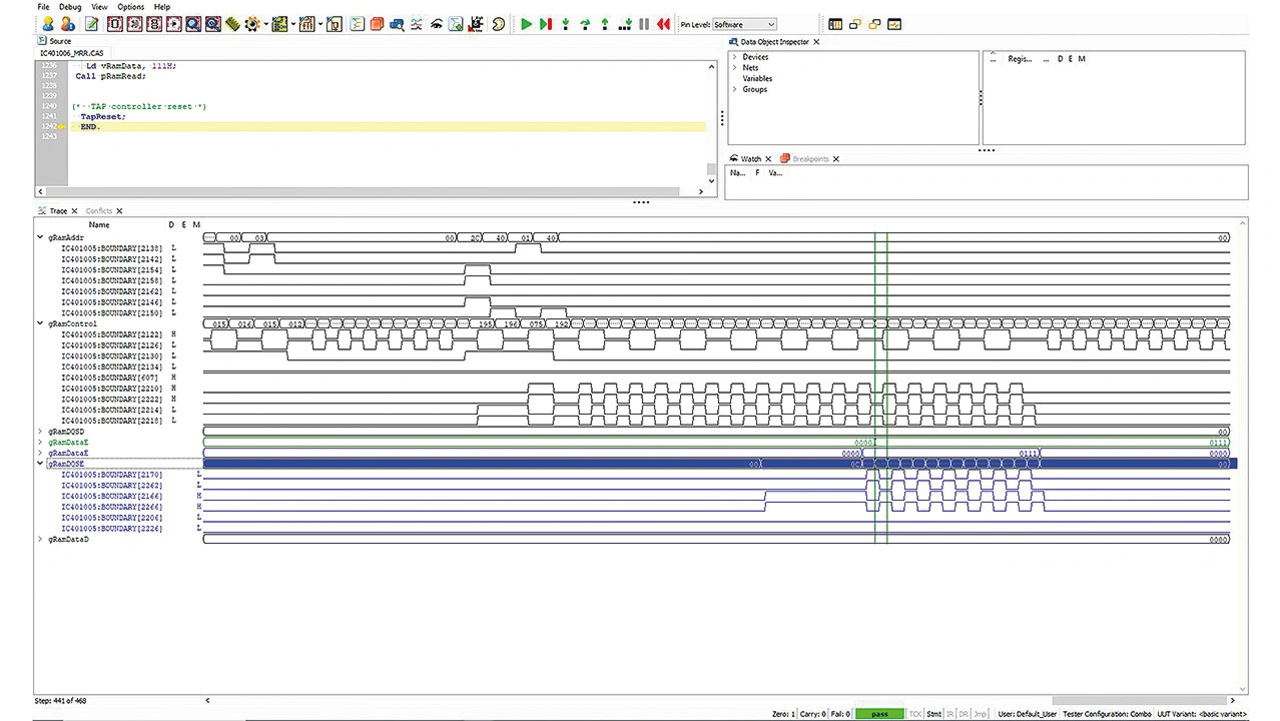

Die Stimulierung der RAM-Pins erfolgt im Prinzip nach den gleichen Mechanismen, wie bei einem funktionellen Test auch, d. h. es wird zunächst die Grundinitialisierung vorgenommen und danach werden bestimmte, für die Erkennung von Fehlerbildern optimierte Testpattern in den RAM geschrieben und anschließend wieder zurückgelesen (Bild 2). Das gilt sowohl für einfache SRAM- bis hin zu aktuellen LPDDR5-Bausteinen. Dabei spielen die Komplexität und Anzahl der an- geschlossenen RAM-Bausteine selbst keine Rolle, d. h. die Modelle sind so ausgelegt, dass mithilfe des Boundary-Scan-Systems die dafür notwendigen Tests vollkommen automatisch generiert werden können, sodass der Anwender kein spezifisches Wissen über die jeweiligen RAM-Bausteine besitzen muss.

Göpel Electronic zählt zu den Vorreitern, was das Testen solcher Bausteine betrifft. Der Test von SRAM-, DRAM-, DDR1-, DDR2- und DDR3-RAM-Bausteinen ist ein etablierter Bestandteil der Embedded-JTAG-Solutions-Plattformsoftware »System Cascon« und ist bei unzähligen Baugruppentests im täglichen Einsatz. Darüber hinaus ist Göpel Electronic einer der ersten Anbieter, der auch den Boundary-Scan-Test aktueller Speicherbausteine wie DDR4, LPDDR4 und LPDDR5 unterstützt. Eine stetig wachsende Bauteilbibliothek in System Cascon enthält bereits vorgefertigte und geprüfte Zugriffsbeschreibungen, damit der RAM-Test sehr schnell und automatisiert erstellt werden kann. Der Anwender muss nur das Modell aus der Bibliothek dem entsprechenden Baustein zuweisen. Die beim Boundary-Scan-RAM-Verbindungstest verwendeten spezialisierten Testpattern ermöglichen das gezielte Finden kurzgeschlossener oder nicht gelöteter Pins.

Die immer höheren Geschwindigkeiten...

...der RAM-Bausteine lassen vermuten, dass es mit statischen Testverfahren immer schwieriger wird, solche Bausteine zu testen. Allerdings zeigen die langjährigen Erfahrungen im Baugruppentest, dass sich diese Bausteine beim quasistatischen Test mit wenigen Testpattern unkritisch verhalten. Durch die integrierten Automatismen in den RAM-Bausteinen, u. a. Self-Refresh oder interne Taktgenerierung, lassen sich die Bausteine auch bei sehr niedrigen Zugriffsgeschwindigkeiten problemlos ansprechen und verlieren während des Testablaufs nicht ihren Speicherinhalt.

Darüber hinaus erlauben bestimmte RAM-Typen,...

...wie DDR4 oder DDR5, einen speziellen statischen Verbindungstest, den sogenannten Connectivity-Test, der mit dem TEN-Pin am RAM-Baustein aktiviert wird. Ist dieser Testmodus aktiv, wird eine Logikverknüpfung anstelle des RAM-Speichers im RAM-Baustein geschaltet, die das Testen von außen über einfache Testmuster erlaubt. Dabei werden typischerweise die Datenleitungen als Ausgänge und die Adress- und Steuersignale als Eingänge verwendet. Ein reales Beispiel an einem DDR4 RAM für so eine Logikverknüpfung sieht wie folgt aus:

DQ2 = A2 XOR A5 XOR A13

Steht dieser Connectivity-Test-Mode nicht zur Verfügung (z. B. bei LPDDR4 oder LPDDR5), können nur Boundary-Scan-RAM-Tests verwendet werden, die bestimmte Testpattern in die RAM-Zellen schreiben und zurücklesen. Damit lassen sich Kurzschlüsse, z. B. hervorgerufen durch Lötbrücken, oder auch nicht gelötete Pins exakt auf physikalischer Netzebene aufspüren. Dieser Test zeigt also nicht nur an, dass es einen Fehler gibt; sondern auch, wo er sich genau befindet, einschließlich der RAM-Steuerleitungen. Die können nämlich bei herkömmlichen Funktionstests im Fehlerfall nicht immer genau lokalisiert werden, entweder ein RAM-Zugriff funktioniert oder eben nicht.

Die Embedded-JTAG-Solutions-Plattformsoftware...

...System Cascon bietet darüber hinaus weitere Optimierungen im RAM-Testgenerator an, um die Testzeit zu minimieren. Man kann beispielsweise einen sogenannten Go/NoGo-Test mit reduzierten Testpattern automatisch generieren lassen. Am Anfang des Tests werden grundlegende Testpattern ausgeführt, die eine prinzipielle Fehlererkennung ermöglichen. Erst bei einem auftretenden Fehler werden speziellere und umfangreichere Testpattern verwendet, die eine exakte Diagnose auf Netz- und Pin-Ebene ermöglichen. Damit lässt sich wertvolle Testzeit einsparen, was gerade bei In-Line-Fertigungssystemen eine wichtige Anforderung darstellt, denn das Testverfahren darf die eigentliche Bestückungstaktzeit nicht verlängern, um die Fertigung insgesamt nicht auszubremsen.

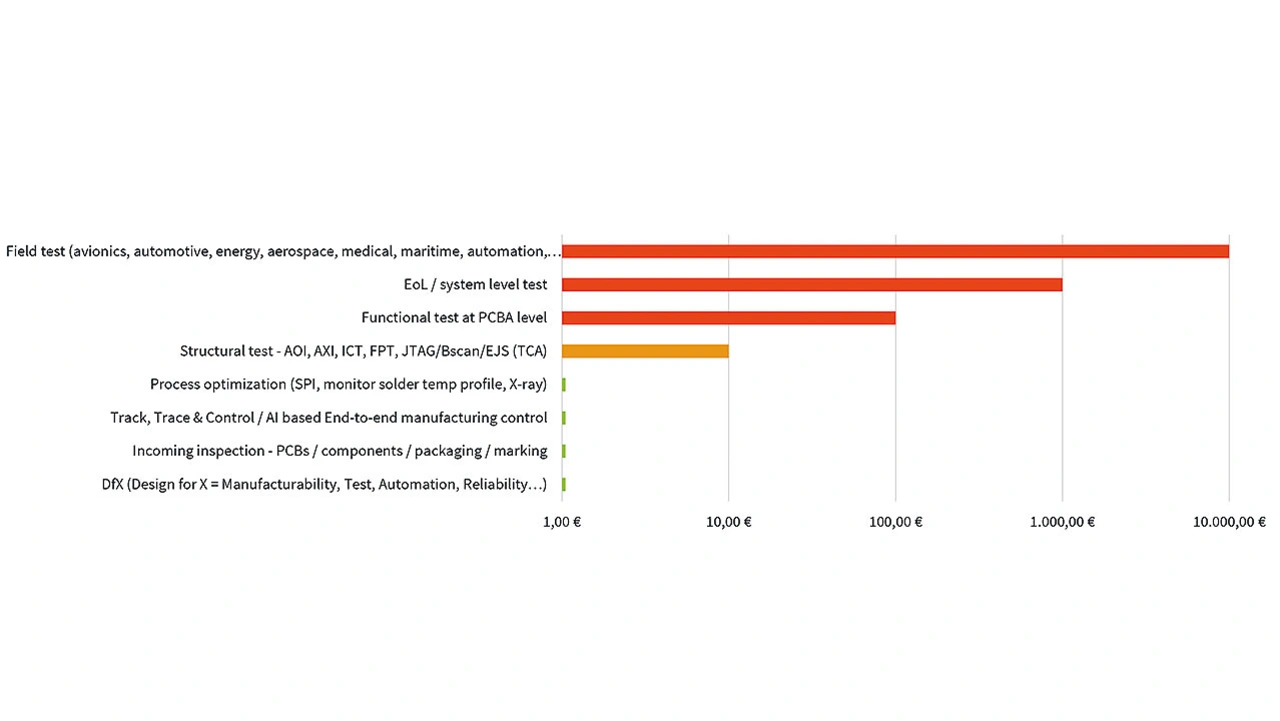

Einfache und zuverlässige Produkttests sparen Zeit und Kosten

Diese Testlösung für einen einfachen strukturellen Boundary-Scan-Test zeigt, dass es sehr gut möglich ist, auch ohne Funktionstests eine Baugruppe während des Fertigungsprozesses oder später bei auftretenden Defekten umfangreich und vor allem präzise zu prüfen. Dabei stellt System Cascon eine wertvolle Hilfe für den Testentwickler dar, weil viele Tests vollautomatisiert sehr schnell und einfach generiert werden können, was wiederum Testentwicklungszeit und damit letztendlich Kosten bei der Fehler- suche spart (Bild 3).

Die Bereitstellung neuer Bibliotheksmodelle zur Unterstützung aktueller LPDDR5-RAM-Bausteinen hilft Anwendern bei der Suche nach agilen Testlösungen über den gesamten Produktlebenszyklus, angefangen bei der Designentwicklung, über den Fertigungstest bis hin zur Reparatur und Wartung von Baugruppen.

Die Autoren

Sven Haubold ist Senior Hardware Engineer im Bereich Embedded JTAG Solutions bei Göpel Electronic.

Tino Ackermann ist Applikationsmitarbeiter im Bereich Embedded JTAG Solutions bei Göpel Electronic.