IEDM 2017

Intel und Globalfoundries mit dritter FinFET-Generation

Fortsetzung des Artikels von Teil 1

Globalfoundries mit 7-nm-CMOS-Plattform für Mobil- und High-Performance-Computing

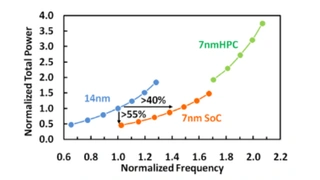

Von der US-Ostküste, aus Malta/New York, kommt die 7-nm-CMOS-Plattform von Globalfoundries mit ebenfalls der dritten FinFET-Generation. Globalfoundries nutzt SAQP (Self-Aligned Quad Patterning) für die Formung des Fins und SADP (Self-Aligned Dual Patterning) für die BEOL-Metallisierungsschichten (Back-End Of Line). Die geroutete Logikdichte konnte um den Faktor 2,8 gegenüber der Vorgänger-Technologie 14 nm gesteigert werden. Wahlweise bietet der SoC-Prozess je nach Chipauslegung 40 % mehr Schaltgeschwindigkeit oder 55 % weniger Leistungsaufnahme. Darüber hinaus gibt es eine High-Performance-Version oberhalb der SoC-Technologie.

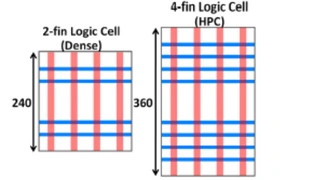

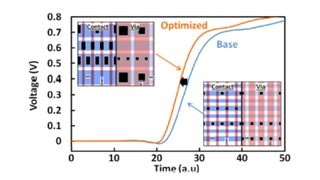

Der Fin-Pitch beträgt 30 nm, der Contacted Gate Pitch liegt bei 56 nm und der kritische BEOL-Metal-x-Pitch bei 40 nm. Alle Werte sind im Vergleich zum 14-nm-Vorgänger-Prozess deutlich verbessert worden. Die 2-Fin-Standardlogikzelle wurde signifikant in der Höhe reduziert. Insgesamt konnte so eine Verkleinerung um den Faktor 0,36 erzielt werden, gemittelt über einen repräsetativen Mix von kritischen Zellen. Für High-Performance-Anwendungen stehen auch 4-Fin-Logikzellen zur Verfügung. Die 4-Fin-Zelle bietet dazu größere Verdrahtungsstrukturen und Kontaktflächen. Ein Schlüssel zur starken Verkleinerung ist das SADP-Lithographie-Verfahren mit 193-nm-Immersion-Technik für die verschiedenen Metallisierungslagen von M0 bis M4. Um vielen Kunden gerecht zu werden, unterstützt Globalfoundries eine Reihe von breiten Verdrahtungsstrukturen, großen Kontaktflächen und Vias. Eine Reduzierung der parasitären Widerstände geschieht über Junction/Epi-Optimierung und ein Zuschneiden des Kontaktwiderstandes per Trench-Implantierung. Die Einführung von Kobalt reduziert die Kontaktwiderstände im Vergleich zu Kupfer. Ein Multi-Work-Function-Prozess der zweiten Generation erlaubt undotierte Fins zur Einstellung verschiedener Schwellspannungen Ut. Das bringt zwei Vorteile: FETs mit höherer Ut bieten eine höhere Ladungsträgermobilität und das Weglassen der Dotierung verbessert die Ut-Fehlanpassung (mismatch).

Globalfoundries hat zwei SRAM-Zellen entwickelt, die für hohe Schaltfrequenzen misst 0,0353 µm2, während die auf Dichte optimierte SoC-Zelle nur 0,0269 µm2 aufweist. Die 7-nm-Prozessgeneration zeigt gegenüber 14 nm die doppelte Schaltleistung und die doppelte Dichte. Die dritte FinFET-Generation zeigt charakteristische steile subschwellen Anstiegsflanken mit 69 mV/Dec für NMOS (72mV/Dec für PMOS). Sowie niedrige DIBL-Werte (Drain Induced Barrier Lowering) von 40 mV/V für NMOS (52 mV/V für PMOS).

Der 7-nm-Pozess umfasst mehrere Kupfer/Low-k BEOL Stacks für unterschiedliche Anwendungsgebiete. Der Mx-Metallierungsprozess wurde um den Faktor 100 weniger Anfällig für Elektromigration. Zusätzlich gibt es eine Anzahl von integrierbaren verbesserten Komponenten, wie einen MiM-Kondensator, der Schaltungen von der Stromversorgung entkoppelt, oder einen MOS-Kondensator für Entkopplungen jeder Art. Während beim MiM-C die Dichte um den Faktor 2 zulegte, ist es beim MOS-C der Faktor 1,6.

Schließlich hat Globalfoundries noch Vorbereitungen getroffen, um auch künftig bei 7 nm EUV-Lithographie bei kritischen Elementen einsetzen zu können, wie bei MOL, Kontakten oder BEOL Vias. EUV reduziert kritische Masken um 25 %. Im nächsten Jahr will das Unternehmen den neuen ASIC-Technologie-Baukasten FX7 anbieten, der auf dem 7-nm-Prozess basiert.

Jobangebote+ passend zum Thema

7 nm als dritte Generation der FinFET-Prozesse.

- Intel und Globalfoundries mit dritter FinFET-Generation

- Globalfoundries mit 7-nm-CMOS-Plattform für Mobil- und High-Performance-Computing