ISSCC 2023

Die Energieeffizienz ist das größte Problem

Fortsetzung des Artikels von Teil 1

Weitere Optimierungsmöglichkeiten, um die Energieeffizienz zu verbessern

Speicher und IO

Der Energieverbrauch für die Datenübertragung zwischen Prozessor und Speicher hängt stark von der Art des Speichers und der Art der Verbindung zwischen Speicher und Prozessor ab. Im Vergleich zu DDR5 lässt sich mit HBM-Speichern eine viel höhere Bandbreite erreichen und gleichzeitig sinkt der Energieverbrauch pro Bit um drei- bis viermal. Bei einer 3D-Stacking-Technik, bei der der Speicher direkt auf dem Rechen-Die aufgesetzt wird, steigt die Bandbreite und die Leistungsaufnahme sinkt auf nur noch 0,2 pJ/bit. Su hält es für möglich, dass mit anderen Speichertechnologien als SRAM (wird heute in den Stapeln verwendet) noch weitere Energieeinsparungen möglich sind. »Es wird auch viel über Processing in Memory diskutiert, hier arbeitet AMD mit Samsung zusammen, ein weiterer vielversprechender Ansatz«, so Su weiter. Denn die Energie, die notwendig ist, um ein einzelnes Bit aus dem Speicher auszulesen, liegt in derselben Größenordnung wie die Energie, die zur Durchführung einer ganzen 64-Bit-Gleitkommaoperation erforderlich ist. Das heißt, dass es bei bestimmten Operationen wesentlich effizienter sein kann, diese Operation im Speicher selbst auszuführen. Allerdings ist es nicht so einfach, die richtigen Operationen zu bestimmen, die sich dafür eignen, und auch die entsprechende Software fehlt, »aber mit dieser Technik lassen sich bis zu 85 Prozent der Energie einsparen, die für die Datenbewegung notwendig ist, also ein durchaus vielversprechender Ansatz«, so Su.

Geht es um die Kommunikation ist Su überzeugt, dass die Zukunft in optischen Interconnects liegen wird. Das heißt, dass einerseits im Packaging-Bereich einiges passieren muss, andererseits aber auch in den Kommunikationsmöglichkeiten von Chiplet-Architekturen.

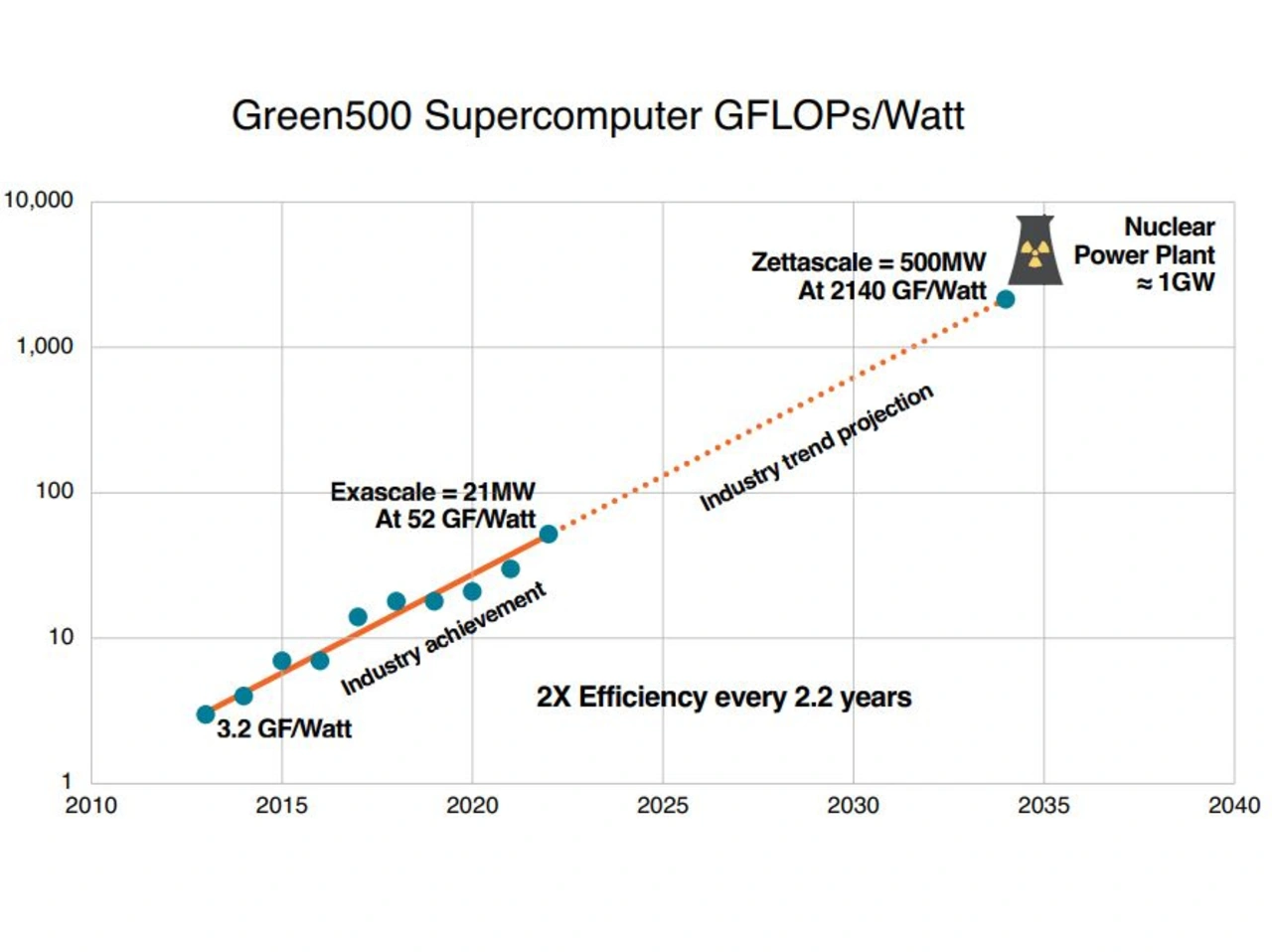

Optimierte Hardware und KI

Eine andere Möglichkeit, die Energieeffizienz zu steigern, besteht aus Sicht von Su in Beschleunigern, denn sie sind im Vergleich zu General-Purpose-Architekturen deutlich energieeffizienter. Als Beispiel verweist sie auf den AMD Instinct MI250 Beschleuniger, der im Exascale Frontier Supercomputer arbeitet. Su: »In diesem Fall wurde eine Exaflop-Rechenleistung mit einem Energiebudget von 21 MW erreicht. Das entspricht der 2,5-fachen Leistung im Vergleich zum vorher führenden Supercomputer und das bei einer 3,5-mal so hohen Energieeffizienz.« Su führt diese Steigerung auf die hochparallele und effiziente GPU-Architektur und die Implementierung spezieller Matrixmultiplikationsprimitive zurück, denn damit ist es möglich, GEMM-Operationen (generalisierte Matrix-Matrix-Multiplikation), wie sie häufig in Linpack und vielen HPC-Algorithmen verwendet werden, effizienter auszuführen. Su: »Dadurch wird die benötigte Energie pro 64-Bit-Gleitkomma-Operation im Vergleich zu herkömmlichen Allzweck-Gleitkomma-Operationen ungefähr halbiert, so dass Software-Algorithmen, die diese Primitive richtig nutzen, eine viel höhere Recheneffizienz erzielen können.« Als weitere Beispiele in diesem Zusammenhang verweist Su auf Beschleuniger in Smartphones und PCs, die Aufgaben wie Videokodierung und -dekodierung oder Bildverarbeitung übernehmen und dafür viel weniger Energie benötigen als General-Purpose-CPUs.

In diesen Beschleunigern ist der Algorithmus direkt auf der Hardware abgebildet, der gesamte Overhead von Allzweck-CPUs, der für die Software-Programmierbarkeit benötigt wird, fällt weg. Außerdem kann dann die Genauigkeit genutzt werden, die auch wirklich passt. Bei einem General-Purpose-CPUs kommt grundsätzlich der IEEE-Gleitkommastandard zum Einsatz. Er bietet zwar eine hohe Genauigkeit und es gibt jede Menge an Software-Bibliotheken, aber das geht zulasten eines hohen Energiebedarfs. Das Datenformat kann aber entscheidend sein, wenn es um Energieeffizienz geht. Su erklärt weiter, dass dieser Ansatz am deutlichsten im Bereich Maschinenlernen wird, wo ständig neue Datenformate wie Brain-Float 16 und FP8 entwickelt werden, die die Leistungsaufnahme deutlich verringern. Su ist überzeugt, dass eine optimales Datenformat auch im HPC-Bereich viel bringen könnte.

Sie ist grundlegend davon überzeugt, dass KI-Methoden im HPC-Bereich verstärkt genutzt werden sollten, um die Energieeffizienz zu erhöhen. Geht es beispielsweise um umfangreiche Physikberechnungen, könnte ein Teil des aufwendigen Codes durch KI-basierte Modelle ersetzt werden, die Genauigkeit wird dann mithilfe »normalen« Codes erreicht. Das heißt, die KI-Modelle erlauben eine Näherung an das Ergebnis, die in der anschließenden Phase mithilfe von reinem Code so verbessert wird, dass ein genaues Ergebnis möglich wird – die Folge: dieser Ansatz ist schneller und energieeffizienter. Dieser Ansatz befindet sich laut Su erst in der Anfangsphase, aber mit einer optimierten Plattform mit paralleler KI- und HPC-Rechenkapazität hält sie eine deutlich gesteigerte Energieeffizienz für möglich.

KI wird darüber hinaus auch im Design eingesetzt. EDA-Tools verfügen mittlerweile über KI-gesteuerte Ansätze, um eine Design Space Optimization (DSO) durchzuführen, so dass PPA-Optimierungen möglich sind. AMD hat hierzu Untersuchungen durchgeführt. Laut Su konnte das Unternehmen mithilfe eines DSO.ai-Flows deutliche Verbesserungen der Ergebnisse gegenüber den am besten abgestimmten und optimierten Entwürfen der erfahrensten Entwicklungsingenieure erreichen. Su ist überzeugt, dass eine verstärkte Nutzung der KI-Methodik beispielsweise in Richtung Logik-Refactoring, Re-Pipelining oder andere mikro-architektonische Änderungen noch weitere deutliche Verbesserungen ermöglicht.

Fazit

Su ist überzeugt, dass die Energieeffizienz der entscheidende Faktor ist, um die Datenverarbeitung auf die Zettascale-Ebene zu heben. Allerdings müssen dafür Innovationen auf allen Ebenen erfolgen, angefangen beim Silizium und Packaging, über Design und Architektur, bis hin zur Software und den Algorithmen. »Nur wenn wir alle Ansätze in vollem Umfang nutzen, werden wir einen Weg zu einer Leistung auf Zettascale-Anwendungsebene innerhalb eines 100-MW-Rahmens finden«, fasst Su zusammen.

Jobangebote+ passend zum Thema

- Die Energieeffizienz ist das größte Problem

- Weitere Optimierungsmöglichkeiten, um die Energieeffizienz zu verbessern