Efinix

FPGAs für intelligente Edge-Anwendungen

FPAGs haben immer noch den Ruf, dass sie groß und teuer sind sowie eine hohe Verlustleistung aufweisen. Dies trifft sicherlich für einige FPGAs zu, doch es gibt auch Alternativen auf dem Markt, die das genaue Gegenteil sind: klein, kostengünstig und energiesparend.

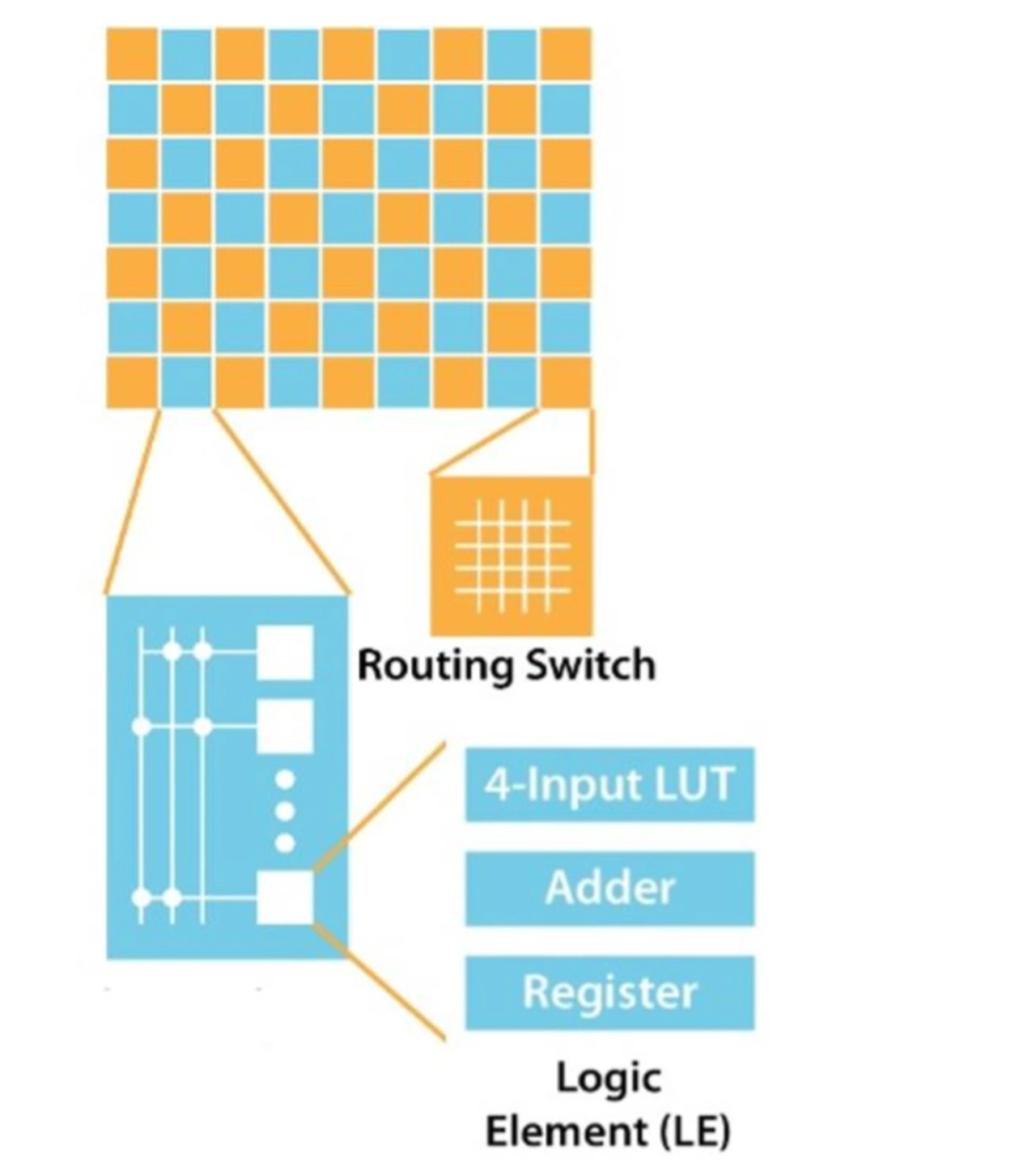

Auch nach ca. 35 Jahren sehen die FPGA-Architekturen immer noch ähnlich aus. Die Architektur hat feste Logikzellen und ein festes Routing über das komplette Silizium verteilt. Routing ist ein sehr wichtiger Teil eines FPGAs, damit man die verschiedenen Ein/ Ausgänge der Logikzellen miteinander verbinden kann, um das gewünschte Verhalten der Schaltung zu erreichen. Gleichzeitig gibt es aber auch noch die Anforderung, dass dieses Design in einer vorgegebenem Geschwindigkeit laufen muss. Das bedeutet, dass die Verbindungen relativ direkt und ohne Umwege implementiert werden müssen. Dazu muss man bei dieser alten Architektur sehr viele Routing-Ressourcen zur Verfügung stellen, um diese Ziele zu erreichen.

Jobangebote+ passend zum Thema

Die High-End-FPGAs brauchen hierfür sehr viele Routing Ressourcen, was zu einer großen Siliziumfläche und hoher Verlustleistung führt. Die Mid-Range- oder Low-Range-FPGAs haben meist die gleichen Logikzellen wie die High-End-FPGAs, unterscheiden sich aber meist in der Anzahl der zur Verfügung stehenden Routing-Ressourcen. Normalerweise werden die Routing-Ressourcen so berechnet, dass bis zu einer Auslastung von 75 Prozent der Baustein gut zu routen ist. Eine höhere Auslastung ist auch möglich, aber dann erweist sich das Verdrahten der Logikzellen als sehr schwierig. Das bedeutet es können nicht mehr direkte Verbindungen benutzt werden, sondern es müssen Umwege in Kauf genommen werden, was in einer Verringerung der Systemfrequenz resultieren kann.

Die bis heute genutzte Innovation besteht darin, die Prozessgeometrien zu reduzieren, da kleinere Siliziumstrukturen eine höhere Systemfrequenz ermöglichen. Die Nachteile eine kleineren Siliziumstruktur sind aber erhöhte Kosten, die ein solcher Schritt mit sich bringt, sowie teilweise eine erhöhte statische Verlustleistung. Diese Innovationsmöglichkeit löst also nicht das eigentliche Problem, sondern schiebt es nur vor sich her.

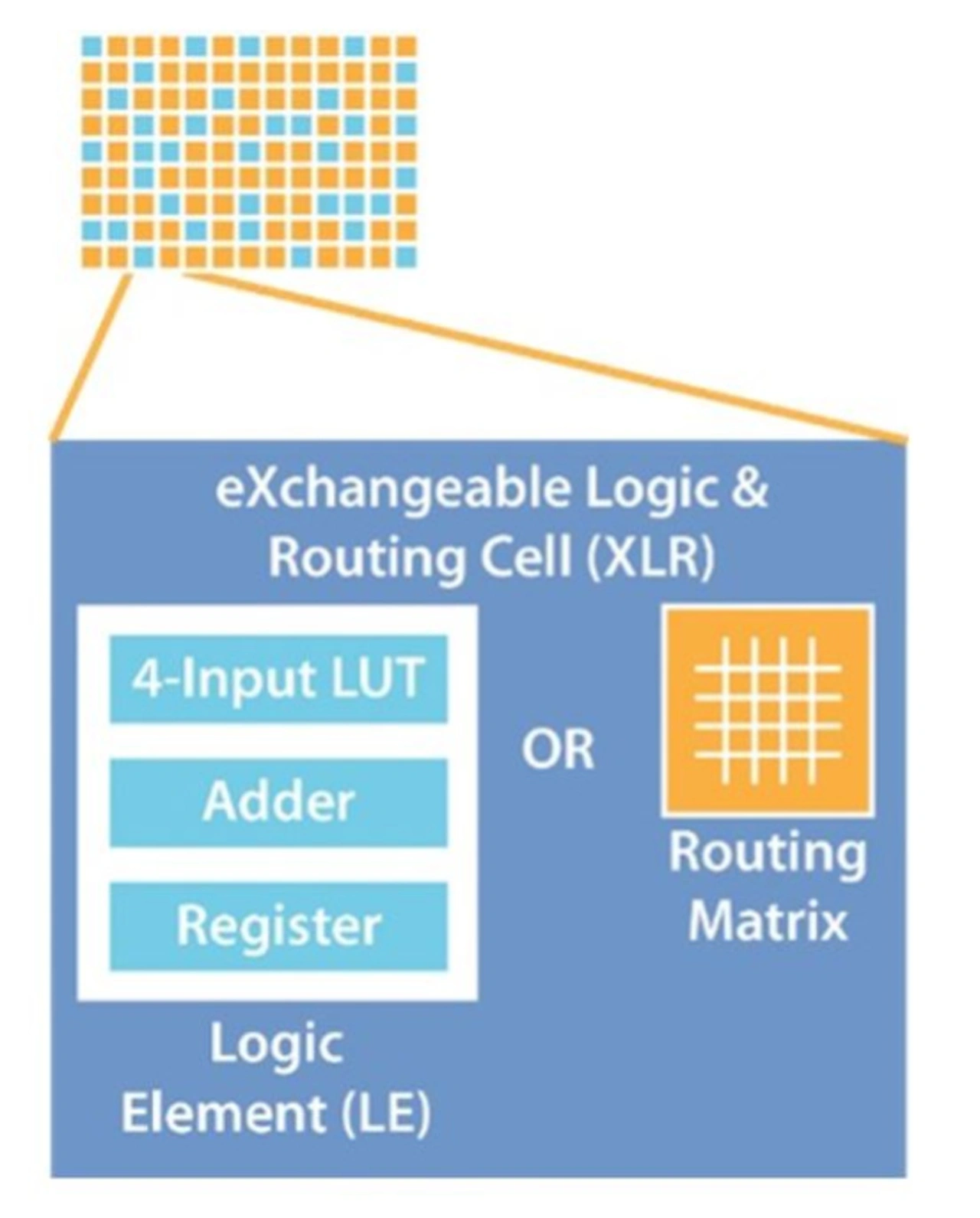

Eine neue Architektur löst das Problem

Efinix hat eine neue FPGA-Architektur entwickelt, mit der das eigentliche Problem gelöst wird. Denn bei der »Quantum«-Architektur von Efinix sind nur sehr wenige Routing-Ressourcen über das Silizium verteilt. Um trotzdem über das FPGA routen zu können, benutzt Efinix die so genannten XLR-Zellen (eXchanable Logic and Routing), die sowohl als Logikzellen als auch als Routing-Ressource fungieren können. Mit diesem Ansatz können Routing-Ressourcen in den Bereichen zur Verfügung gestellt werden, in denen sie benötigt werden. Dadurch erreicht man eine wesentlich geringer Siliziumfläche verglichen zu den FPGAs heutiger Marktführer. Dadurch sinkt auch der statische - aber auch der dynamische Stromverbrauch. Der statische Stromverbrauch ist normalerweise eine Funktion über die Fläche, das bedeutet: größere Fläche, größerer Stromverbrauch.

Der dynamische Stromverbrauch ist auch deutlich geringer, da die Verbindungen kürzer sind und somit die parasitären Effekte geringer ausfallen, welche typischerweise die dynamische Verlustleistung negativ beeinflussen.

Ein zusätzlicher Vorteil der neuen Quantum-Architektur besteht darin, dass die Auslastung über 90 Prozent liegen kann, ohne dass man eine Verringerung der Systemfrequenz in Kauf nehmen muss.

»Titanium«-FPGA-Familie

Die Titanium-FPGA-Familie basiert auf der Quantum-Architektur und zeigt in der Anwendung genau die Vorteile, die oben beschrieben wurden: Sehr hohe Systemfrequenz bei geringer Verlustleistung. Dieses Verhalten ist genau das, das in Edge-Applikationen benötigt wird, um die Produkte intelligenter zu machen, ohne eine Verbindung zum Internet bzw. externe Server benutzen zu müssen.

Die Titanium-Familie unterstützt Systemfrequenzen zwischen 400 und 500 MHz, dies ist jedoch abhängig vom Design, speziell von der Anzahl der kombinatorischen Tiefe des Designs. Neben der Systemfrequenz sind natürlich noch weitere Eigenschaften von Interesse.

Ein wichtiger Punkt in Edge-Anwendungen ist die Größe des Bausteins. Meist haben solche Anwendungen nur einen limitierten Platz zur Verfügung. Hier hilft die Quantum-Architektur ebenfalls, denn mit ihr stehen sehr kleine Bausteine mit entsprechenden Logikressourcen zur Verfügung. Ein gutes Beispiel ist der Ti60W64. Das ist ein Baustein mit ca. 60K Logikelementen und einer Bausteingröße von 3,5 x 3,4 mm². Diese Größe bei dieser Logikkomplexität ist einzigartig im FPGA-Markt und zeigt die Überlegenheit der Quantum-Architektur.

Darüber hinaus sind auch die unterstützen Schnittstellen von Interesse. Für Kamera Anwendungen werden oft MIPI CSI-2, LVDS oder auch SLVS-EC benötigt. Alle Titanium-Bausteine unterstützen MIPI CSI-2 bis 1,5 Gbps auf den Standard HSIOs ohne zusätzliche Beschaltung. Ab Ti85 wird MIPI CSI-2 zusätzlich bis 2,5 Gbps an dedizierten MIPI-D-PHYs angeboten. Der MIPI CSI-2 Block wird als Soft-IP im IP-Katalog kostenfrei angeboten. Das Soft-IP hat den Vorteil, weitere Formate nachträglich zu dem Block hinzufügen zu können. Alle Titanium-FPGAs unterstützen eine Standard-LVDS-Schnittstelle mit einer Geschwindigkeit bis 1,5 Gbps. Der SLVS-EC-Standard wird von allen Titanium-Bausteinen mit High-Speed-SERDES unterstützt (Ti85,Ti135, Ti165, Ti240, Ti375). Der entsprechende IP-Core wird von einem 3rd-Party-IP-Anbieter angeboten.

Um Daten zwischenzuspeichern, werden oft Speicherschnittstellen benötigt. Diese müssen schnell, aber auch stromsparend sein. Die Titanium-Familie unterstützt Speicherschnittstellen für LPDDR4 und LPDDR4X bis 3,3Gbps, abhängig von den jeweiligen Gehäusen. Der Speicher-Controller ist fest im Silizium integriert, um die entsprechende Geschwindigkeit aber auch eine geringe Verlustleistung zu gewährleisten. LPDDR4X ist für Edge-Anwendungen optimal geeignet, da die Schnittstellen schnell und stromsparend sind. Außerdem sind LPDDR4X-Speicher lange verfügbar, da diese gerne im Automotive Bereich eingesetzt werden.

Weitere Schnittstellen für Edge-Anwendungen sind Ethernet (bis 10 GE), um Daten schnell und über eine lange Distanz zu übertragen. Für eine Anbindung an ein PC-System, wir oft auch PCI-Express benötigt. Beide Schnittstellen werden von den Titanium-FPGAs mit SERDES unterstützt, PCI-Express bis Gen4x4.

Schnittstellen wie SDI, CoaXpress, HDMI und DP können bei den Titanium FPGA mit SERDES im PMA-Direkt-Mode angeschlossen werden. Entsprechende 3rd Party IP Anbieter unterstützen die Titanium-Architektur mit Ihren IPs.

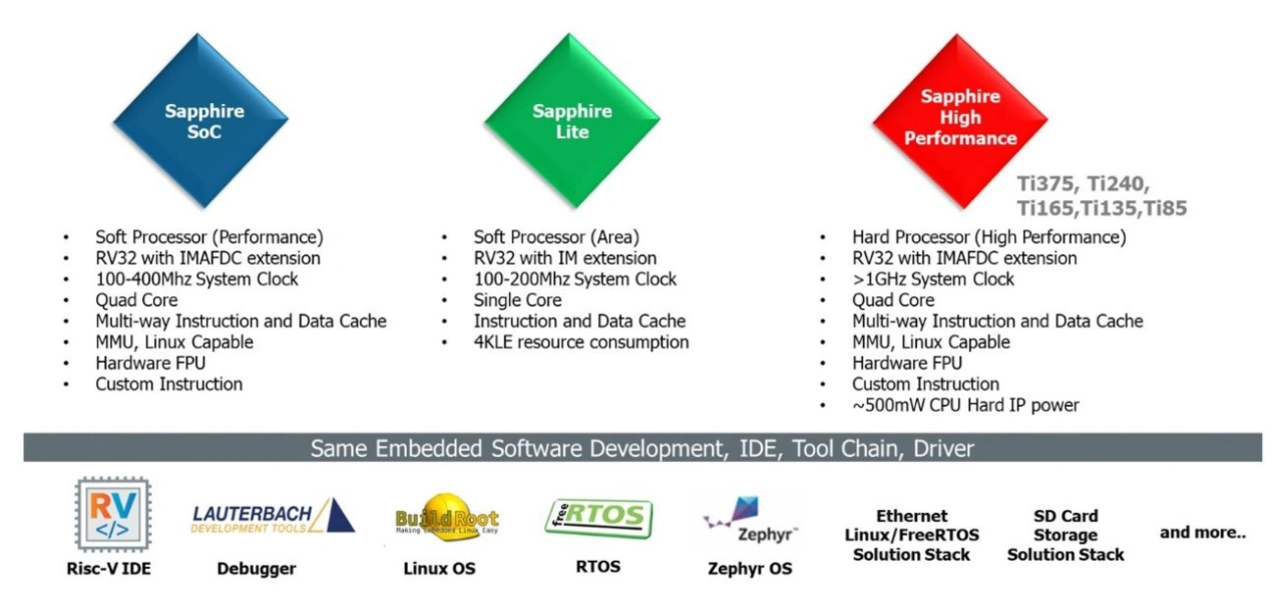

RISC-V

Nicht selten werden Prozessoren in ein FPGA implementiert, oder fest verdrahtete Prozessoren benutzt. Efinix setzt hier auf RISC-V als Prozessor, der als Soft-IP implementiert werden kann. Dieser kann eine Systemfrequenz von bis zu 400 MHz in den Titanium-FPGAs erreichen. Das Soft-IP verfügt über eine MMU, sodass Linux auf dem Prozessor benutzt werden kann. Damit ist RISC-V in vielen Anwendungen nutzbar, plus dem Vorteil: Für diese Architektur fallen keine Lizenzkosten an. Außerdem eignet sich RISC-V sehr gut für Low-Power-Anwendungen. Für Applikationen, die einen schnelleren Prozessor benötigen, bieten alle Titanium Bausteinen mit SERDES (Ti85, Ti135, Ti165, Ti240, Ti375) einen fest verdrahteten Quad RISC-V. Dieser kann mit 1 GHz getaktet werden. Laufen alle vier Cores mit 1 Ghz, liegt die typische Verlustleistung bei ca. 500 mW. Dieser Wert unterscheidet sich erheblich zu dem von vergleichbaren FPGAs.

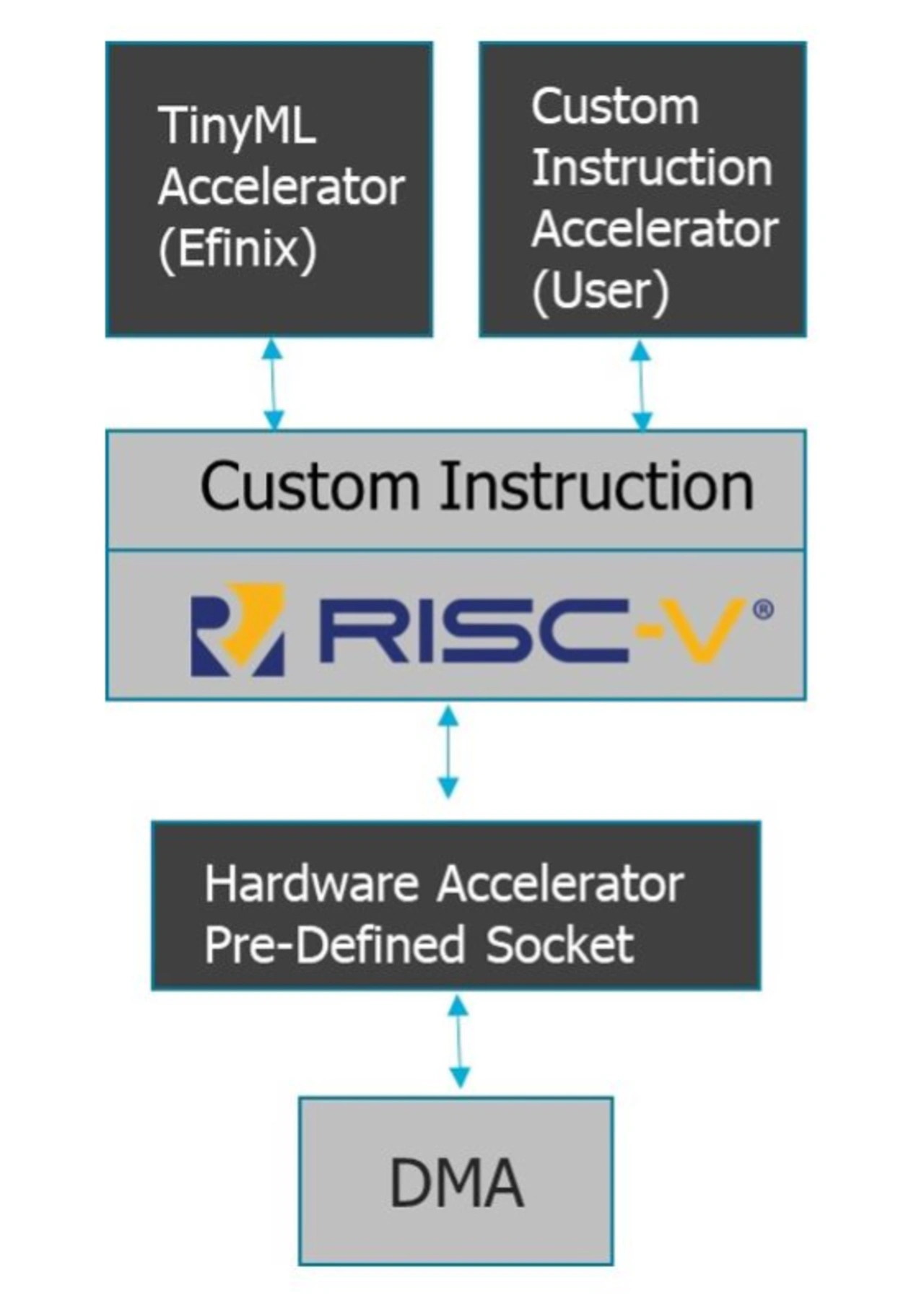

Das Soft-IP sowie der Quad RISC-V als Hard-IP unterstützen »Custom Instructions«, mit denen spezielle Funktionen beschleunigt werden können. Efinix nutzt diese Custom Instructions in seinen KI-Lösungen, die auf RISC-V basieren.

KI-Lösungen von Efinix

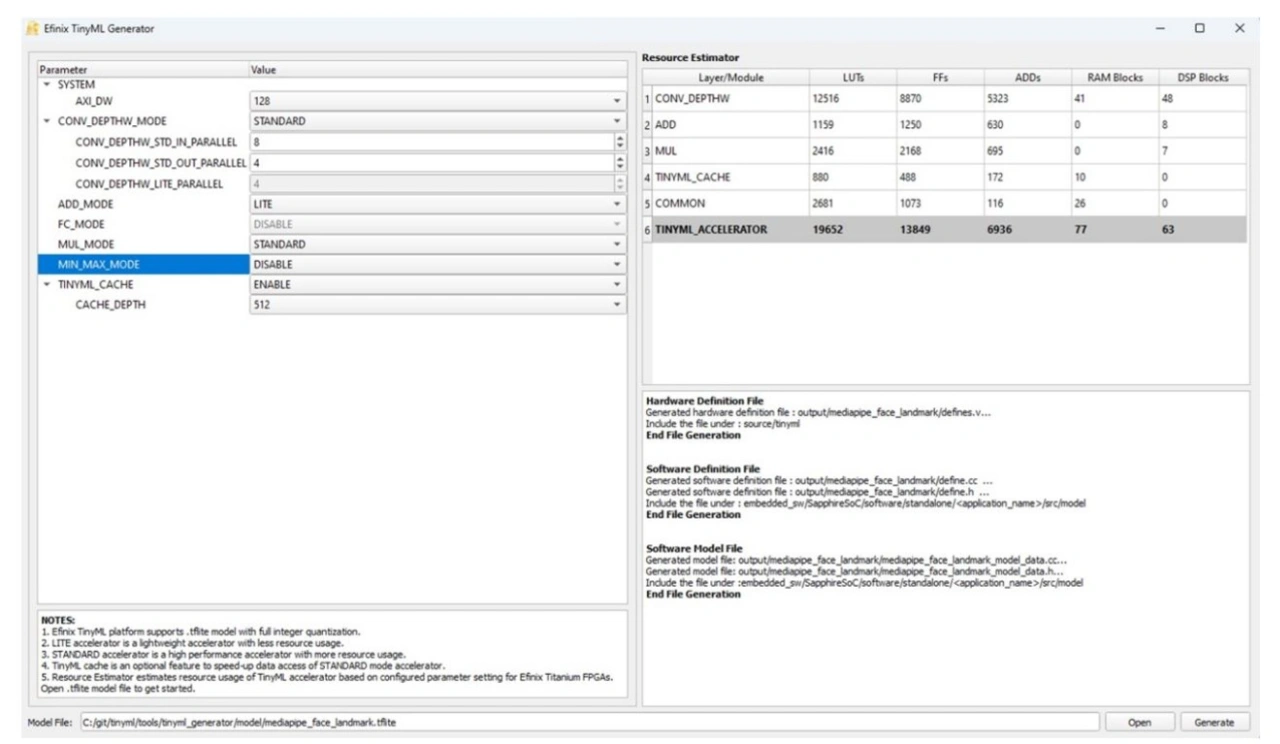

Für die RISC-V-basierten KI Lösungen von Efinix können Daten aus Tensorflow Lite als Microcontroller-Output extrahiert werden. Diese Daten können in das TinyML-Tool geladen werden, um dort die verschiedenen Beschleunigungsmöglichkeiten anzuwenden.

Die Lite Beschleunigung basiert auf Custom Instructions des RISC-V-Cores. Hierbei werden für die verschiedenen Layer im neuronalen Netzwerk kundenspezifische Funktionen hinterlegt, die eine schnellere Abarbeitung gewährleisten als ein Standarddurchlauf durch den RISC-V Prozessor. Diese Funktionen sind in einer Library hinterlegt, das bedeutet, dass man im entsprechenden C-Code keine Änderungen durchführen muss, um eine Beschleunigung zu erreichen.

Ist die Beschleunigung durch Custom Instructions nicht ausreichend, kann die Standard-Beschleunigung ausgewählt werden. Diese hat zwar eine höhere FPGA-Auslastung zur Folge, aber erreicht auch eine höhere Beschleunigung. Um ein Optimum im Design zu finden, werden automatisch die benötigten Ressourcen im TinyML-Tool angezeigt, die die entsprechende Funktion/Beschleunigung benötigt.

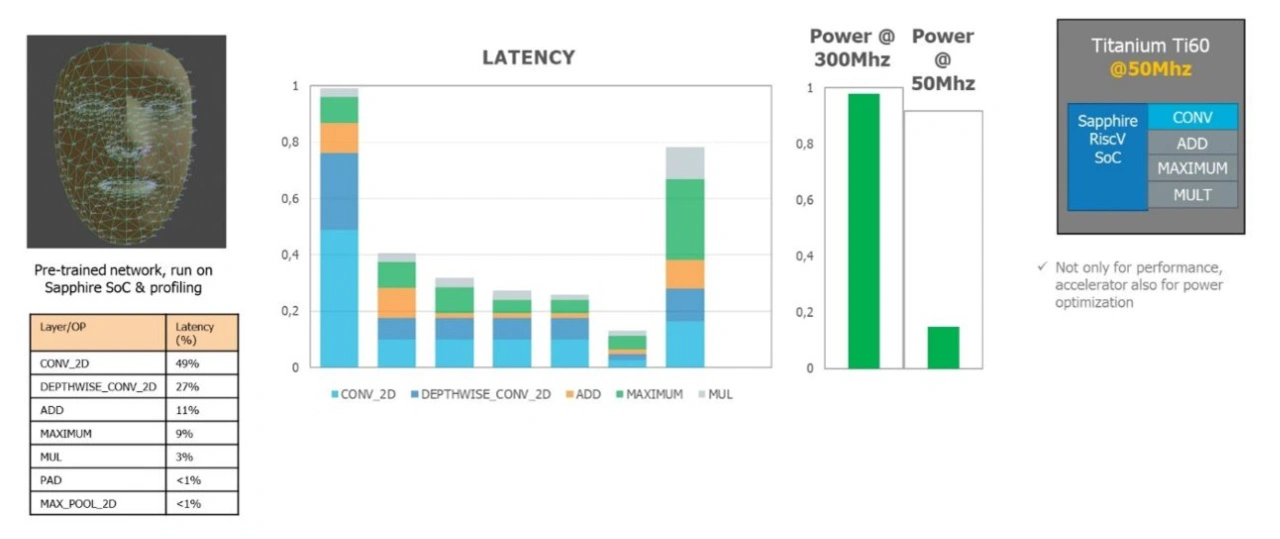

Als Beispiel dient eine Gesichtsmasken-Anwendung. Der RISC-V wurde im Ti60 als Soft-IP implementiert und läuft mit 300 MHz. Lässt man die Funktion ausschließlich auf dem RISC-V ablaufen, wurde diese Latenz auf 1 gesetzt. Durch die verschiedenen Optimierungen konnte eine Beschleunigung erreicht werden, so dass nur noch 10 Prozent der ursprünglichen Latenz benötigt wird. Neben der Beschleunigung verspricht dieser Ansatz auch eine verringerte Leistungsaufnahme. Denn der Prozessor kann bei gleicher Latenz nur noch mit 50 MHz getaktet werden. Die komplette Anwendung benötigt weniger wie 500 mW im Ti60 Baustein bei der niedrigsten Latenz.

Portiert man dieses Design z.B. auf ein Titanium-FPGA mit einem festverdrahteten Quad RISC-V, kann der Prozessor mit 1GHz getaktet werden, sowie weitere Speicherschnittstellen hinzugefügt werden, um eine noch größere Beschleunigung für die Anwendung zu erreichen.

Um ein Gefühl für größere Anwendungen zu bekommen, wurde hier ein Beispiel durch gerechnet, das folgende Merkmale ausweist:

- Logik Zellen: 300000

- Register: 250000

- Systemfrequenz: 450 MHz

- Memory: 200 Mb

- DSP-Blöcke: 1000

- PLL : 1x

- Speicher Schnittstelle: LPDDR4x bei 3000Mbps (50% read, 50% write)

- RISC-V Quad Core : 1 GHz

- SERDES: PCI-Express Gen4 x4

Die gesamte Verlustleistung beträgt typischerweise ca. 6 W (Power Estimator v0.6 Ti375). Ein Blick auf die Werte von herkömmlichen FPGAs zeigt, dass Efinix hier deutlich punkten kann.

Software

Die Software-Umgebung für den RSIC-V sowie die Software für die FPGA-Entwicklung stehen kostenlos zur Verfügung und können von der Support-Webseite heruntergeladen werden.

Beide Software-Umgebungen unterstützen Linux (RHE x86-64 V8.0 and later, Ubuntu x86-64 V18.04 or later) sowie Windows 10 (64) und größer. Selbst bei unserem aktuell größten Baustein(Ti375) benötigt unsere Software-Umgebung nicht mehr als 16 GB.

Autor:

Maximilian Werner ist FAE EMEA bei Efinix