Efinix

Schnell, energiesparend, klein und schlau

Efinix bietet mit seiner Quantum-Architektur kompakte, stromsparende FPGAs und SiPs für KI- und Edge-Anwendungen. Die Titanium-Familie kombiniert geringe Verlustleistung, hohe Auslastung und KI-Beschleunigung mit RISC-V und Standard-Tools wie TensorFlow Lite – effizient, flexibel, kostenlos.

Kleiner, intelligenter und leistungsfähiger, das sind die Anforderung für viele Systeme. Doch alles gleichzeitig zu erreichen, ist oft nicht so einfach, denn ein Mehr an Leistungsfähigkeit ist auch oft mit höherer Verlustleistung gekoppelt und die daraus entstehende Abwärme kann nicht mehr an die Umwelt abgegeben werden.

Mit Künstlicher Intelligenz (KI) werden die Systeme zwar immer intelligenter, aber auch KI benötigt sehr viel Rechenleistung, um die Ergebnisse schnell zur Verfügung zu stellen, was die Verlustleistung ebenfalls in die Höhe treibt. Die KI in die Cloud auszulagern, wiederum widerspricht der Forderung nach schnellen Reaktionszeiten des Systems. Deswegen müssen diese System vor Ort direkt die KI-Prozesse ausführen. GPUs werden in diesen Applikationen sehr häufig benutzt, haben aber das Problem einer sehr hohen Verlustleistung sowie hoher Kosten. Herkömmliche FPGAs sind zwar etwas besser in der Verlustleistung, sprengen aber auch oft das Budget.

Efinix hat sich diesem Problem angenommen. Hierzu zwei Ansätze, wie man mit FPGAs kleine, intelligente und leistungsfähige Systeme entwickeln kann. Die folgenden Beispiele sind aus der Titanium Familie.

Kleine Gehäuse

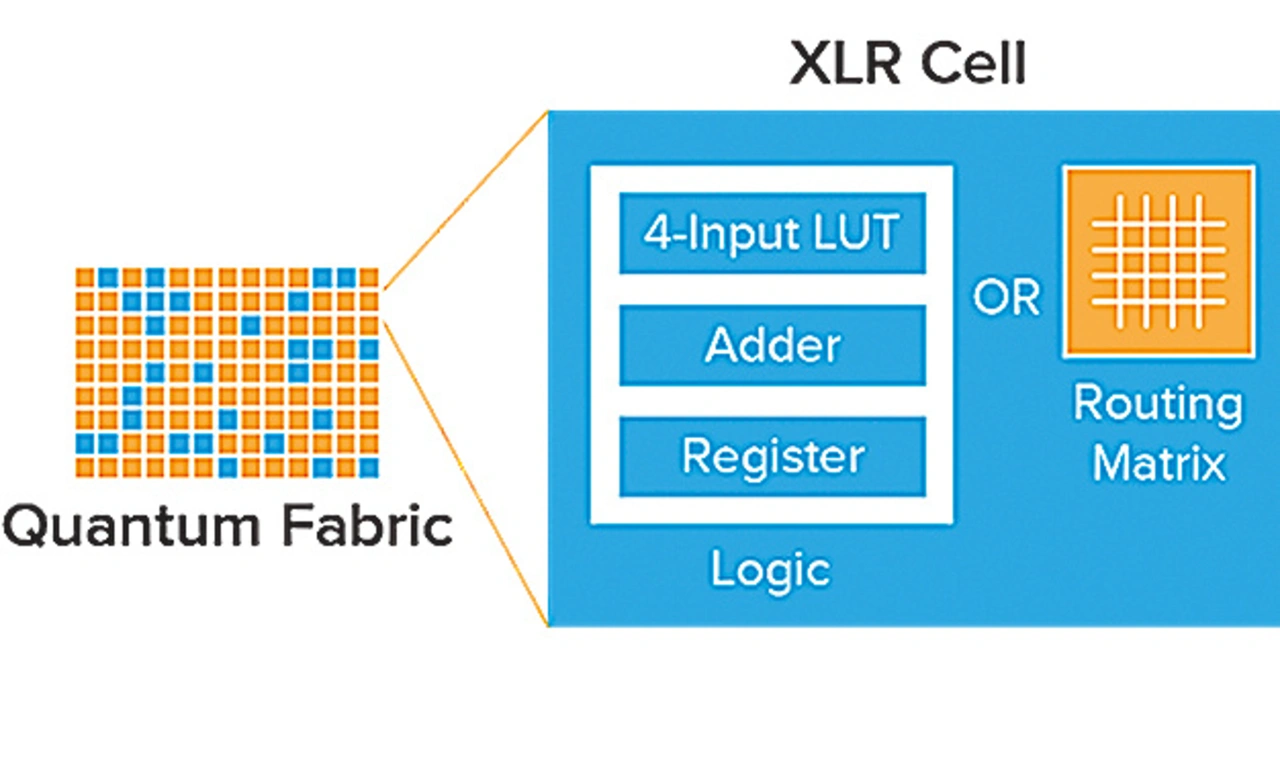

Kleine Gehäuse (und damit eine kleine Chip-Fläche) geben Wärme schlechter ab als große Gehäuse, deswegen können kleine Gehäuse nur bei Bausteinen zur Verfügung gestellt werden, die entsprechend wenig Verlustleistung produzieren. Herkömmliche FPGAs sind nicht für geringe Verlustleistung bekannt. Müssen sie trotzdem eine etwas geringere Verlustleistung aufweisen, werden die geforderten Systemfrequenzen nicht mehr erreicht. Dies liegt an der herkömmlichen FPGA-Architektur, die vor ca. 35 Jahren eingeführt wurde und Logikzellen sowie Routing Ressourcen aufweist. Damit eine Verbindung gewährleistet werden kann, auch wenn der Baustein zu 75 Prozent ausgelastet ist, werden sehr viele Routing-Ressourcen benötigt, welches die Die Fläche stark vergrößert. Zwar können die Bausteine höher ausgelastet werden, was aber wiederum auf Kosten der Systemfrequenz geht, weil jetzt nicht mehr eine direkte Verbindung der Signale gewährleistet werden kann. Es müssen Umwege in Kauf genommen werden, welches die Systemfrequenz beeinträchtigt. Efinix setzt genau hier an.

Jobangebote+ passend zum Thema

Efinix hat mit seiner Quantum-Architektur einen Weg gefunden, dass die FPGA-Zellen Routing und Logik gleichzeitig zur Verfügung stellen können. Mit diesem Ansatz können Routing-Ressourcen in den Bereichen zur Verfügung gestellt werden, an denen sie benötigt werden. Dieser Ansatz ist wesentlich effizienter und macht es möglich die gleichen Logikressourcen auf weniger als die Hälfte der Fläche von herkömmlichen FPGAs in der gleichen Silizium-Struktur zur Verfügung zu stellen. Dieser Ansatz hat neben der Silizium Fläche auch einen sehr großen Einfluss auf die Verlustleistung sowie die Auslastung des FPGAs. Die Efinix FPGAs können über 90 Prozent ausgelastet werden, ohne einen Nachteil in der Systemfrequenz in Kauf nehmen zu müssen.

Ein gutes Beispiel bei Efinix für kleine Gehäuse ist das Ti60-FPGA. Dieser wird als Wafer Level Chip Scale BGA 64 angeboten in einer Größe von 3,5 x 3,4 mm, was in etwa der Die-Größe entspricht. Vergleichen Sie diese Größe mit anderen Anbietern und wie gesagt: diese kleinen Gehäuse sind nur möglich, wenn die FPGAs stromsparend sind, da die Wärme bei kleineren Gehäusen schlechter abgeleitet werden kann.

System in Package (SiP)

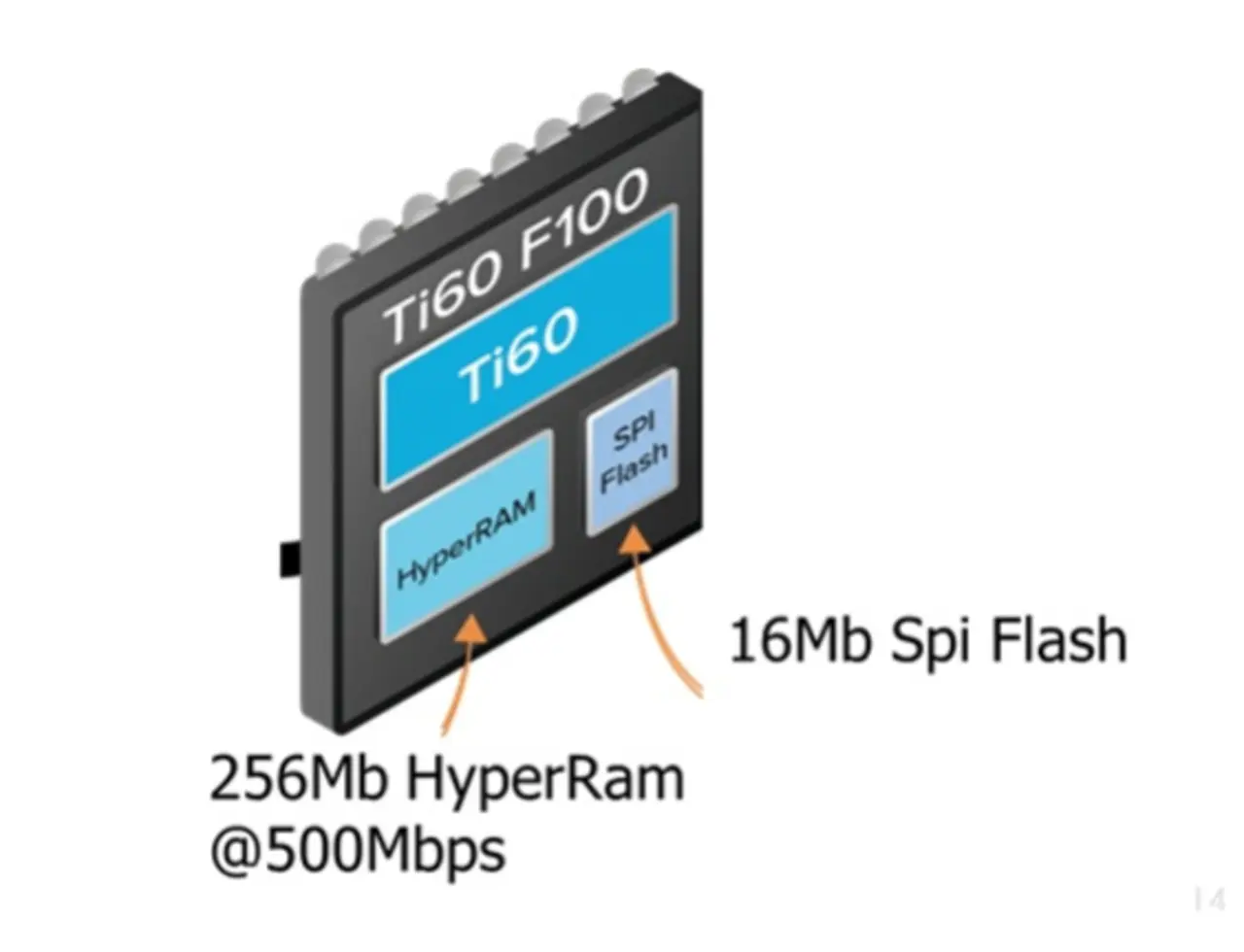

Auch bei einem »System in Package«-Ansatz sind ein kleines Die sowie eine geringe Verlustleistung wichtig, da die zusätzlichen Bausteine/Funktionen, die im gleichen Gehäuse sitzen, ebenfalls Verlustleistung erzeugen. Auch hier ein Beispiel aus der Titanium Familie mit dem Ti60.

In diesem BGA100 Gehäuse mit einer Größe von 5,5 x 5,5 mm² sind FPGA mit 60K LE (Logikelemente) sowie ein HyperRam mit 256 Mb und ein 16 Mb SPI-Flash integriert. Das HyperRam hat einen 16-bit-Anschluss und kann mit 500 Mbps pro Datenleitung betrieben werden. Im 16 Mb SPI-Flash lassen sich zwei komprimierte Bitstreams hinterlegen, so dass auch der »Golden Image«-Ansatz unterstützt werden kann. Dieser ist für Systeme wichtig, die im Feld programmiert werden sollen, damit im Fehlerfall noch auf ein intaktes Image zurückgegriffen werden kann.

Dieser Ansatz ist zum Beispiel für 1-GE-Kameras interessant, da auch MIPI-Schnittstellen bis 1,5 Gbps über die High Speed I/Os (HSIO) zur Verfügung stehen. Aber auch weitere Systeme sind denkbar, in denen der Speicher als Speicher für den RISC-V benutzt wird. Der benötigte HyperRam Controller IP Core ist im IP-Catalog enthalten und kann entsprechend den Anforderungen konfiguriert werden.

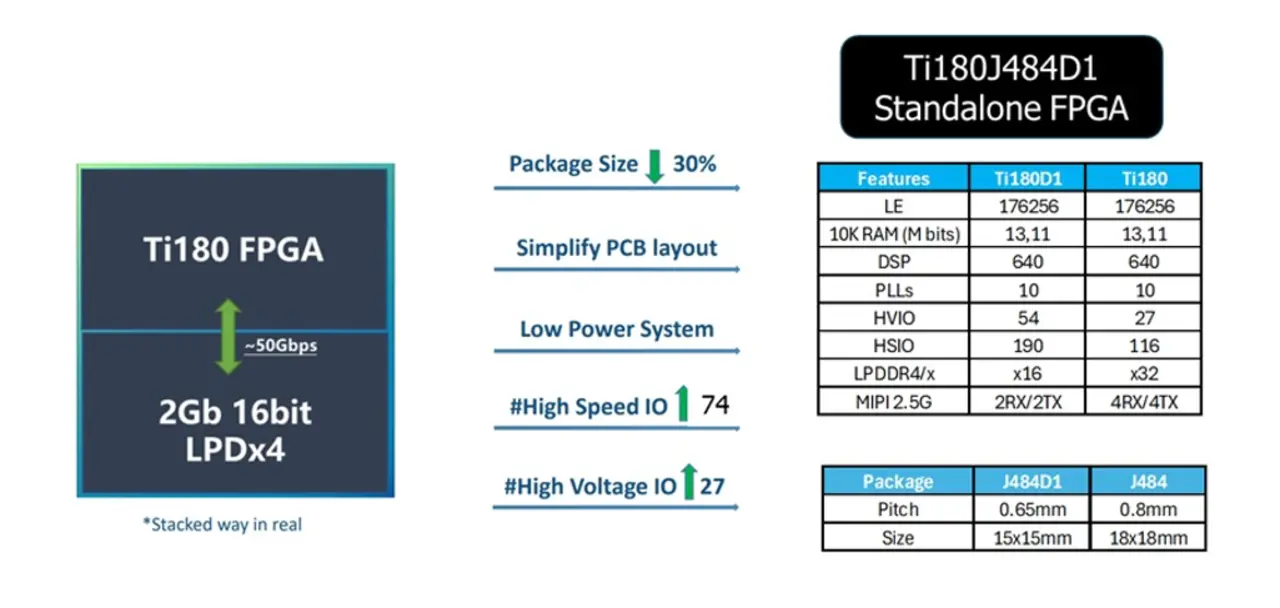

Mit diesem SiP stößt man bei höherwertigen Applikationen oft an Grenzen bei den FPGA- und Speicherressourcen. Deswegen hat Efinix jetzt ein weiteres SiP zusammengestellt. Dieser basiert auf dem Ti180 und hat einen LPDDR4X-Speicher in das gleiche Gehäuse integriert. Der LPDDR4X-Speicher ist mit 16 Bit angeschlossen und kann mit bis zu 3 Gbps betrieben werden. Es stehen 2 Gb Speicher zur Verfügung. Das herkömmliche Gehäuse hat einen Pitch (Pin-Abstand) von 0,8 mm und eine Größe von 18 x 18 mm². Das SIP 484 Gehäuse hat einen 0,65-mm-Pitch und konnte somit auf 15 x 15 mm² verkleinert werden. Auch ein Layout des LPDDR4x auf dem PCB (Leiterplatte) kann eingespart werden, was die Anzahl der PCB-Lagen reduziert sowie das PCB-Layout beschleunigt, denn ein LPDDR4X-Layout auf dem PCB ist häufig sehr komplex. Auch hier ist natürlich eine geringe Verlustleistung die Basis dieses SIP Ansatzes ,da hier der LPDDR4X Speicher einiges an Verlustleistung hinzufügt.

Durch das integrieren des Speichers in das Gehäuse konnte die Anzahl der verfügbaren USER I/Os erhöht werden. Von 116 HSIOs + 27 HVIOs auf 190 HSIOs + 54 HVIOs. Weiterhin stellt dieses System zwei MIPI-Schnittstellen (RX und TX) zur Verfügung, die bis zu 4 x 2,5 Gbps unterstützen, sowie die HSIOs, die LVDS/MIPI-Schnittstellen mit bis zu 1,5 Gbps ermöglichen.

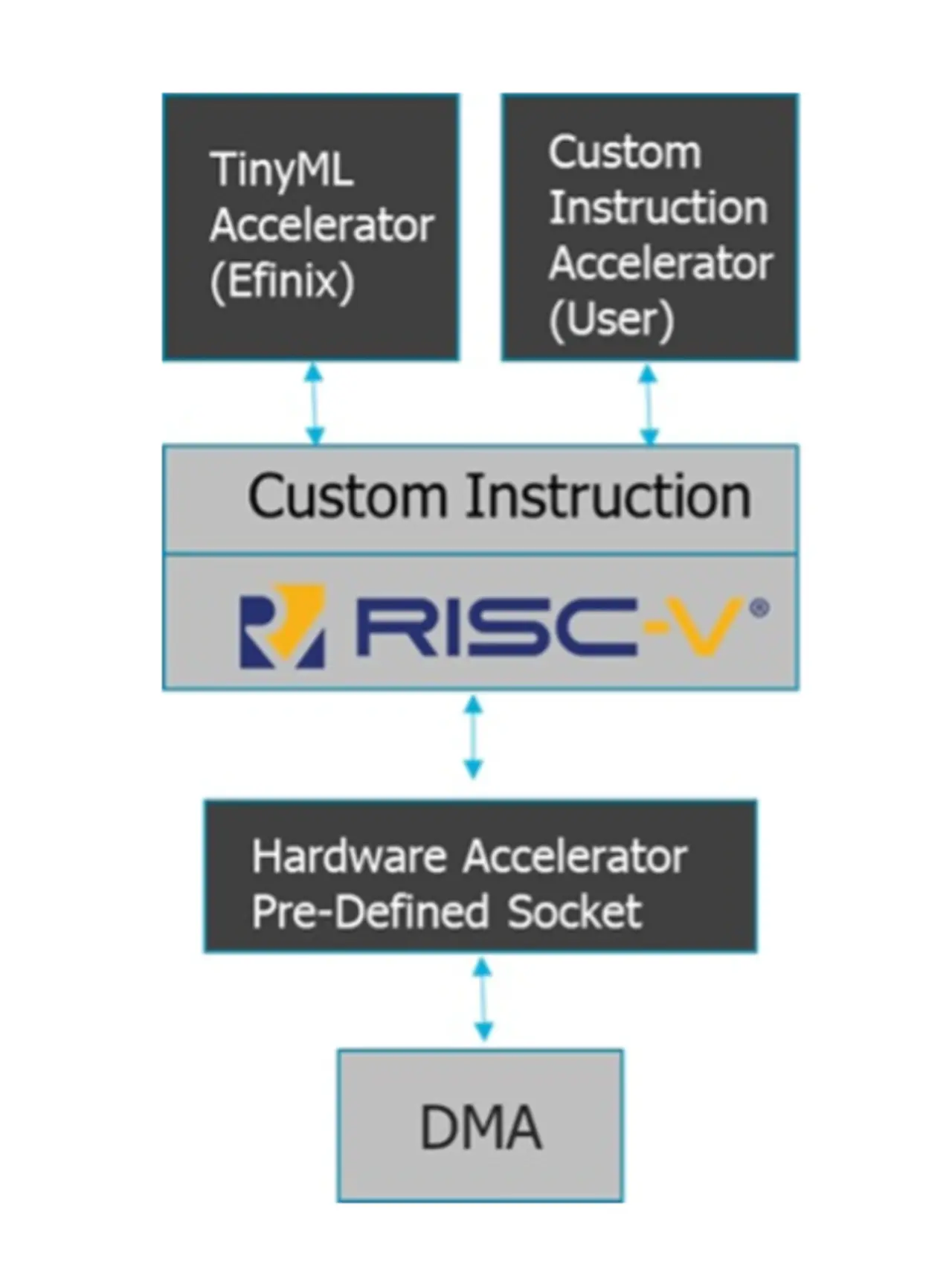

Die System Frequenz des Speichers musste auf 2,5 Gbps im industriellen und auf 3 Gbps im kommerziellen Speedgrade limitiert werden, um die Verlustleistung zu begrenzen. Somit ist diese Lösung optimal geeignet, um z.B. 10/20G USB-Kameras zu entwickeln, die einen Anschluss an einen FX10/20 von Infineon benötigen. Auch für KI-Anwendungen stellen die SiPs eine sehr kompakte Lösung dar, da die KI Algorithmen auch den schnellen internen Speicher benutzen können. Für diese KI-Lösungen im Edge hat Efinix seinen eigenen KI-Ansatz basierend auf einem RISC-V entwickelt, bei dem zur Beschleunigung die »Custom Instructions« der RISC-V-Architektur benutzt werden können oder eine DMA-Funktion, um höhere Beschleunigungen zu erreichen, die mithilfe der FPGA Ressourcen möglich sind.

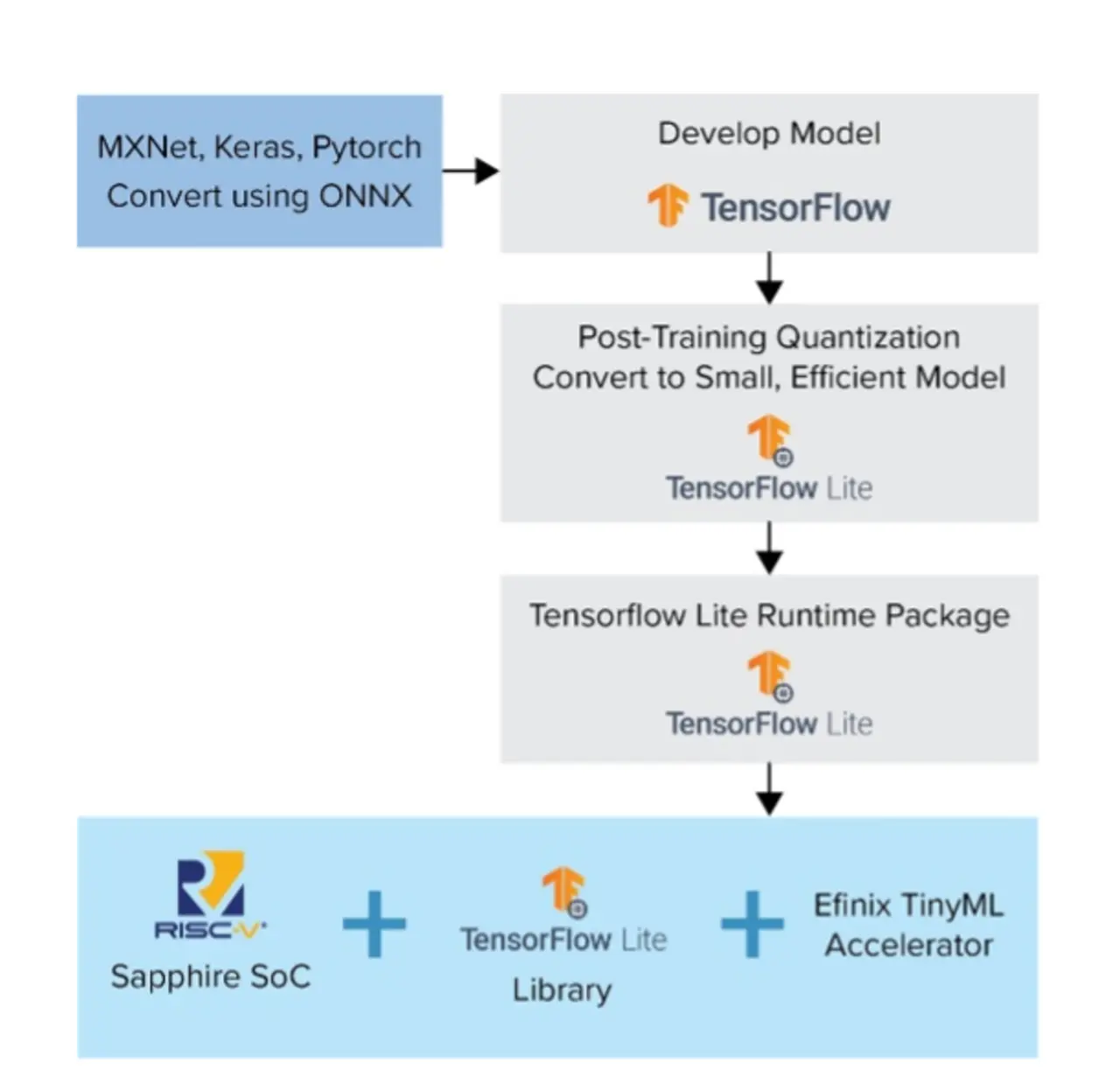

Der KI-Flow basiert auf den Standard KI Tools wie TensorFlow und Tensorflow Lite, bei denen man die trainierten Modelle exportieren und in den TinyML flow bei Efinix einlesen kann. Im Tiny ML Tool können die einzelnen Layer des Neuronalen Netzwerkes über »Custom Instruction« oder DMA-Mode beschleunigt werden, je nach Bedürfnissen der Applikation.

Mithilfe von KI können heute Systeme im Edge auf eine sehr effiziente Art und Weise intelligent gemacht werden. Dies bedingt aber auch, dass KI auf kleiner Fläche und mit geringer Verlustleistung für die Edge-Applikationen realisiert werden kann. Immer wichtiger für die Anwender wird auch die Benutzung von Standards in der Realisierung. Deswegen setzt hier Efinix auf die Standard RISC-V Architektur sowie auf die Benutzung der Standard Tools wir TensorFow Lite. Darüber hinaus ist die KI-Lösung kostenlos verfügbar und jeder kann diese Lösung ohne zusätzlichen Kosten in Efinix Bausteine Implementieren.

Für die Implementierung der Lösungen in die Efinix-FPGAs steht die Efinity Software zur Verfügung. Auch hier gilt: Die Software steht für registrierte Kunden kostenlos zur Verfügung. Efinity unterstützt VHDL (bis 2008 und 2019 Interface), Verilog sowie System Verilog. Die Timing-Anforderungen werden über SDC-Files spezifiziert und überprüft. Die Efinity Software stellt nur sehr wenig Anforderungen an den PC, der mit Linux oder Windows betrieben werden kann. Der Speicherbedarf liegt lediglich bei 16 MB für die Ti375-Bausteine (375K LE). Und die Durchlaufzeiten sind extrem hoch und die geforderte Systemfrequenz lässt sich einfach erreichen.

In der heutigen Zeit bedingen neue Ansätze auch neue Methoden. Die Basis ist bei Efinix die neue Quantum Architektur, die die kleinen und stromsparenden SiPs ermöglichen. Weitere werden folgen.