Field Programmable Gate Array

GateMate Integrated Logic Analyzer

Cologne Chip stellt Entwicklern einen speziell für GateMate FPGAs entwickelten Integrated Logic Analyzer zur Verfügung, der mit umfangreichen Funktionen sowohl die Entwicklung des als Gateware bezeichneten FPGA-Designs als auch die Implementierung des GateMate FPGAs in komplexe Systeme erleichtert.

Ein integrierter Logikanalysator, kurz ILA, wird direkt als Gateware in einem FPGA (Field Programmable Gate Array) implementiert und ermöglicht die Auswertung interner Signalverläufe der zu testenden DUT-Gateware (Design Under Test) direkt im FPGA. Dazu wird die ILA-Gateware mit den zu analysierenden DUT-Signalen verbunden und zusammen mit der DUT-Gateware auf einem FPGA konfiguriert. Dies ermöglicht Entwicklern, das Verhalten der internen Signalverläufe ihrer Gateware unter realen Bedingungen in Echtzeit zu überwachen, ohne den normalen Betrieb des DUT zu beeinträchtigen. Auf diese Weise können tiefe Einblicke gewonnen werden, um die Funktionalität komplexer Systeme besser zu verstehen und zu optimieren.

Jobangebote+ passend zum Thema

Gateware

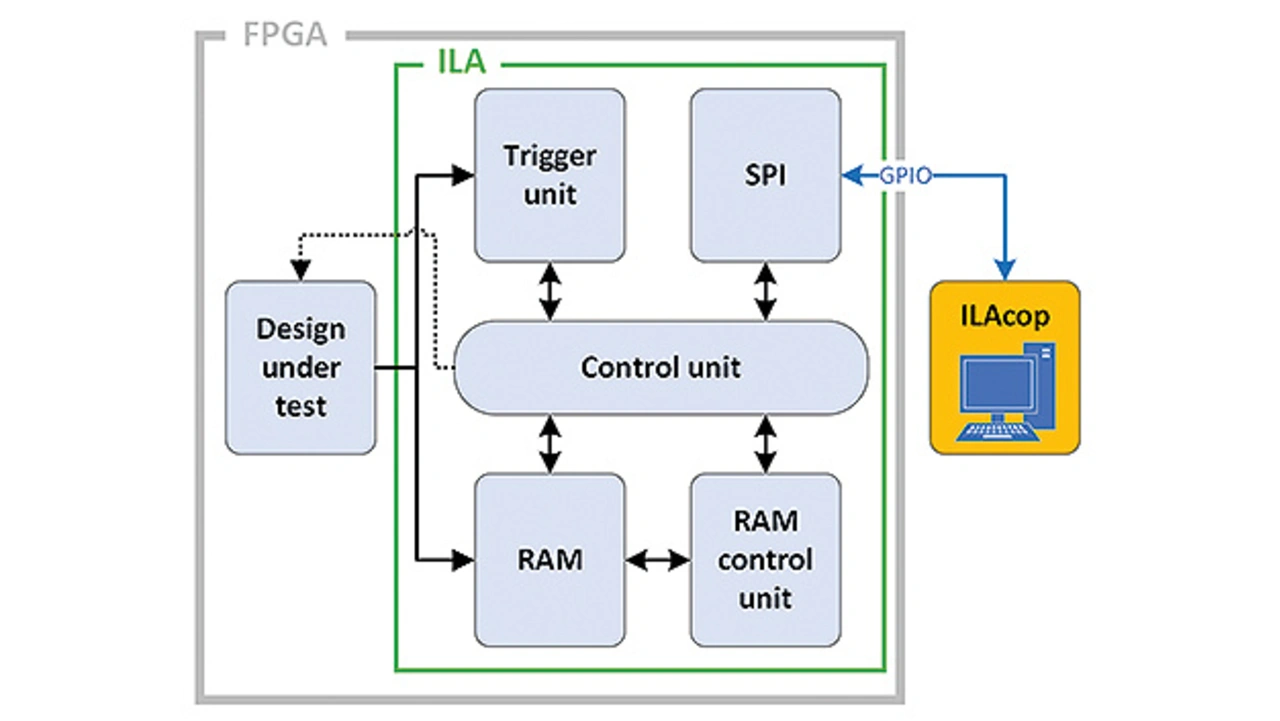

Die Gateware des ILA nutzt mit den in Bild 1 gezeigten Komponenten effizient einen minimalen Teil der im FPGA zur Verfügung stehenden Hardwareressourcen. Dies erlaubt die parallele Konfiguration des ILA mit einem ressourcenintensiven DUT auf dem FPGA, ohne dessen regulären Betrieb zu beeinträchtigen.

Die vom Benutzer ausgewählten Testsignale werden zu einem Testvektor zusammengefasst und sind sowohl mit dem RAM als auch mit der Trigger-Einheit verbunden. Nachdem der Testvektor durch eine vom Benutzer einstellbare Anzahl von Registerstufen synchronisiert wurde, gelangt er direkt an den Dateneingang des RAM. Das RAM des ILA ist in seiner Datenbreite und -tiefe flexibel und wird im FPGA aus Block-RAM-Zellen konstruiert. In der Trigger-Einheit wird der Testvektor auf die eingestellte Trigger-Bedingung hin überprüft.

Die als ILAcop (ILA control program) bezeichnete Anwendersoftware wird auf dem Betriebssystem des Anwender-PCs installiert und ermöglicht zum einen die Konfiguration der ILA-Gateware vor der Implementierung und zum anderen die Steuerung der ILA-Gateware während des Analyseprozesses über die SPI-Schnittstelle (Serial Peripheral Interface). Der GateMate ILA wurde so entwickelt, dass die Kommunikation des Analyseprozesses über die gleiche Hardwareschnittstelle erfolgen kann, über die auch die Konfiguration des FPGAs erfolgt.

Die Steuereinheit der ILA-Gateware koordiniert die Kommunikation zwischen dem FPGA und ILAcop über die SPI-Schnittstelle. Sie konfiguriert die einzustellenden Trigger, hält das DUT ggf. im Reset-Zustand, startet den Aufnahmeprozess und sorgt dafür, dass die zu analysierenden Signale korrekt übertragen werden.

Die RAM-Steuereinheit ist dafür verantwortlich, dass die Abtastwerte des Testvektors für die definierte Zeitspanne um das eingestellte Trigger-Ereignis nach der Erfassung zur Verfügung stehen.

Workflow

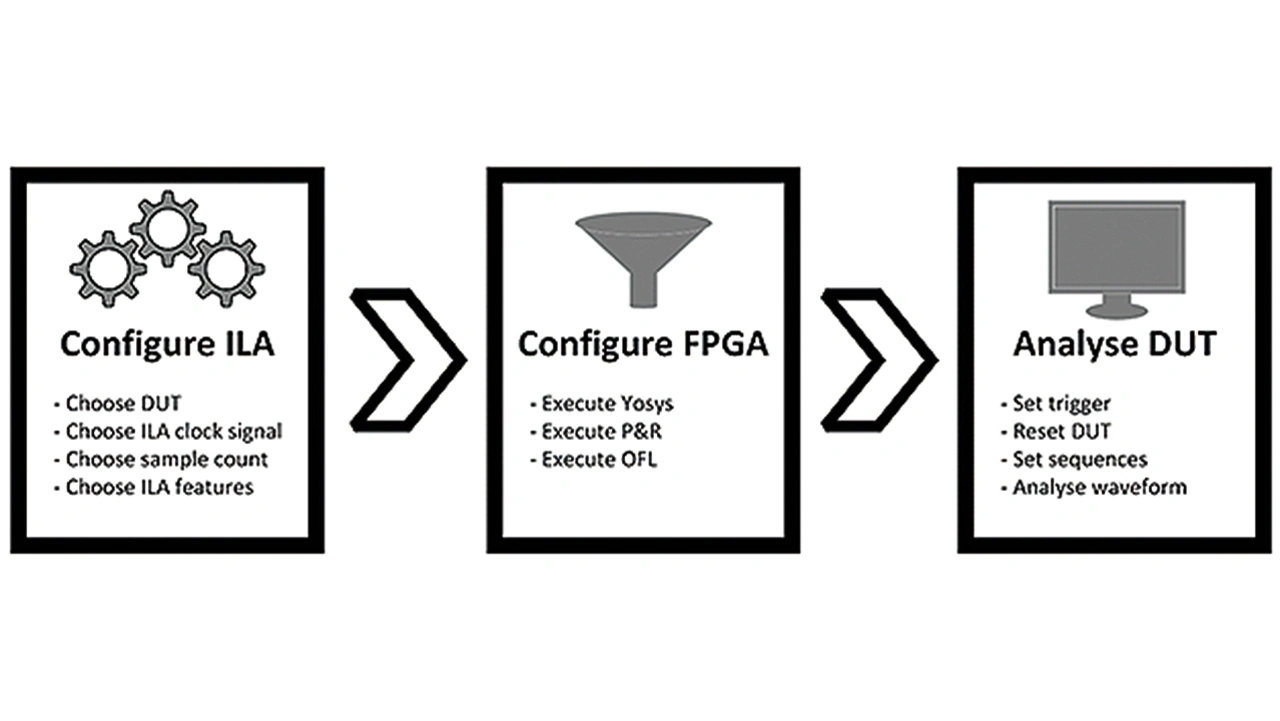

Der gesamte Workflow wird durch das Python-Programm ILAcop gesteuert (Bild 2). Als erstes muss die Gateware des ILA für das individuelle DUT konfiguriert werden. Konfigurationen wie die Taktquelle des ILA, die Auswahl der zu testenden Signale sowie die Dauer der Datenerfassung sind von dem zu analysierenden DUT abhängig und können neben weiteren Funktionen individuell eingestellt werden.

Im nächsten Schritt wird die abstrakt beschriebene Gateware von ILA und DUT, die zu diesem Zeitpunkt bereits über verschiedene Signale miteinander verbunden sind, auf dem FPGA konfiguriert. Zunächst muss die gesamte Gateware mithilfe von Yosys, einem leistungsfähigen Open Source Synthesetool, synthetisiert werden. Während des Syntheseprozesses wird die Schaltung optimiert und auf die spezifischen Hardwarekomponenten des GateMate FPGA abgebildet.

Anschließend erfolgt die Platzierung und Verbindung der Schaltungselemente auf dem FPGA durch die proprietäre Software P&R von Cologne Chip. Diese Software ist speziell für die effiziente Handhabung des FPGA-Layouts entwickelt und erzeugt eine Konfigurationsdatei, die alle für die Gateware benötigten Hardwareelemente im FPGA adressiert und konfiguriert.

Die abschließende Übertragung der Konfigurationsdaten in das FPGA erfolgt mit dem OpenFPGAloader, einem weiteren Open Source Tool, das speziell das Laden von Konfigurationsdateien auf eine Vielzahl von FPGA-Geräten unterstützt.

Ist das FPGA erfolgreich konfiguriert, beginnt die Kommunikation zwischen ILAcop und ILA-Gateware. Zur Laufzeit kann der Benutzer über ein Terminal die Trigger-Bedingungen festlegen, den Reset-Zustand des DUT steuern und die Messdatenerfassung starten.

Nach Abschluss der Messdatenerfassung und vollständiger Übertragung aller Daten aus dem internen Speicher des FPGA wird der zeitliche Verlauf der aufgezeichneten Signale rekonstruiert und in einer VCD-Datei (Value Change Dump) gespeichert. In einem separaten Prozess werden die Daten der VCD-Datei automatisch von einer Software in einem Timing-Diagramm visualisiert.

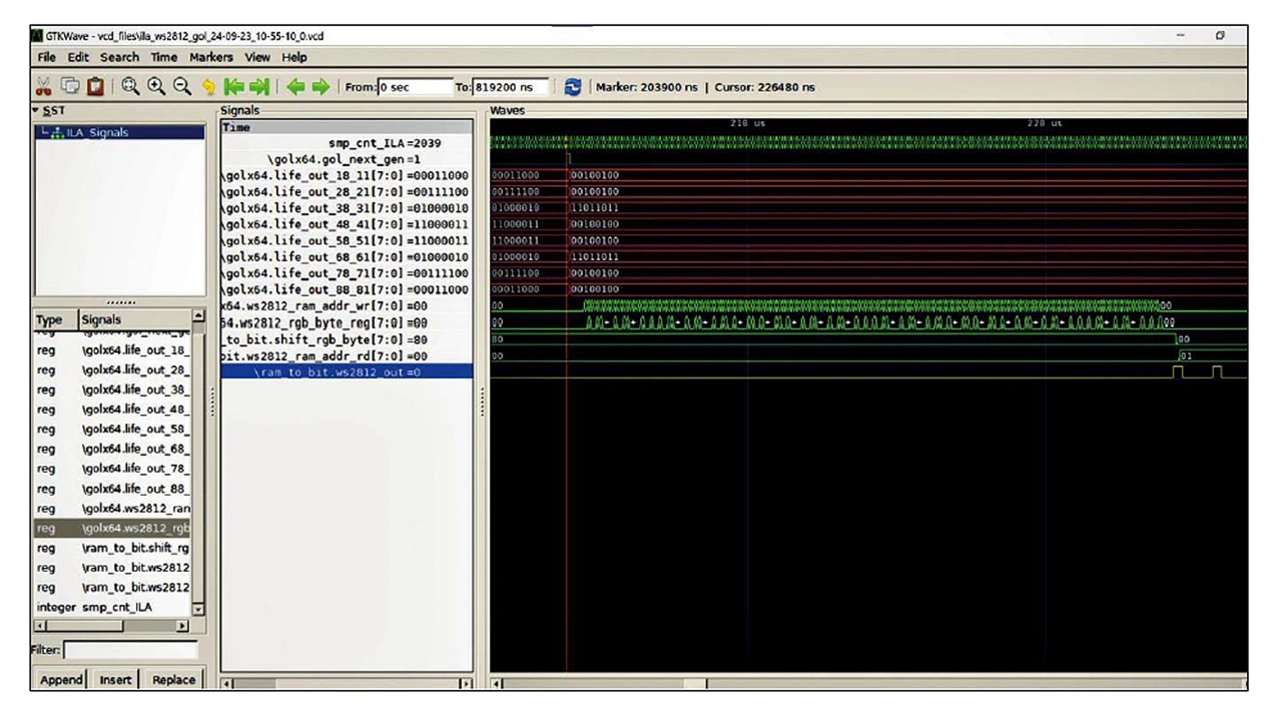

Bild 3 zeigt ein mit GTKWave visualisiertes Beispiel für ein Timing-Diagramm, in dem vom ILA aufgezeichnete Signale eines DUT aus dem FPGA dargestellt werden. Alternativ kann jede andere Software zur Darstellung des Timing-Diagramms mit VCD-Import verwendet werden. In der Signalbezeichnung im Zeitdiagramm steht vor dem Signalnamen, durch einen Punkt getrennt, die Modulhierarchie, in der das Signal im originalen Design zu finden ist. Weitere Informationen zu diesem speziellen Beispiel-DUT befinden sich im öffentlichen Git-Repository des Cologne Chip GateMate ILA im Verzeichnis »gatemate_ila/example_dut/ws2812_gol/«.

ILA-Eigenschaften

Der GateMate ILA zeichnet sich durch die folgenden Eigenschaften aus:

➔ Konfigurations-Wizard: Der Benutzer wird durch die Konfiguration des ILA für die Analyse eines DUT mittels einer intuitiven und einfach zu bedienenden Shell-Prozedur geführt, die Erläuterungen zu allen Konfigurationen bietet.

➔ Umfassende Analyse des DUT-Quellcodes: Das System identifiziert automatisch die Hierarchie des DUT und durchsucht dessen Module, wobei die Namen aller im Design definierten Signale gespeichert werden. Spezielle GateMate-Hardwareelemente, die vom DUT verwendet werden, wie z. B. PLLs oder Block-RAMs, werden identifiziert, sodass eine Konfiguration des ILA nur innerhalb der Hardwaregrenzen des verwendeten FPGAs möglich ist.

➔ Flexible und einfache Auswahl eines Abtastfrequenzsignals: Zur Einstellung der Abtastfrequenz kann das Ausgangssignal einer zusätzlichen PLL mit frei wählbarer Frequenz, ein externes Taktsignal oder ein im DUT definiertes Taktsignal, wie z. B. das Ausgangssignal einer instanziierten PLL, gewählt werden.

➔ Parallele Abtastung von über 1.000 Signalen möglich: Die Signale des DUT werden aus einer hierarchisch organisierten Liste vom Benutzer ausgewählt und in einem Testvektor zusammengefasst. Die maximale Anzahl der Bits des Testvektors und die Anzahl der insgesamt speicherbaren Abtastwerte hängen von den verfügbaren, d. h. nicht vom DUT genutzten Block-RAM-Zellen im FPGA ab. Das CCGM1A1 FPGA verfügt über 32 Block-RAM-Zellen, die mit der ILA Gateware im True Dual Port Mode betrieben werden. Die Anzahl der verfügbaren Adressen und die Datenbusbreite sind variabel konfigurierbar. Die maximal mögliche Datenbreite einer Block-RAM-Zelle im True Dual Port Mode beträgt 40 bit, wobei 1.024 Speicheradressen zur Verfügung stehen. Wenn dem ILA beispielsweise 30 Block-RAM-Zellen eines GateMate FPGAs zur Verfügung stehen, kann ein Testvektor bis zu einer Größe von 1200 bit konfiguriert werden.

➔ Konfiguration des ILA aus einer JSON-Datei: Alle vom Assistenten erstellten Konfigurationen werden in einer JSON-Datei im lesbaren Textformat gespeichert. Dadurch kann der Benutzer bei späteren Aufrufen einfach Änderungen vornehmen, wie z. B. die zu analysierenden Signale ändern. Die Verwendung der JSON-Datei ermöglicht eine schnelle und einfache Konfiguration des ILA. Ein neues DUT kann auch direkt aus einer JSON-Datei konfiguriert werden, was den Konfigurationsprozess erheblich beschleunigt.

➔ Zur Laufzeit rekonfigurierbarer Trigger: Mithilfe der im ILA integrierten Kommunikationsschnittstelle kann die Trigger- Bedingung jederzeit über ein interaktives Shell-Programm vom Benutzerrechner aus geändert und der Erfassungsvorgang auf dem FPGA gestartet oder abgebrochen werden, ohne den Betrieb des DUT zu beeinträchtigen.

➔ Reset-Hold-Funktion: Diese Funktion ermöglicht das Erfassen von Signalen unmittelbar nach dem Verlassen des Reset-Zustandes des DUT. Dabei kann vor der Messdatenerfassung der Reset des DUT beliebig aktiviert oder deaktiviert werden, während unmittelbar beim Starten der Messdatenerfassung der Reset deaktiviert wird.

➔ Benutzerdefinierte Bitmuster als Trigger: Der ILA ermöglicht die Festlegung individueller Trigger-Ereignisse. Es kann ein spezifisches Bitmuster, das über den gesamten Testvektor als erwartetes Trigger-Ereignis eingestellt wird, in hexadezimaler oder binärer Form definiert werden. Dabei lässt sich jedes Bit des Musters als »1«, »0« oder »X« (für »don‘t care«) konfigurieren. Zusätzlich kann ein Trigger auf ein beliebiges Signal gesetzt werden und bei Ereignissen wie einer steigenden oder fallenden Flanke des Signals ausgelöst werden.

➔ Signalanalyse im Timing-Diagramm: Nachdem das definierte Trigger-Ereignis eingetreten ist, kann der zeitliche Verlauf der Signale in einem Zeitdiagramm analysiert werden, wobei die ursprünglichen Namen und Vektorgrößen aus dem DUT im Diagramm verwendet werden.

➔ Konfiguration von Messdatenerfassungssequenzen: Es können Sequenzen mit verschiedenen Auslösebedingungen erstellt werden, die direkt nacheinander ausgeführt werden. Dies ermöglicht die Erfassung von Abtastwerten zu Ereignissen, die in kurzen Zeitabständen aufeinander folgen. Unmittelbar nach dem Empfang der erforderlichen Abtastwerte wird die Aufzeichnung mit der nächsten Trigger-Auslösebedingung gestartet. Jede Aufzeichnung aus diesen Sequenzen wird in einem eigenen Zeitdiagramm dargestellt und gespeichert.

➔ Open-Source: Als Open-Source-Tool bietet der ILA eine hohe Flexibilität und Anpassbarkeit sowie die Möglichkeit zur Weiterentwicklung durch die Community.

Beispielkonfigurationen mit Übersicht zum Ressourcenverbrauch

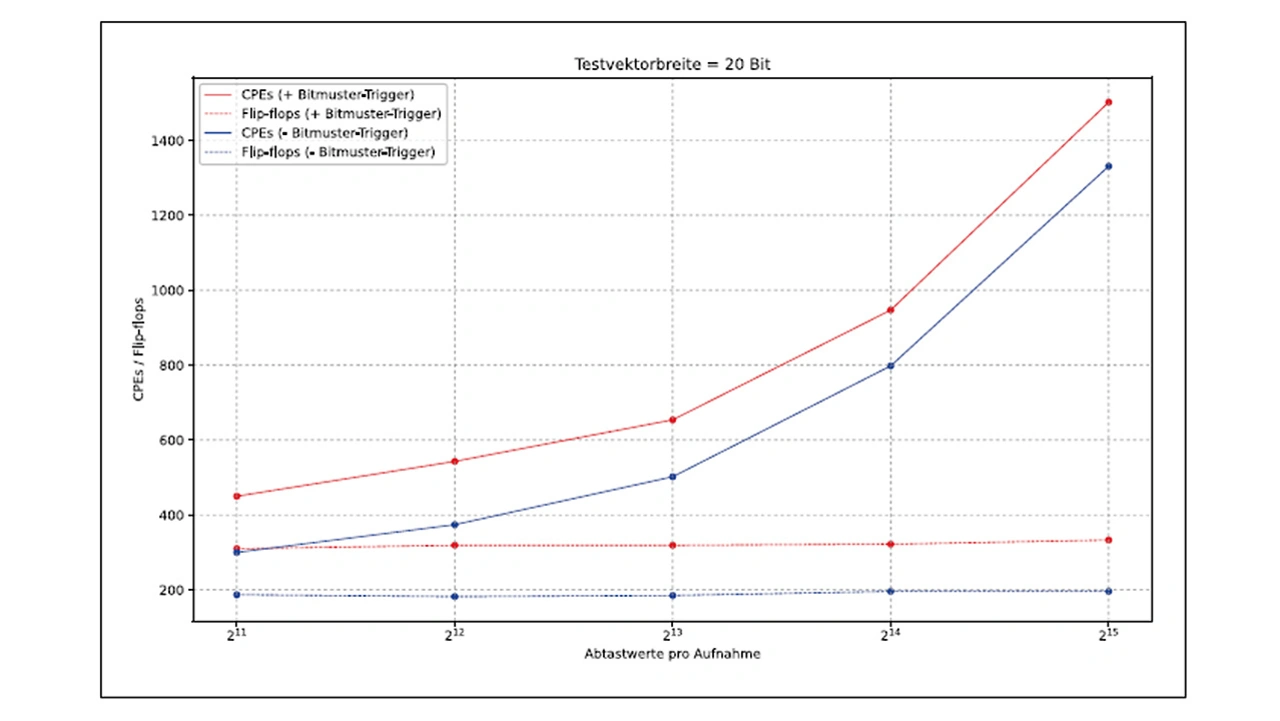

Der Ressourcenverbrauch des ILA ist aufgrund seines generischen Designs variabel und hängt von der Konfiguration ab. Dies umfasst die vom Benutzer eingestellten Funktionen, die Bitbreite des Testvektors und die Anzahl der geforderten Abtastwerte.

Der im Folgenden dargestellte Test wurde auf dem Cologne Chip Evaluation Board V3.1B mit einem CCGM1A1 FPGA durchgeführt. Der CCGM1A1 FPGA verfügt über 20.480 CPEs (Cologne Programmable Elements), die jeweils über einen 8-Bit LUT-Tree für Logikfunktionen und zwei Speicherelemente verfügen, die als Flip-Flop oder Latch verwendet werden können.

Die Analyse des Ressourcenverbrauchs des ILA auf einem CCGM1A1 FPGA zeigt einen besonders geringen Ressourcenverbrauch. Für eine Konfiguration mit einem Testvektor von 8 bit Breite und insgesamt 2048 Abtastwerten pro Erfassung benötigt der ILA nur 235 CPEs, was 1,15 Prozent der Gesamtzahl der CPEs des FPGAs entspricht. Zusätzlich werden 152 Flip-Flops verbraucht, was lediglich 0,37 Prozent der insgesamt verfügbaren Flip-Flops entspricht.

Bild 4 zeigt den Ressourcenverbrauch des ILA bei einer konstanten Testvektorbreite von 20 bit. Die Anzahl der Abtastwerte je Aufzeichnung wird für jeden Prüfpunkt um eine Zweierpotenz erhöht. Es fällt auf, dass die Anzahl der verwendeten Flip-Flops konstant bleibt. Dies liegt daran, dass die vom ILA benötigten Register, mit Ausnahme des Speicheradresszählers, von der Testvektorbreite abhängen. Die zusätzlich benötigten CPEs dienen der Erweiterung des Speichers unter Verwendung der vorhandenen RAM- Blöcke. Während für 2048 Abtastwerte nur ein RAM-Block benötigt wird, erhöht sich der Bedarf bei 32.768 Abtastwerten auf 32 RAM-Blöcke. Diese werden mithilfe von CPEs so konfiguriert, dass sie zusammen wie ein einziger RAM mit 32.768 Speicheradressen funktionieren.

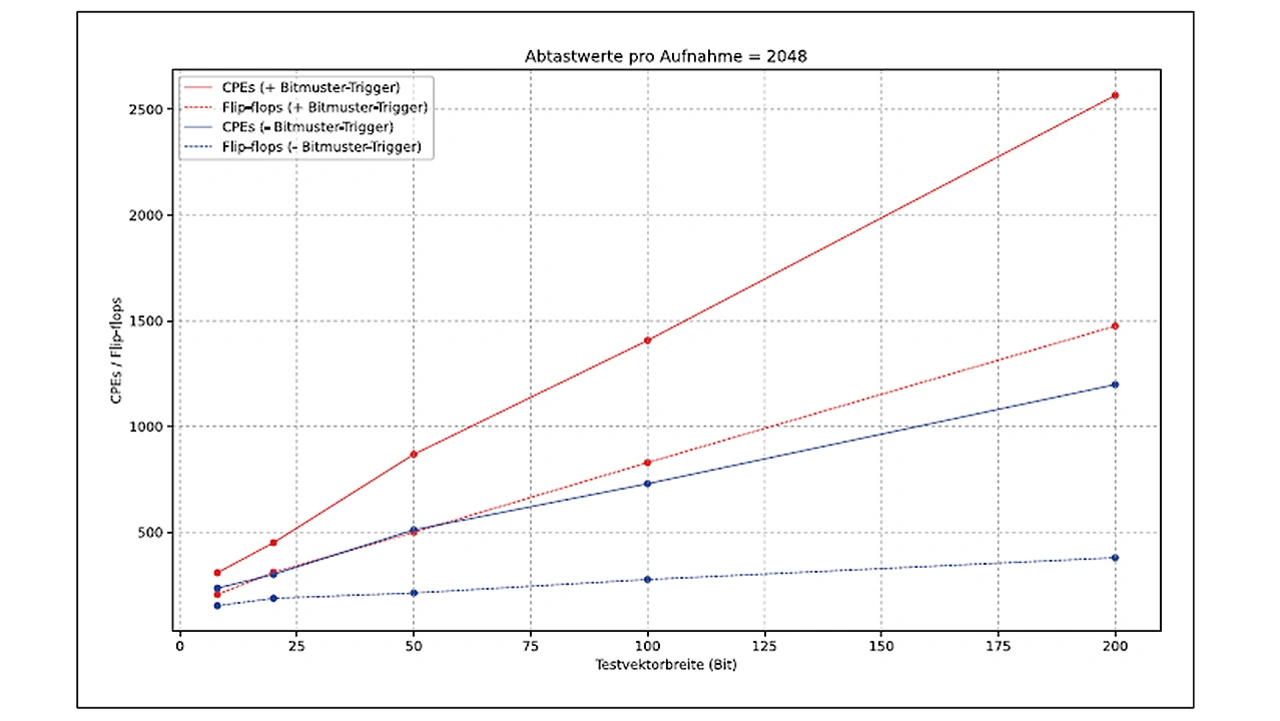

Bild 5 zeigt den Ressourcenverbrauch, wenn die Testvektorbreite erhöht wird, während die Anzahl der Abtastwerte pro Erfassung konstant bleibt. Hierbei ist deutlich zu erkennen, dass der Bedarf an Hardware mit steigender Testvektorbreite nahezu linear zunimmt. Dabei steigt der Hardwareverbrauch mit aktiviertem Bitmuster-Trigger deutlich steiler an.

Fazit

Der GateMate ILA stellt Entwicklern von Gateware für GateMate FPGAs ein nützliches Werkzeug zur Verfügung, das eine gründliche Analyse der Signale des zu testenden Designs in seiner realen Arbeitsumgebung ermöglicht. Besonders hervorzuheben ist sein geringer Hardwarebedarf bei minimaler Konfiguration, der die Implementierung des ILA auch bei sehr begrenzten Hardwareressourcen ermöglicht. Durch eine effiziente Implementierung und den Einsatz von Pipelining-Techniken wird der kritische Pfad der ILA-Gateware gering gehalten. Dadurch werden Analysen auch in hohen Frequenzbereichen möglich.

Mithilfe des Konfigurations-Wizards kann der ILA sehr einfach mit einem beliebigen DUT konfiguriert werden. Mit der Möglichkeit, Konfigurationen schnell in einer JSON-Datei zu erstellen, können fortgeschrittene Benutzer den ILA auch besonders schnell konfigurieren. Cologne Chip bietet aktiven Support für den ILA und entwickelt diesen kontinuierlich weiter. Durch den Open-Source-Ansatz ist die gesamte Community eingeladen, den ILA mitzugestalten oder auf dessen Basis neue Innovationen zu entwickeln.

Der Autor

Dave Fohrn

war während seines Studiums der Technischen Informatik an der TH Köln im Institute of Computer and Communication Technology (ICCT) im Bereich Embedded Systems unter der Leitung von Prof. Dr. Krawutschke tätig. Durch seine unterstützenden Tätigkeiten in der Forschung und Lehre konnte er im Laufe seines Studiums spannende und praxisnahe Projekte umsetzen. Nach seiner Abschlussarbeit mit dem Titel »Entwicklung eines eingebetteten Logikanalysators auf einem Gate-Mate FPGA« bekam er die Möglichkeit, als Embedded Software Engineer in der Forschung und Entwicklung bei Cologne Chip tätig zu werden. In Zusammenarbeit mit Prof. Dr. Krawutschke unterstützt er auch weiterhin die Forschung und Lehre an der TH Köln durch den Einsatz des GateMate FPGA in verschiedenen Projekten.