Klein, schnell, energiesparend

Details zur Quantum-Architektur von Efinix und ihre Vorteile

Fortsetzung des Artikels von Teil 4

Die Titanium XLR-Zelle in Aktion

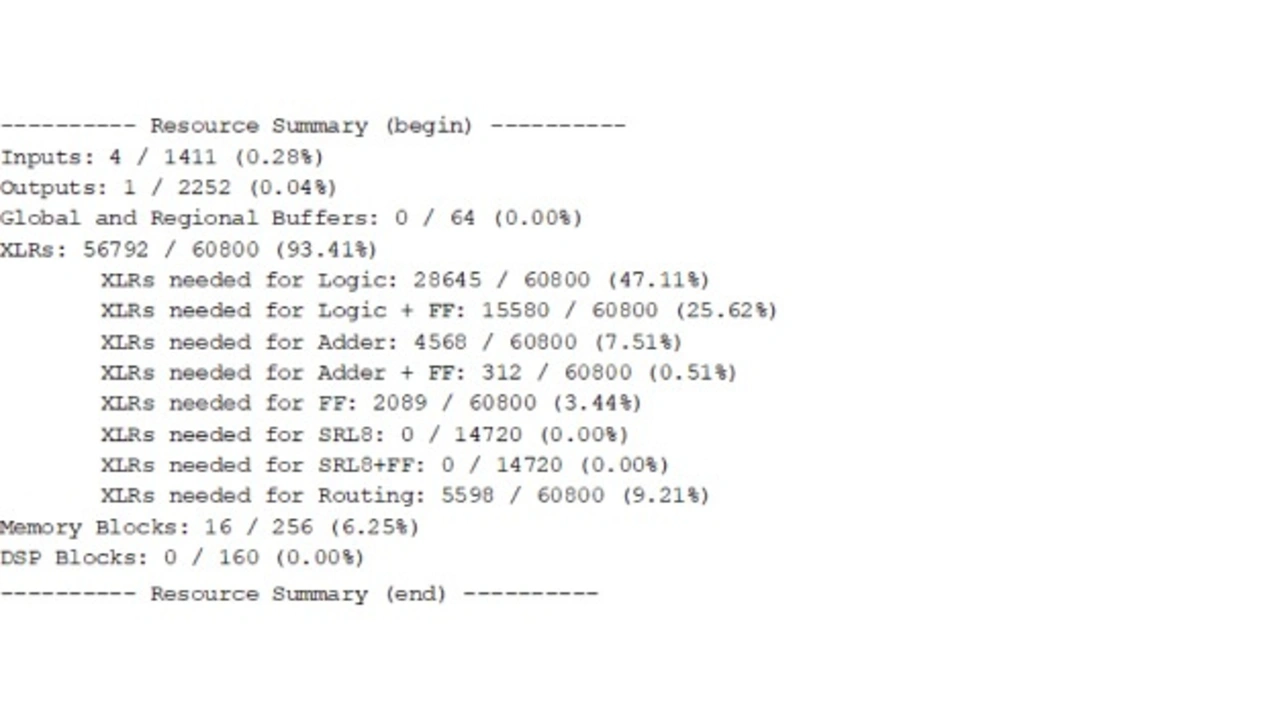

Im Efinity-Placer-Report meldet die Software die Nutzung in XLR-Zellen für die Logik und die Schätzung, die für das Routing benötigt wird. Abbildung 6 ist ein Reportausschnitt, der die Ressourcennutzung für ein 32-Bit-RISC-Prozessor (oc_m1_core) Open-Source-Design zeigt. Dieses Design ist 8-mal eingesetzt und zielt auf das Ti60 FPGA. Das mehrfache Einsetzen von Designs ist eine übliche Methode für FPGA-Hersteller, große Designs zu erstellen, um einen Baustein für Benchmarking und Experimente zu füllen. Das FPGA ist mit über 93 Prozent der verwendeten XLR-Zellen ziemlich vollgepackt und nur etwas mehr als 9 Prozent der verfügbaren XLR-Zellen sind für das Routing reserviert.

Jobangebote+ passend zum Thema

Analyse der Zahlen im Report:

Das Design verwendet 5.598 XLR-Zellen für das Routing, was etwa 60 Prozent der 9.120 XLR-Zellen entspricht, die für das Routing reserviert sind (15 Prozent von 60.800).

Das Design verwendet 51.194 XLR-Zellen für die Logik, was 61.432,8 LEs entspricht.

Es gibt 4.008 ungenutzte XLR-Zellen, die für Logik und Routing verwendet werden können. Wenn wir 15 Prozent der ungenutzten Zellen für das Routing aufheben, bleiben 3.406 (abwärts gerundet) für die Logik übrig. Diese Zahl entspricht 4.087 LEs, das sind etwa 3.500 LEs mehr als im Datenblatt angegeben.

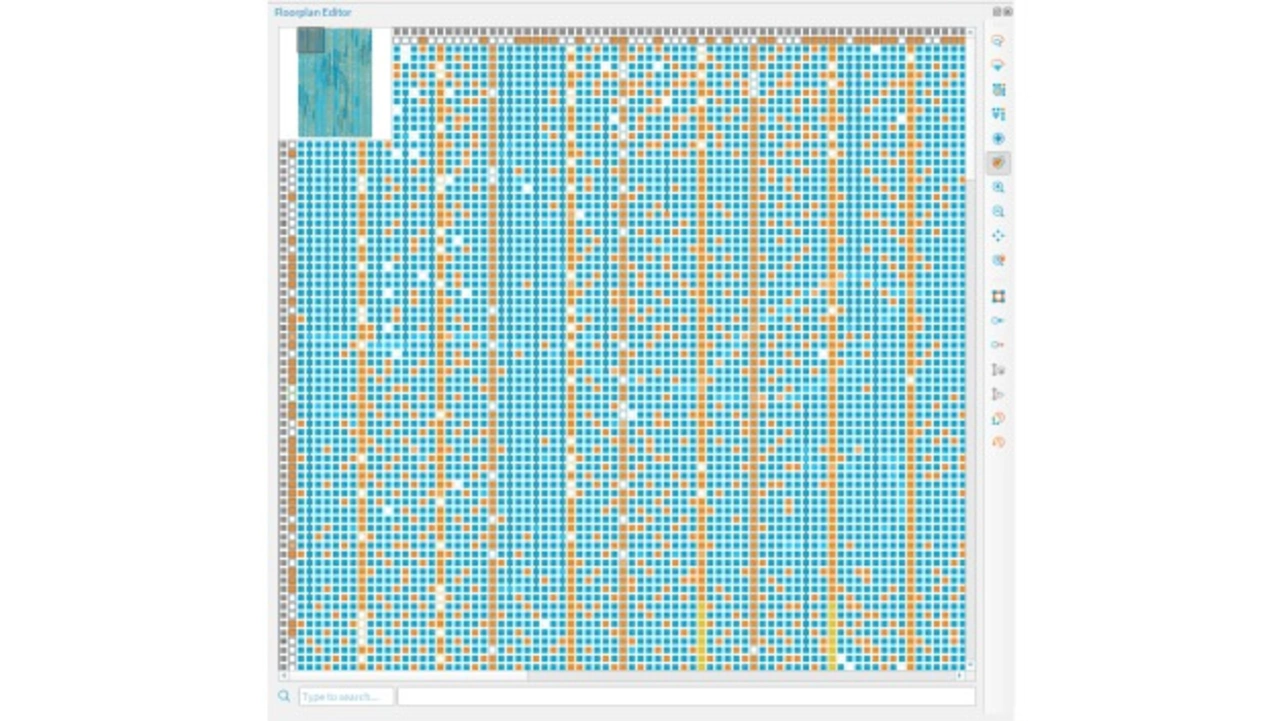

Abbildung 7 zeigt den Floorplan.

Zusammenfassung

Aufgrund der einzigartigen Quantum-Architektur und der flexiblen XLR-Zelle kann Efinix eine skalierbare FPGA-Architektur anbieten, die nicht wie traditionelle FPGA-Architekturen durch das Routing begrenzt ist. Die Quantum-Architektur ermöglicht eine kleinere Die-Fläche, einen geringeren statischen Stromverbrauch sowie einen geringeren dynamischen Stromverbrauch. Bei der Quantum-Architektur sind die Verbindungen optimierter, kürzer, was zu einer geringeren Kapazität führt, welches eine geringere dynamische Leistungsaufnahme für die Verbindungen zwischen den Blöcken ermöglicht.

Ein gutes Beispiel für die kleine Chipgröße ist der Ti60, das erste Mitglied der Titanium-Familie. Er ist für 60K LEs 3,5 x 3,4 mm groß in einem winzigen 64-Pin-WLCSP-Gehäuse; es gibt keine anderen FPGAs, die auch nur annähernd diese Logikkapazität und Größe aufweisen.

- Details zur Quantum-Architektur von Efinix und ihre Vorteile

- Die Innovation der Quantum-Architektur

- High-Speed Titanium-Familie

- Dynamische Logik und Routing

- Die Titanium XLR-Zelle in Aktion