Klein, schnell, energiesparend

Details zur Quantum-Architektur von Efinix und ihre Vorteile

Fortsetzung des Artikels von Teil 3

Dynamische Logik und Routing

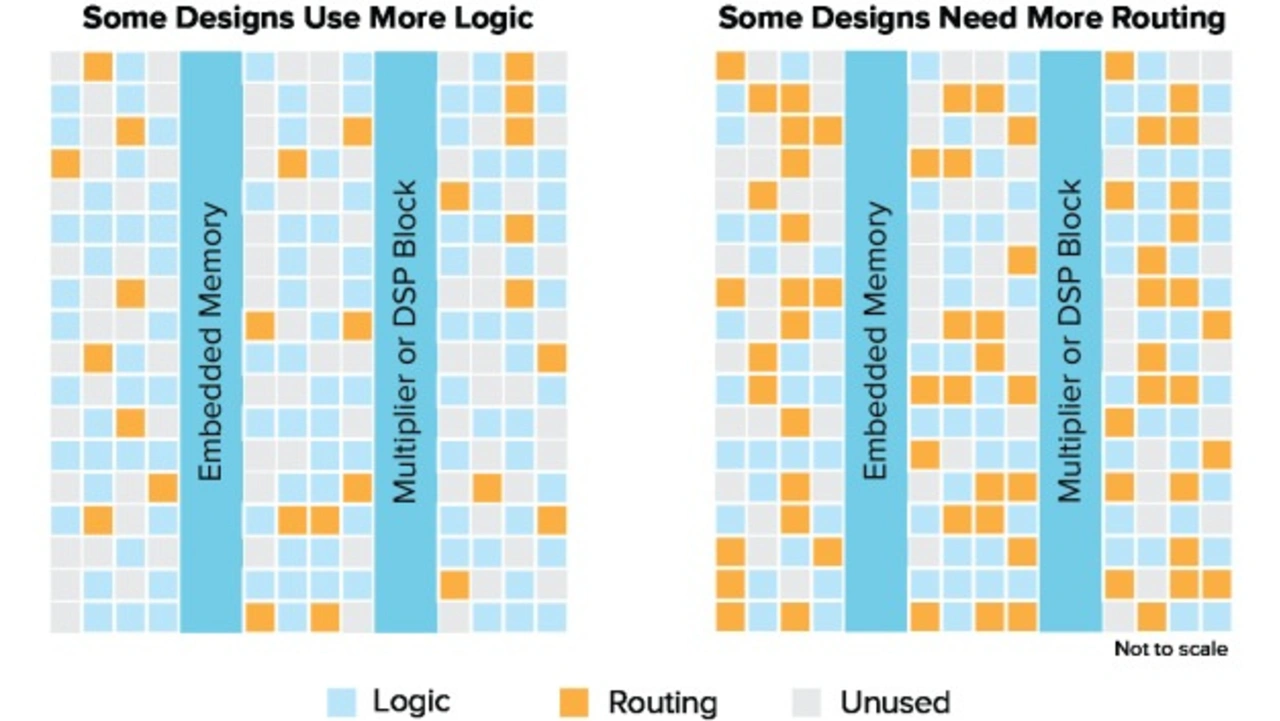

Manche Designs benötigen mehr Routing, manche weniger, und genau hier zeigt die XLR-Zelle ihre Qualität und Effektivität. Die Efinity-Software verfügt über Heuristiken, die abschätzen, wie viele XLR-Zellen ein Design für das Routing benötigt. Wenn das Design nicht alle der reservierten XLR-Zellen für das Routing benötigt, kann die Software diese dynamisch für weitere Logik verwenden (Abbildung 5).

Jobangebote+ passend zum Thema

Da die XLR-Zelle sowohl Logik als auch Routing unterstützt, kann die Software, nachdem sie die gesamte Logik platziert hat, dieselben XLR-Zellen auch für das Routing verwenden. Das hat enorme Vorteile. Folgendes Szenario: ein Design schreitet gut voranschreitet, alles ist gut geroutet und das FPGA fast voll mit Logik gefüllt. Jetzt muss noch ein bisschen Logik hinzufügt gefügt werden. Wenn die Logik in einem traditionellen FPGA aufgebraucht ist, gibt es keinen Platz mehr dafür. Mit der XLR-Zelle kann der Entwickler diesen zusätzlichen Schritt gehen und noch ein bisschen mehr Logik einbauen. Die Quintessenz: Der Entwickler kann mehr XLR-Zellen und damit mehr LEs verwenden, als im Datenblatt angegeben sind. Dieser Punkt ist sogar so wichtig, dass er wiederholt werden muss: Titanium-FPGAs können mehr Logik bieten, als im Datenblatt angegeben ist.

Wenn der Entwickler mehr Logik bekommen kann, als das Datenblatt angibt, warum gibt Efinix eine niedrigere Zahl an? Wie wir bereits erklärt, hat Efinix umfangreiche Tests durchgeführt, die zu den im Datenblatt angegebenen Werten geführt haben. Obwohl viele Designs mit weniger Routing auskommen können, benötigen andere wirklich alle diese reservierten XLR-Zellen. Das Datenblatt gibt eine konservative Schätzung für die Anzahl der benötigten XLR-Zellen für durchschnittliche Designs.

- Details zur Quantum-Architektur von Efinix und ihre Vorteile

- Die Innovation der Quantum-Architektur

- High-Speed Titanium-Familie

- Dynamische Logik und Routing

- Die Titanium XLR-Zelle in Aktion