imec

Neue SOT-MRAM-Architektur beseitigt bisherige Probleme

Fortsetzung des Artikels von Teil 1

SOT-MRAM hat aber seine eigenen Probleme

SOT-MRAM ist nicht-flüchtig und benötigt daher trotz hoher Speicherdichte eine deutlich geringere Standby-Leistungsaufnahme als SRAM. Aber die dynamische Leistungsaufnahme ist aufgrund des hohen Stroms, der für den Schreibvorgang benötigt wird, immer noch relativ hoch.

Darüber hinaus sind auch noch Innovationen bei Skalierung der Dichte erforderlich, damit SOT-MRAM zu einem echten Konkurrenten für SRAM in eingebetteten Speicheranwendungen werden kann. Die Einführung einer senkrechten Magnetisierung in der festgelegten und freien Schicht (als p-MTJ bezeichnet) anstelle einer traditionellen Magnetisierung in der Ebene verbessert die Skalierungsmöglichkeiten, da die Speicherzelle nicht mehr rechteckig sein muss.

Die größte Herausforderung liegt jedoch in der Architektur. STT-MRAM mit seiner säulenartigen Struktur ist eine Komponente mit zwei Anschlüssen. Wenn diese Speicherzellen in einem Array implementiert werden, ist nur ein Auswahlelement – typischerweise ein (Zugriffs-)Transistor - pro MTJ-Zelle notwendig, um das Speicherelement zum Lesen oder Schreiben auszuwählen. SOT-MRAMs hingegen mit den getrennten Lese- und Schreibpfaden sind Komponenten mit drei Anschlüssen: zwei Zugriffstransistoren für jedes Speicherelement, einer zum Lesen, einer zum Schreiben. Unabhängige Lese- und Schreibpfade bieten zwar einen Vorteil in Hinblick auf die Zuverlässigkeit, sie benötigen aber aufgrund des zusätzlichen Zugriffstransistors, der mit zusätzlichen Metalldrähten verbunden ist, zusätzlichen Bauraum.

Und dann ist da auch noch das Problem in Hinblick auf die Fertigbarkeit. Das imec hatte 2018 die Integration von SOT-MRAM auf 300-mm-Wafern mit CMOS-kompatiblen Prozessen in vollem Umfang demonstriert und damit die industrielle Einführung erleichtert. Die praktische Umsetzung einer SOT-MRAM -p-MTJ-Bitzelle blieb jedoch nach wie vor aufgrund des zusätzlichen Magnetfelds in der Ebene während des Schreibvorgangs schwierig. Dieses Magnetfeld ist erforderlich, um die Symmetrie zu brechen und einen deterministischen Magnetisierungswechsel zu gewährleisten. Mit anderen Worten: Ohne dieses Magnetfeld ist es unmöglich zu wissen, welche Orientierung die freie Schicht nach Anlegen des Schreibstroms aufweist. In der Entwicklungsphase von SOT-MRAM kann dieses Feld durch ein externes Magnetfeld erzeugt werden, aber die endgültigen Komponenten erfordern eine robuste und kompakte Felderzeugung im Baustein selbst.

Jobangebote+ passend zum Thema

Wesentliche Optimierungsschritte

Bisher wurden Lösungen für jede der einzelnen Probleme erfolgreich demonstriert - mehrere davon wurden vom imec entwickelt und auf 300mm-Wafern demonstriert.

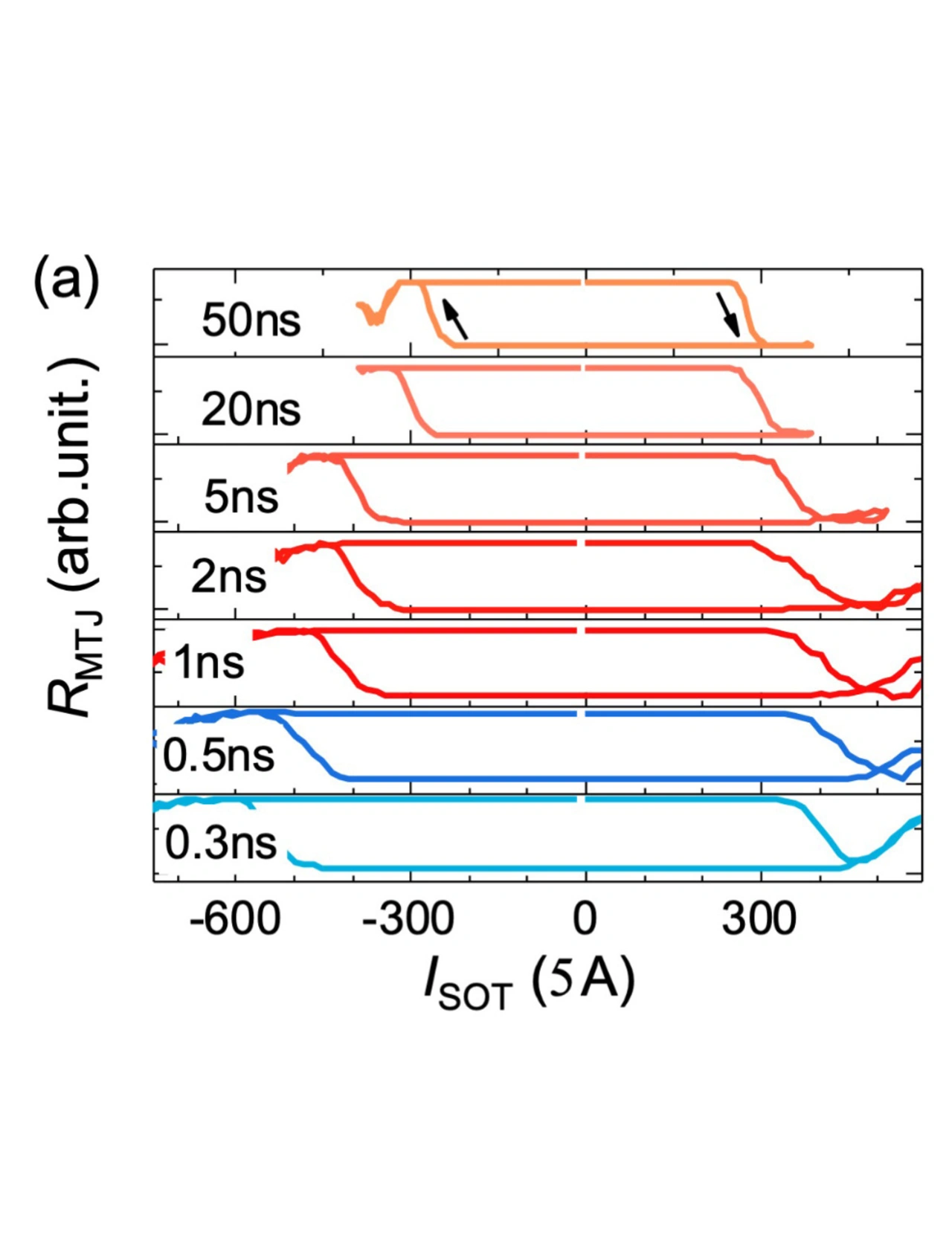

Die Rolle des externen Magnetfeldes übernimmt ein eingebetteter Ferromagnet in der Hartmaske für die SOT-Schicht. Damit wird ein externes Magnetfeld überflüssig. Der Ferromagnet induziert ein kleines homogenes Feld in der Ebene auf der freien Schicht des magnetischen Tunnelübergangs. 2019 hat das imec bereits gezeigt, dass dieser »feldfreie« Schaltansatz zuverlässig ist und gleichzeitig ein Schreiben des SOT-MRAMs im Bereich von weniger als 1 ns zulässt.

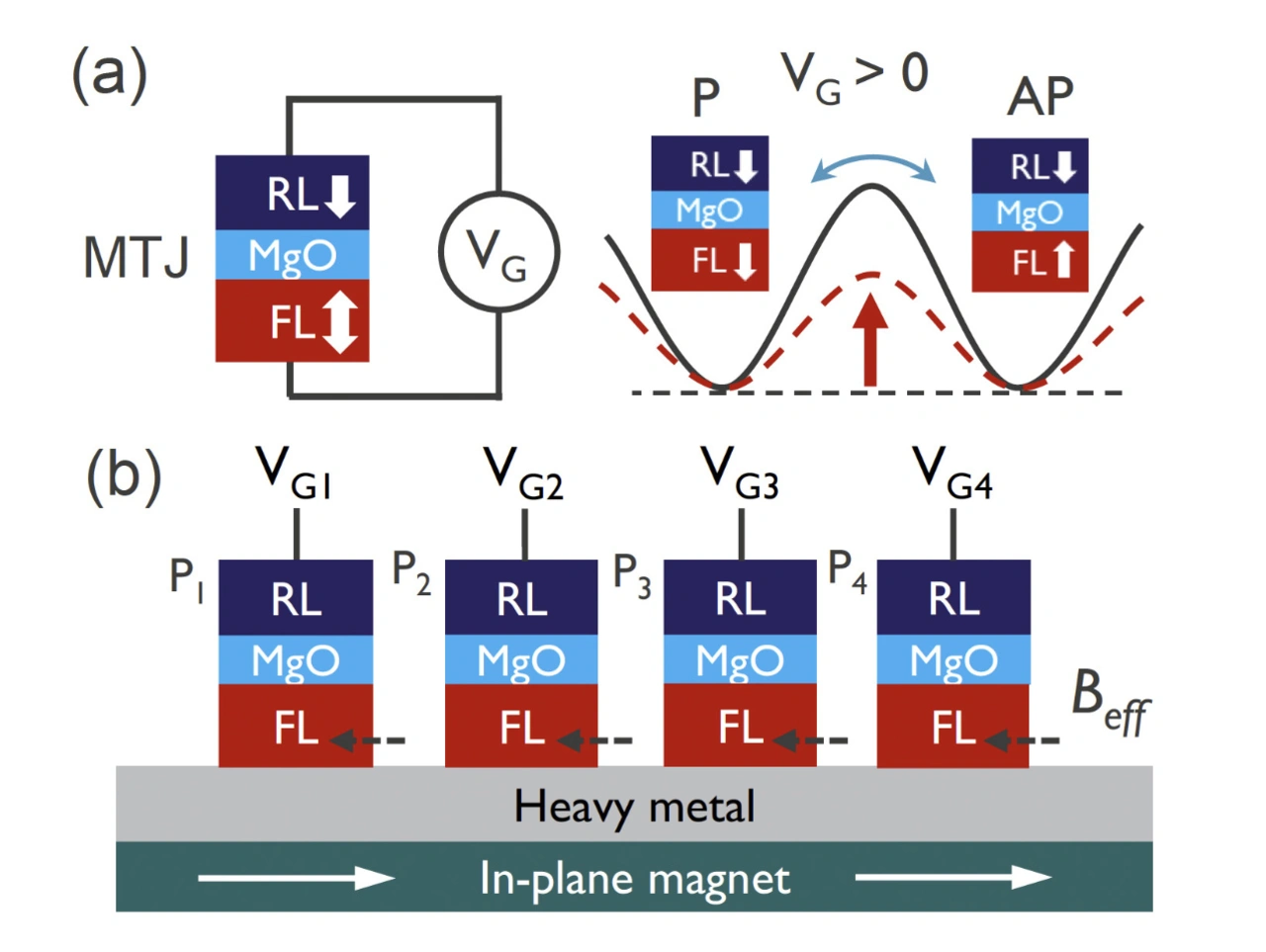

Die Probleme, die mit dem hohen Schreibstrom verbunden sind, können teilweise durch einen spannungsgesteuerten Ansatz (Voltage Gate - VG) gelöst werden. In einem solchen VG-SOT-MRAM ist der SOT-Effekt zwar weiterhin für das Schalten der freien Schicht verantwortlich, aber ein spannungsgesteuertes magnetisches Anisotropie-Gate (VCMA) erzeugt ein elektrisches Feld (über die Tunnelbarriere), um die Energiebarriere zu senken. Dadurch wird für den Schreibvorgang ein geringerer Strom benötigt, was die dynamische Leistungsaufnahme verbessert.

Ein weiterer Vorteil des VG-unterstützten Ansatzes besteht darin, dass damit der Weg zu Multi-Bit-Bauteilstrukturen (Multi Pillar) offensteht. Anstatt einen MTJ-Stapel mit einer SOT-Leitung zu verbinden, können nun vier (oder mehr) MTJ-Stapel auf einer gemeinsamen SOT-Leitung implementiert werden. In dieser Multi-Bit-Komponente kann ein einzelner Stapel (oder ein Bit) ausgewählt werden, indem eine Spannung an sein VCMA-Gate angelegt wird. Dies führt zu einer Verringerung der Energiebarriere und erleichtert das Schalten. Aber es wird nur ein einziger (großer) Zugriffstransistor (statt vier) benötigt, um über die gemeinsame SOT-Leitung zu schreiben. Und das führt zu einer insgesamt kompakteren Bit-Zelle.

Bislang wurden jedoch noch keine Ansätze demonstriert, die einerseits kein externes Magnetfeld benötigen (feldfreies Schalten) und gleichzeitig mit einem Multi-Bit-Ansatz kompatibel sind. Zum Beispiel erfordert die oben vorgestellte Lösung für ein feldfreies Schalten die Einbettung eines Ferromagneten in jede der p-MTJ-Stapel, was die Skalierbarkeit stark beeinträchtigt.

Alles gemeinsam umsetzen – das ist das Ziel

Auf der IEDM 2022 hat imec einen neuartigen, voll funktionsfähigen Multi-Bit-SOT-MRAM demonstriert, der alle oben genannten Herausforderungen auf einen Streich löst.

Bei der neu entwickelten Architektur kommt weiterhin ein skalierbarer Ansatz ohne externes Magnetfeld zum Tragen, indem das imec eine planare, magnetische Schicht innerhalb der gemeinsamen SOT-Schicht implementiert (hybride Spinquelle). Diese zusätzliche gemeinsame planare, magnetische Schicht ist mit jedem einzelnen Speicherelement gekoppelt. Sie wirkt wie ein Magnetfeld für jeden Stapel, ist aber nicht mehr Teil jedes einzelnen MTJ-Stapels, was die Skalierbarkeit verbessert.

Zweitens hilft der VCMA-Effekt beim Schreiben, denn er moduliert und senkt die Energiebarriere für das eigentliche Schalten, was einen geringeren Energieaufwand beim Schalten zur Folge hat.

Drittens reduziert dieses VCMA-unterstützte Konzept die Anzahl der Transistoren pro Bit, was dem Flächenverbrauch und der Skalierbarkeit zugutekommt.

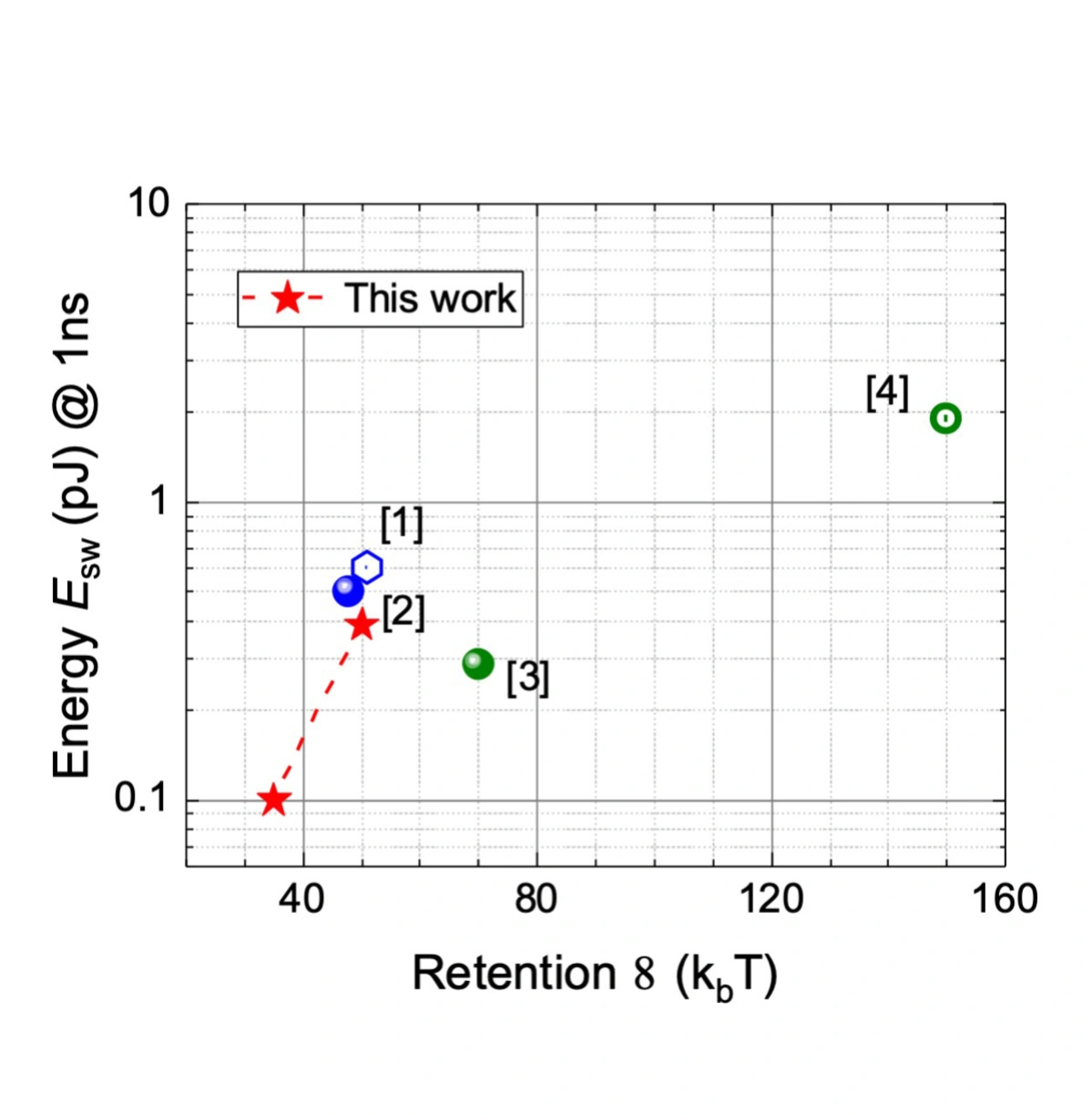

Dieser Ansatz ermöglicht ein »feldfreies« (ohne externen Magnet) Schalten mit hoher Schalteffizienz (etwa 60fJ/Bit Leistungsaufnahme), eine schnelle Schaltgeschwindigkeit (bis zu 300ps) und eine >1012 Lebenserwartung. Er eignet sich sowohl für Ein-Bit- als auch für Multi-Bit-SOT-Bausteine, und die integrierte 300-mm-Technologie ist CMOS- und Back-End-of-Line-kompatibel.

- Neue SOT-MRAM-Architektur beseitigt bisherige Probleme

- SOT-MRAM hat aber seine eigenen Probleme

- Auf dem Weg zur industriellen Umsetzung