Embedded-Prozessoren

Neue Sitaras mit Rekord-Rechenleistung

Fortsetzung des Artikels von Teil 1

Funktionen von Mikrocontrollern auf dem Chip

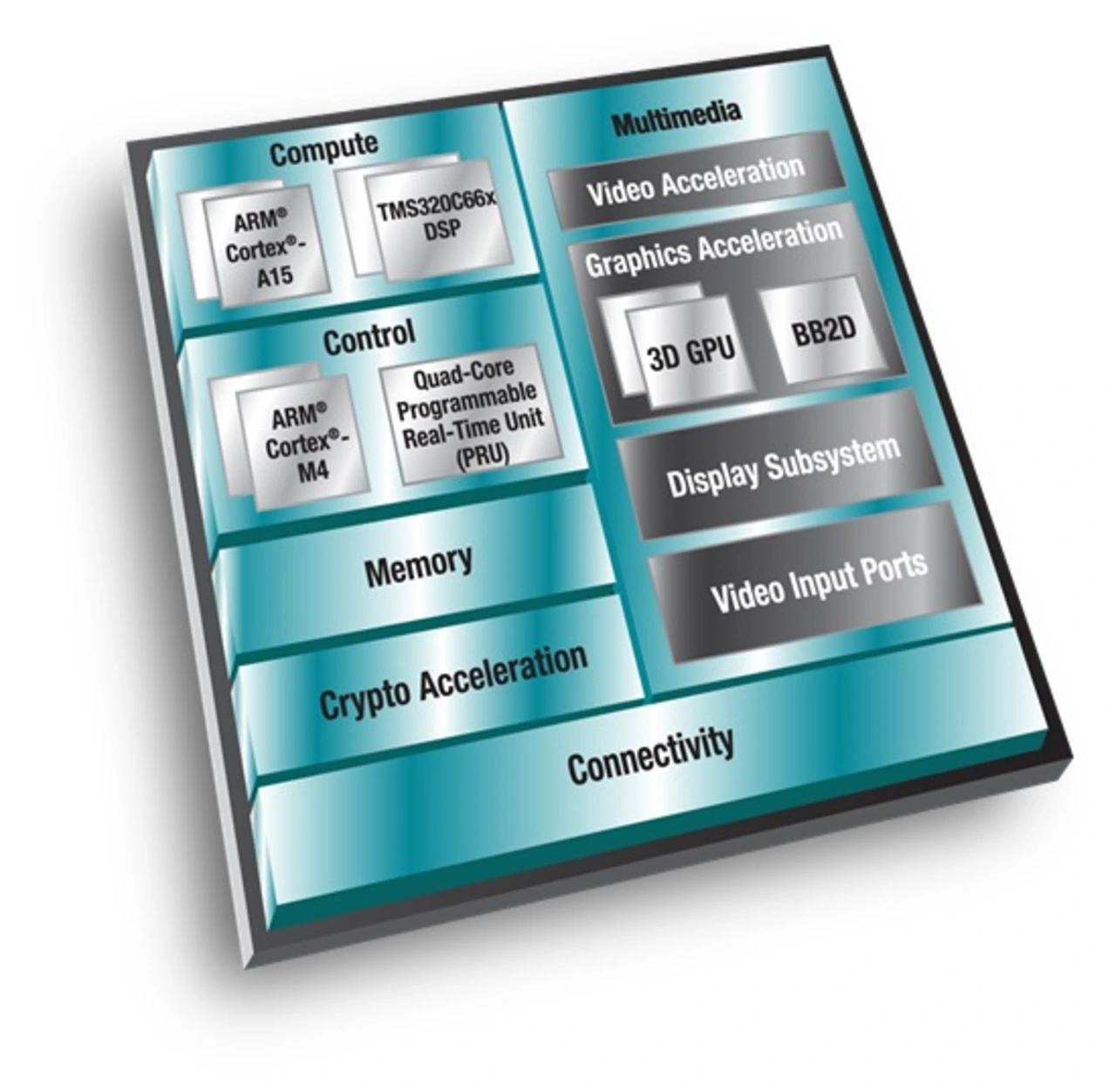

Wie Bild 2 zeigt, haben die neuen Chips mehrere Funktionen, die man normalerweise in Mikrocontrollern findet, wie Pulsbreitenmodulatoren (PWM) und diverse Schnittstellen wie z.B. Ethernet oder CAN. Im Gegensatz zu MCUs fehlt ihnen der nichtflüchtige Speicher.

Sie behalten die programmierbare Echtzeit-Einheit und das industrielle Kommunikationssubsystem (PRU-ICSS), das man von anderen High-End-Sitara-Prozessoren kennt. Die neuen Chips implementieren vier dieser mit 200 MHz getakteten proprietären RISC-Cores (doppelt so viele wie in den ersten Sitara-Chips), auf diesem deterministischen Subsystem läuft eine Firmware, die verschiedene Industrieprotokolle wie Profinet, Profibus, Powerlink, EnDat und Ethernet/IP implementiert. Die PRU ist im Prinzip ein kleiner Prozessor mit eingeschränktem Befehlssatz. Dieser kann zur Bereitstellung bestimmter Ressourcen für Echtzeit-Funktionen konfiguriert werden, die auf dem Chip nicht verfügbar sind.

In industriellen Steuerungs-Applikationen wird die PRU in der Regel für I/O-Funktionen konfiguriert. Durch den Einsatz der PRU lassen sich gegenüber der Verwendung eines externen Chips für dieselbe Funktion Systemkosten sparen. Unter anderem können mit der PRU auch weitere Standard-Schnittstellen wie ein UART oder industrielle Feldbusse (z.B. Profibus) implementiert werden. Da die PRU frei programmierbar ist, lassen sich jedoch auch kundenspezifische Schnittstellen realisieren. Die PRU kann dank ihrer Programmierbarkeit in verschiedenen Verarbeitungs-Szenarien für unterschiedliche I/O-Typen genutzt werden, um die Stromaufnahme zu senken und die System-Performance zu steigern. Unter anderem kann die PRU bestimmte kundenspezifische Datenbehandlungs-Aufgaben übernehmen, damit der Cortex-A15-Prozessor entlastet werden kann.

Kunden können sogar nachträglich per Mausklick entscheiden, welches Protokoll im PRU-ICSS laufen soll. Sie müssen in das PRU-ICSS nur eine Firmware laden, die das Subsystem für ein bestimmtes Protokoll konfiguriert und das Protokoll implementiert, um beispielsweise EtherCAT Slave durch Powerlink zu ersetzen. Der ARM Cortex-A15 lädt dabei die Firmware und spielt sie in das PRU-ICSS hinein. Auf diese Weise können Anwender auch alle Topologien, ob Linien-, Stern- oder Ringtopologie, in das PRU-ICSS implementieren. Die Firmware wird von TI bereitgestellt und lässt sich von der TI-Webpräsenz herunterladen.

Cortex-M4 für Echtzeitanwendungen und DSP on Chip

Der Cortex-A15 ist ein Applikationsprozessor, der für Echtzeitanwendungen nicht geeignet ist. Schon die Caches (jeweils 32 KB L1-Cache für Befehle und Daten und bis zu 2 MB geteilter L2-Cache für die Dual-Core-Varianten) machen - solange man sie nicht abschaltet - jede Vorhersagbarkeit zunichte - je nachdem, ob Daten/Befehle im Cache liegen oder aus dem Hauptspeicher geladen werden müssen, wird eine unterschiedliche Anzahl Taktzyklen benötigt. Die Sprungvorhersage tut ihr übrigens - bei einer Fehlvorhersage muß die lange Pipeline gelöscht und neu mit Instruktionen geladen werden. Und last but not least sind die auftretenden Latenzzeiten bei Interrupts nicht für industrielle Anwendungen brauchbar.

Da die AM57x jedoch auch auf Echtzeitanwendungen zielen, hat TI zwei jeweils mit 213 MHz getaktete Mikrocontroller-Cores des Typs ARM Cortex-M4 implementiert, die 64 KB geteilten RAM-Speicher aufweisen. Der M4 weist mit seiner 6-stufigen-In-Order-Pipeline sehr geringe Latenzzeiten bei Interrupts auf (12 Taktzyklen), bei Inter-Interrupts werden sogar nur 6 Taktzyklen fällig.

Neben den Cortex-M4 wurden auch noch je nach Derivat ein oder zwei DSP-Cores des Typs TMS320C66x mit 32KB/32KB L1-Cache und 288 KB L2-Cache spendiert, die mit jeweils bis 750 MHz getaktet werden und z.B. für komplexe Motorsteuerungs-Algorithmen, Medical Imaging, Testen & Messen und andere analytische Funktionen verwendet werden können. Mit 48 GMACs bzw. 24 GFLOPs wird hier Rechenleistung satt bereitgestellt.

Natürlich stellt sich die Frage, wie zwischen diesen ganzen Hardware-Blöcken (es gibt neben CPUs, DSPs, GPUs und MCUs auf L3-Ebene noch 2,5 MB geteiltes RAM mit fehlererkennenden bzw. fehlerkorrigierenden Codes, ECC) die Daten hin- und hergeschaufelt werden. Auf L3-Ebene wurde ein NoC (Network on Chip), den TI von Arteris lizensiert hat, eingebaut, darunter auf L4-Ebene gibt es sogar nochmals vier Instanzen der Schaltmatrix Sonics3220, die man von Sonics lizensiert hat.

In komplexen SoC-Designs wie dem AM57x stellt ein NoC hohe Bandbreite zwischen den einzelnen Blöcken bereit und vermeidet Datenkollisionen auf den Leitungen. Dazu werden Daten in Pakete umgewandelt, die priorisiert und über das Netzwerk verschickt werden. Hersteller wir Arteris bieten dazu Konfigurations-Tools an, um das NoC so energieeffizient und Chipfläche-sparend wie möglich als Ring, Baum, Multischicht-Design oder eine Kombination von allem zu konfigurieren.

Interessant ist dabei, dass diese Tools auch das Chip-Design hinsichtlich der Stromversorgung vereinfachen. Mit ihnen können die Blöcke in Power- und Taktdomänen aufgeteilt werden, das NoC kümmert sich automatisch um den Datenaustausch vpon einer Domäne zur nächsten unabhängig von deren Taktfrequenzen. Diese feine Granularität ermöglicht für jeden Block die optimale Energieeffizienz herauszuholen und ihn abzuschalten, wenn er nicht benötigt wird. NoCs unterstützen dazu noch unterschiedliche Spannungsdomänen, was die Frequenz- und Spannungsskalierung (DVFS) vereinfacht.

Fest steht, die AM57x sind hardwareseitig die mit Abstand komplexesten Sitara-Chips, die TI jemals gebaut hat.

Jobangebote+ passend zum Thema

Schnellerer Speicher und GPU

Aus Energiespargründen integrieren die AM43x nur eine 32-bit-DDR3-800-Schnittstelle, die ebenso auch LPDDR2 und DDR3L DRAM unterstützt und 3,2 GB/s Spitzenbandbreite bietet. Die neuen AM57x hingegen haben - wie übrigens schon die allerersten, älteren AM387x und AM389x - zweikanalige 32-bit-Schnittstellen, allerdings nicht für DDR3-800 bis DDR3-1600, sondern für DDR3L Den Sitara-Prozessoren der Familie AM43x fehlt dabei auch eine wichtige Funktion: ECC-Schutz auf der DRAM-Schnittstelle. Einige Industriesysteme benötigen diesen Fehlerschutz und die meisten anderen Embedded-Prozessoren in dieser Klasse bieten dieses Leistungsmerkmal an. Mit dem AM57x hat TI jetzt nachgebessert, eine der mit 532 MHz getakteten Schnittstellen unterstützt fehlerkorrigierende bzw. fehlererkennende Codes (ECC). Der geteilte On-Chip-Speicher ist dank 28-nm-Fertigung auf 2,5 MB gewachsen, auch er ist mit ECC geschützt.

Im Rahmen einer weiteren Energiesparmaßnahme verwendete TI in den AM4379 und AM4378 eine langsamere Version der GPU PowerVR SGX530, die auf rund 30 Millionen Dreiecke/s kommen. Die mit 425 Mhz getakteten Power VR SGX544 sind da von einem ganz anderen Kaliber: Die kamen schon in Samsungs Smartphone Galaxy S4 zum Einsatz und haben bei 400 MHz eine Rechenleistung von 70 Mio. Dreiecken/s. Neu ist eine weitere GPU speziell für 2D-Grafiken, die GC320 von Vivante. An Ausgängen stehen bis zu 3 LCD-Anschlüsse (MIPI DPI 2.0, BT-656 oder BT-1120), ein HDMI-Anschluß 1.4a und darüber hinaus 6 Video-Eingänge für Kameras (jeweils 2x8 bit, 16 bit und 24 bit) zur Verfügung.

- Neue Sitaras mit Rekord-Rechenleistung

- Funktionen von Mikrocontrollern auf dem Chip

- Mehr Schnittstellen - mit PCI und SATA