Imec

Der Prozessspezialist

Fortsetzung des Artikels von Teil 1

MRAMs auf 300-mm-Wafer

Imec hat vor Kurzem außerdem einen Prozess für die Fertigung von CFETs (Complementary FETs) für den N3-Knoten vorgestellt. Die Forscher sind überzeugt, dass CFETs den FinFETs gegenüber überlegen sind und dass eine Flächenskalierung von Standardzellen und Speicher-SRAM-Zellen um 50 Prozent ermöglichen. Der CFET ist eine Weiterentwicklung eines vertikalen Gate-All-Around-Nanodrahttransistors. Statt entweder n- oder p-Typ-Transistoren zu stapeln, werden beide übereinander gestapelt. Bei dem vom Imec vorgeschlagene Prozess-Flow wird ein vertikaler n-Typ-Transistor (Nanosheet) auf einen p-Typ-FinFET gesetzt. Damit ist es möglich, einerseits den FinFET-Prozess und andererseits das Potenzial von Stresstechniken im unteren pFET gleichzeitig zu nutzen. TCAD-Analysen haben gezeigt, dass der vorgeschlagene CFET den Anforderungen eines N3-Knotens hinsichtlich Leistungsaufnahme und Performance entspricht und damit FinFETs übertrifft. Das Imec geht davon aus, dass sich mit den CFETs die Fläche in SDCs oder SRAM-Zellen um 50 Prozent reduzieren lässt.

Darüber hinaus hat das Imec erhebliche Fortschritte bei der Entwicklung von Ge-Nanodraht-PFETs erzielt, die als praktische Möglichkeit für eine Skalierung über den 5-nm-Knoten hinaus gelten.

Steegen erklärt: »Mit einer Reihe von Skalierungs-Booster-Maßnahmen kann die Industrie die FinFET-Technologie noch auf den 7- oder sogar 5-nm-Knoten erweitern. Danach erscheint die Gate-All-Around-Architektur, kurz GAA, als praktische Lösung, da bei ihrer Fertigung die meisten FinFET-Prozessschritte wiederverwendet werden können.« Ein Problem von GAA und den damit verbundenen lateralen Nanodrähten besteht darin, dass der Kanalquerschnitt im Vergleich zu herkömmlichen FinFETs deutlich kleiner ausfällt. Um die Treiberleistung zu erhöhen, könnte man mehrere Nanodrähte übereinanderstapeln. Das wiederum erhöht aber die parasitären Kapazitäten und Widerstände. Steegen hält deshalb einen anderen Weg für günstiger: Die Silizium-Nanodrähte durch ein Kanalmaterial zu ersetzen, das eine höhere Mobilität ermöglicht, zum Beispiel Germanium. Untersuchungen hätten gezeigt, dass dieser Ansatz tatsächlich machbar ist und dass damit die Kosten-, Flächen- und Leistungsanforderungen für die Technologieknoten kleiner als 5 nm erfüllt werden.

Eine erste Studie über gestreckte Ge-Nanodraht-pFETs haben laut Steegen ergeben, dass sich dieser Ansatz sowohl für analoge als auch digitale ICs eignet. Aus ihrer Sicht hätten gezielte Optimierungen wichtiger Prozessschritte dieser Transistoren dazu geführt, dass sie eine ernstzunehmende Konkurrenz für die GAA-Technologie mit Si-Nanodrähten sind.

Wobei das Imec mit Ge-GAA-FETs mittlerweile Leistungen erreicht, die laut Steegen mit denen modernster SiGe- und Ge-FinFETs durchaus konkurrieren können. Außerdem konnte das Forschungsinstitut erstmals auf einer 14-/16-nm-Plattform p-Typ-Ge-GAA-FETs mit gestapelten Nanodrähten realisieren. Steegen: »Die GAA-Nanodrahttechnologie erscheint als vielversprechende Hochleistungslösung für zukünftige Prozessknoten, sofern die Sperrschichten weiter optimiert werden.

MRAMs auf 300-mm-Wafer

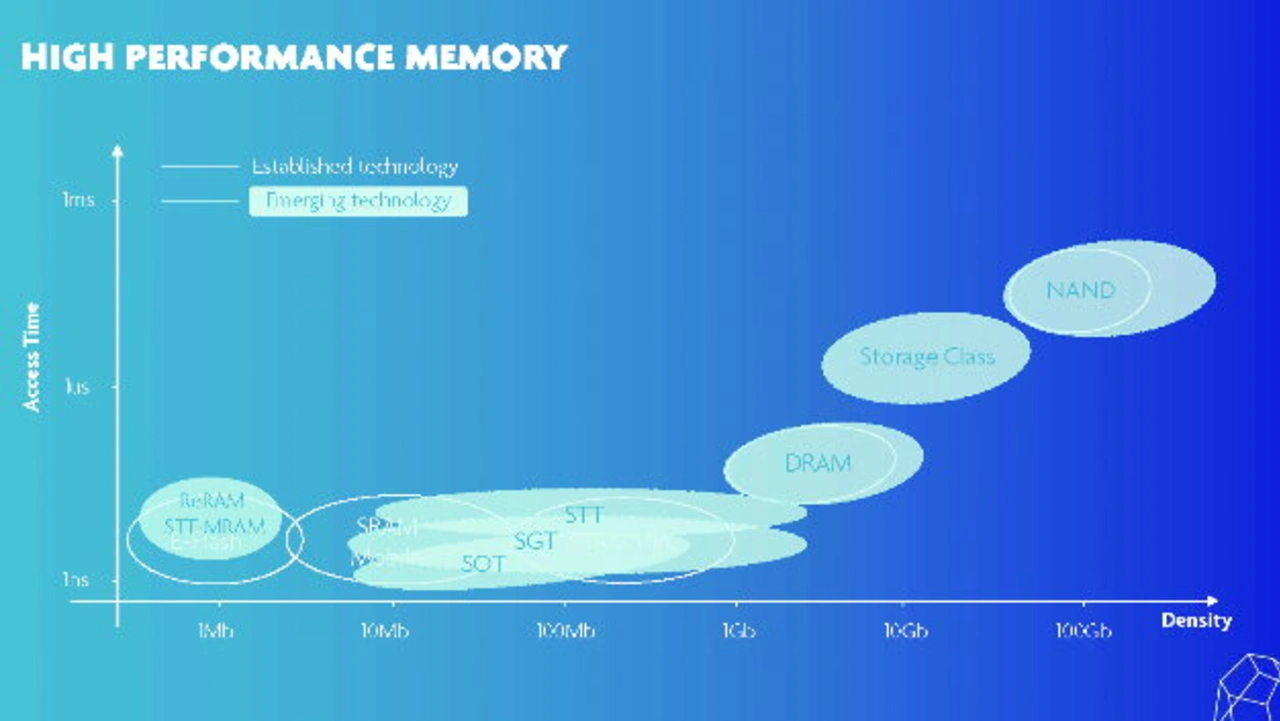

Das Imec hat außerdem als erster gezeigt, dass SOT-MRAMs (Spin-Orbit-Torque-MRAMs) auf 300-mm-Wafern mit CMOS-kompatiblen Verfahren hergestellt werden können. Die MRAMs zeichnen sich durch eine unbegrenzte Lebensdauer, einer hohen Schaltgeschwindigkeit (210 ps) und einem Stromverbrauch von nur 300 pJ erreichen die SOT-MRAMs in einer 300-mm-Linie die gleiche oder bessere Leistung wie im Labor. Das Imec ist überzeugt, dass diese MRAM-Technologie als Ersatz von L1/L2-SRAM-Cache-Speichern in Hochleistungs-Computeranwendungen fungieren wird.

SOT-MRAM ist eine sehr neue, nichtflüchtige Speichertechnologie, die sich durch einen sehr langen Datenerhalt, geringe Leistungsaufnahme und hohe Schaltgeschwindigkeit (unter 1 ns) auszeichnet. Mit diesen Eigenschaften überwindet sie die Beschränkungen von STT-MRAM (Spin-Transfer-Torque-MRAM), das bislang gerne als Ersatz des L1/L2 SRAM-Cache-Speichers gesehen wurde. Bisher wurden SOT-MRAMs jedoch nur im Labor demonstriert; Imec hat nun erstmals die vollständige Integration von SOT-MRAMs auf 300-mm-Wafern mit CMOS-kompatiblen Prozessen nachgewiesen.

Das Imec hat das SOT- und STT-Schaltverhalten auf ein und demselben IC verglichen, das auf einem 300-mm-Wafer hergestellt wurde. Während die Schaltgeschwindigkeit beim STT-MRAM auf 5 ns begrenzt war, war ein zuverlässiges Schalten des SOT-MRAM auch bei 210 ps möglich.

Jobangebote+ passend zum Thema

- Der Prozessspezialist

- MRAMs auf 300-mm-Wafer