IEDM 2017

3D-Integration im Quadrat für allgegenwärtiges Computing

Fortsetzung des Artikels von Teil 2

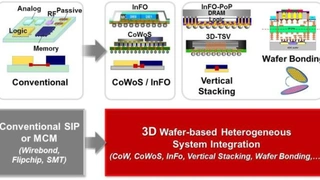

Heterogene 3D-System-Integration

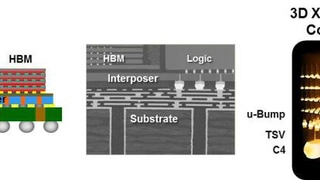

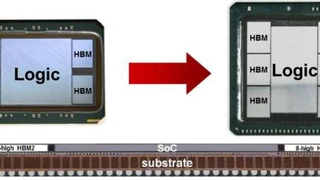

Für die heterogene 3D-System-Integration von 3Dx3D-Systemen gibt es drei Hauptklassen. CoWoS bestehend aus einem Si-Interposer (Verdrahtungzwischenschicht) mit Cu-TSV (Through Silicon Vias) eignet sich ideal für Hochleistungs-Anwendungen mit hohen Pin-Zahlen und hohem Bandbreitenbedarf. Ein kostengünstigeres Verfahren ist InFO, das auf Wafer-Ebene mit Vergussmasse arbeitet und ein Substrat für mobile und andere Computing Anwendungen bereitstellt. Das dritte Verfahren nutzt Wafer-zu-Wafer-Bonding, das beispielsweise bei CMOS-Bildsensoren eingesetzt wird. Diese Wafer-basierten 3D-System-Integrationstechniken können die Chip-zu-Chip und System-Interconnect-Abstände mit dem Ziel einer höheren Dichte reduzieren und verbessern die Systemleistung, die I/O-Bandbreiten und Stromversorgung, den Formfaktur und die Funktion. Die zweite Generation von CoWoS bietet nun eine Interposer-Fläche von 1200 mm2, HD-MiM-Kondensatoren und bleifreien Cu-Lötkugeln, so dass sich damit Systeme mit über 200 Mrd. Transistoren realisieren lassen. Das InFO-Verfahren erlaubt die Integration von Spannungsreglern und passiven Komponenten, wie Spulen mit hoher Güte (>50) und HF-/Millimeterwellen-Antennen.

Jobangebote+ passend zum Thema

Heterogene 3D-System-Integration

- 3D-Integration im Quadrat für allgegenwärtiges Computing

- 3D-CMOS- und SoC-Skalierung

- Heterogene 3D-System-Integration