IEDM 2017

3D-Integration im Quadrat für allgegenwärtiges Computing

Fortsetzung des Artikels von Teil 1

3D-CMOS- und SoC-Skalierung

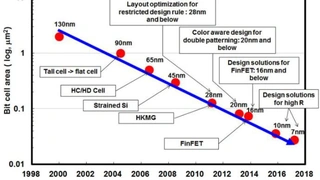

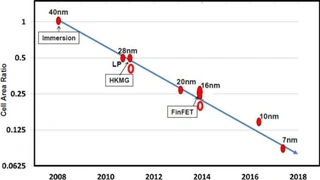

Die Transistorstrukturen des 10-nm-Knotens, der bei TSMC bereits fertigungsreif ist sind als FinFETs bereits dreidimensional ausgeführt und 7-nm-FinFETs wurden gerade qualifiziert. Multi-Patterning-Lithographieverfahren werden bei diesen feinen Strukturen sehr teuer, so dass ein Übergang auf EUV unvermeidbar wird. Erfreulicherweise wurden Fortschritte in der Lichtausbeute gemacht, so dass die Ausgangsleistung heute schon bei 125 W liegt. Prototypen schaffen heute schon 250 Watt, was als Zielgröße gilt. Außerdem konnte auch bereits ein täglicher Durchsatz von 1000 Wafern mit EUV-Belichtung demonstriert werden, was enorm wichtig für ist für den kommerziellen Einsatz. Zur Skalierung von energieeffizienten 3D-Transistor wird an neuen Transistor-Strukturen, Kanal-Materialien und Transistorphysik (Tunnel und Sub-Boltzmann-Konzepte) geforscht. Über den FinFET hinaus versprechen Gate-All-Around Nanowires (GAA-NW) eine gute Kontrolle der Kurzkanaleffekte.

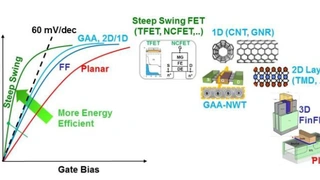

Um CMOS-Transistorstrukturen in den tiefen Nanometer-Bereich zu skalieren, wünscht man sich wenige Lagen (sub 5 nm dünn) luftbeständige 2D-Materialien mit guten dielektrischen Eigenschaften, großer Bandlücke (1 bis 1,2 eV), hoher Ladungsträger-Mobilität (>100-200cm2/V-s) und guten ballistischen Transporteigenschaften. Vielversprechende Kandidaten sind HfSe2 und ZrSe2 sowie MoS2. Sehr wichtig ist auch eine Skalierung der Spannungspegel, um die Leistungsaufnahme zu senken. Hier könnten Steep-Swing-Transistoren, wie TFETs (Tunnel-FETs), NCFETs (Negative Capacitance FETs, mit High-k ferroelektrischer Schicht) und PFETs (Phasen-FETs) das Swing-Limit von 60 mV/dec durchbrechen.

Zur Reduzierung parasitärer Widerstände und Kapazitäten bei tiefen Nanometer-Knoten sind neue Materialien, Beschichtungsverfahren und Schnittstellen-Innovationen erforderlich. Atomic Layer Deposition ist ein vielversprechender Kandidat zur Abscheidung dünnerer und feinerer Diffusionsbarrieren. Alternative 2D-Materialien mit niedrigem Widerstand wie Graphene könnten ebenfalls in Frage kommen. Überhaupt spielen bei tiefen Nanometer-Knoten Materialien für selektives Abscheiden von Atomlagen, selbstausrichtende Prozesse, Oberflächenfunktionalisierung und hartes Masking eine wichtige Rolle.

Jobangebote+ passend zum Thema

3D-CMOS- / SoC-Skalierung

- 3D-Integration im Quadrat für allgegenwärtiges Computing

- 3D-CMOS- und SoC-Skalierung

- Heterogene 3D-System-Integration