#powerfrage an Siemens EDA

Kann die Leistung von SoC-Designs verläßlich analysiert werden?

Eine genaue Abschätzung und Optimierung der Leistungsaufnahme von SoC-Designs wird wichtiger. Doch der geschätzte dynamische Stromverbrauch und die tatsächliche Verlustleistung des hergestellten SoC weichen oft stark voneinander ab. Der Einsatz von Hardware Emulationssystemen kann Abhilfe schaffen.

Ein Gespräch mit Jean-Marie Brunet von Siemens EDA.

Welches Problem hat die Halbleiterindustrie heute bei einer Leistungsabschätzung, die vor der Fertigung des Siliziumbausteins durchgeführt wird?

Das Problem liegt darin, dass der vor der Produktion eines SoC geschätzte dynamische Stromverbrauch und die tatsächliche Verlustleistung des hergestellten SoC voneinander abweichen.Der reale dynamische Stromverbrauch eines neu entwickelten SoC übertraf in den letzten jahren die vorherige Schätzung meist um ein Vielfaches.

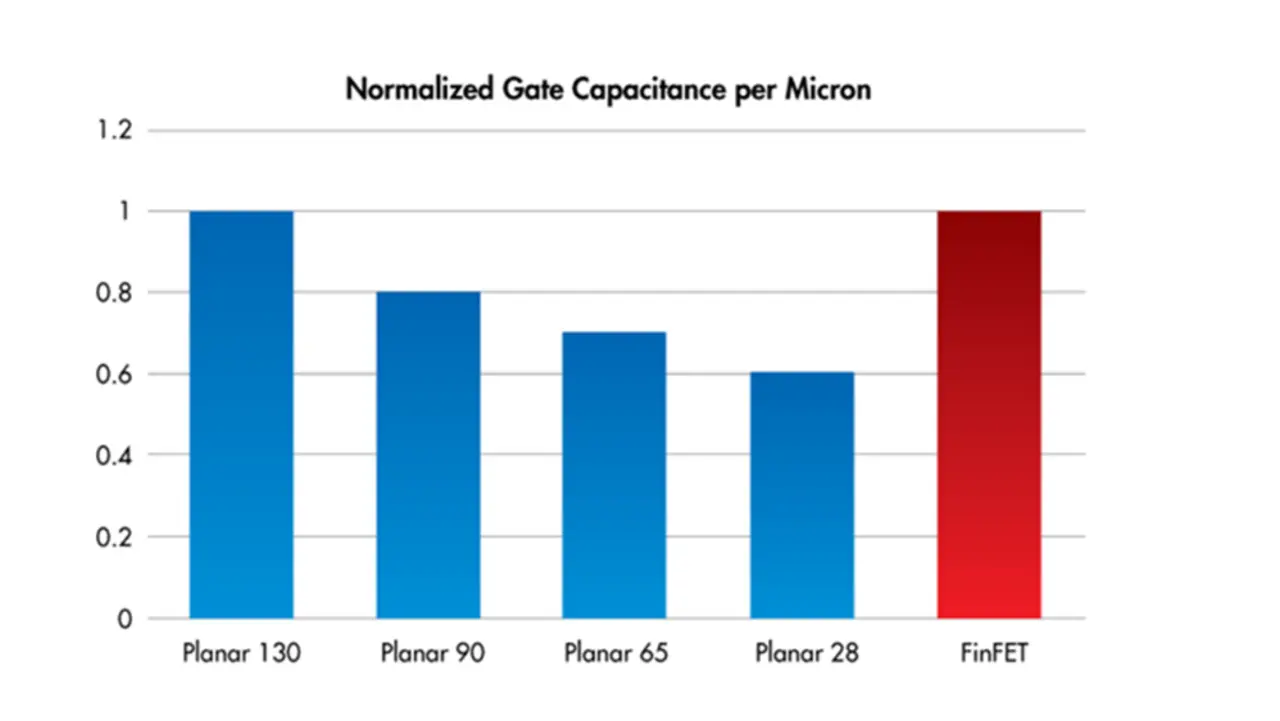

Dabei ist es schon während der Entwicklung und Verifizierung neuer Designs wichtig, den realen Stromverbrauch genau vorherzusagen. Die Hauptursache für die Diskrepanz ist der Umstieg von herkömmlicher planarer CMOS-Technologie auf die FinFET-Halbleitertechnologie. Die traditionelle CMOS-Technologie litt immer unter einen erheblichen Stromverlust im Leerlaufbetrieb. Mit der Übergang zu kleineren Technologien unterhalb von 32 nm stieg der Standby-Strom exponentiell an und wurde nicht mehr handhabbar. Die FinFET-Technik senkte den statischen Stromverlust drastisch. Leider hat sie den Umschalt- oder dynamischen Stromverbrauch nicht wesentlich verändert.

Können Sie etwas näher auf die dynamische Verlustleistung bei FinFET eingehen?

Durch einen 3D-Ansatz reduziert ein FinFET-Transistor den Leistungsverlust planarer Anordnungen drastisch. Der Kanals eines Transistors wird erhöht und das entsprechende Gate wird um ihn herum geschichtet. Die resultierende Struktur ermöglicht eine effizientere Kanalsteuerung, welche Schwellen- und Versorgungsspannungen verringert (Bild 1).

Im Vergleich zu planaren Transistoren macht die dynamische Leistungsaufnahme bei FinFETs aufgrund höherer Stiftkapazitäten den Großteil der gesamten Verlustleistung aus. Dies führt zu höheren dynamischen Leistungswerten.

Das Entwerfen von Designs mit FinFET-Technologie erfordert daher strengere Gestaltungsregeln, welche die spezifischen Anforderungen des FinFET-Prozesses berücksichtigen. Die neuen Regeln beschränken etwa die Synthese, physikalische Platzierungen und die Ausrichtung sowie die Optimierung.

Eine Leistungsanalyse auf RTL-Ebene ist nun obligatorisch. Im Entwicklungsprozess muss sie früh starten und in allen Phasen durchgeführt werden sowie mit anderen Entwurfskenngrößen wie Leistung und Fläche abgestimmt sein. Abgleiche zwischen RTL-Code, eingebettetem Softwarecode und Layout sind unerlässlich, um Probleme frühzeitig im Entwicklungsprozess zu erkennen und zu beheben.

Gibt es weitere Probleme, die zur Abweichung zwischen der geschätzten dynamischen Leistungsaufnahme vor der Produktion und den realen Werten beitragen?

Ein weiteres bedeutendes Problem ist, dass die Testdaten, mit denen das zu testende Design (DUT) stimuliert wird, funktional beschränkt sind. Heute nutzt die Elektronikindustrie in hohem Maße Benchmarks, um die Leistung und den Stromverbrauch neuer Designs zu messen. In den unterschiedlichen Industrien gibt es unterschiedliche Arten von Benchmarks:

In der Mobilfunkbranche bewertet ein sehr beliebter Benchmark namens AnTuTu die Leistung und den Stromverbrauch von Smartphones und Tablets. Car Chase, Manhattan und alle Kishonti-Tests sind die beliebtesten Benchmarks für GPU-lastige Designs. In der KI/ML-Branche misst die MLPerf-Benchmark-Suite die Leistung und den Stromverbrauch von ML-Software-Frameworks, ML-Hardware-Beschleunigern und ML-Cloud-Plattformen. Sie ist sowohl für Training als auch für Inferenz beliebt. Im Speicherbereich bietet die Messung von IOPs eine genaue Bewertung der Leistung/Genauigkeit für neue Geräte.

Es ist wichtig und erforderlich, die Benchmarks auch während der Validierung, die vor der Produktion stattfindet, durchzuführen. Erst durch die vollständige Sichtbarkeit aller internen Designstrukturen können Bereiche mit übermäßigem Stromverbrauch entdeckt und korrigiert werden – bevor das Silizium gefertigt wird.

Wie kann der Stromverbrauch bei der Validierung vor der Produktion gemessen werden?

Traditionell wurde der Stromverbrauch auf Gate-Ebene ermittelt, indem die Schaltaktivitäten des DUT während des Prozessierens von Testvektoren aufgezeichnet werden. Dieser Ansatz hat zwei Probleme.

Zum einen erfolgt die Prüfung sehr spät im Entwicklungsprozess. Obwohl die Abweichung zum realen Silizium nur innerhalb einer Größenordnung von 5 % liegt, gibt es nicht genügend Flexibilität, um Probleme innerhalb des Designs zu beheben. Ein besserer Kompromiss besteht darin, den dynamischen Stromverbrauch bereits auf RTL-Level zu bewerten. Dieser Ansatz führt zwar zu einer größeren Abweichung der Werte gegenüber denen des echten Produktes in einer Größenordnung von rund 15 %, bietet aber eine höhere Flexibilität für Designänderungen.

Zum anderen bilden Testvektoren nicht genau genug die realen Anwendungen des Produktes nach. Um eine genaue Leistungsabschätzung zu ermitteln, ist es wichtig, die Schaltaktivitäten des Zielsystems während des Durchführens von Leistungsbenchmarks, wie oben beschrieben, unter realen Arbeitsbedingungen so genau wie möglich zu erfassen.

Wie wird die Leistungsanalyse durchgeführt und wie erreichen Sie sie?

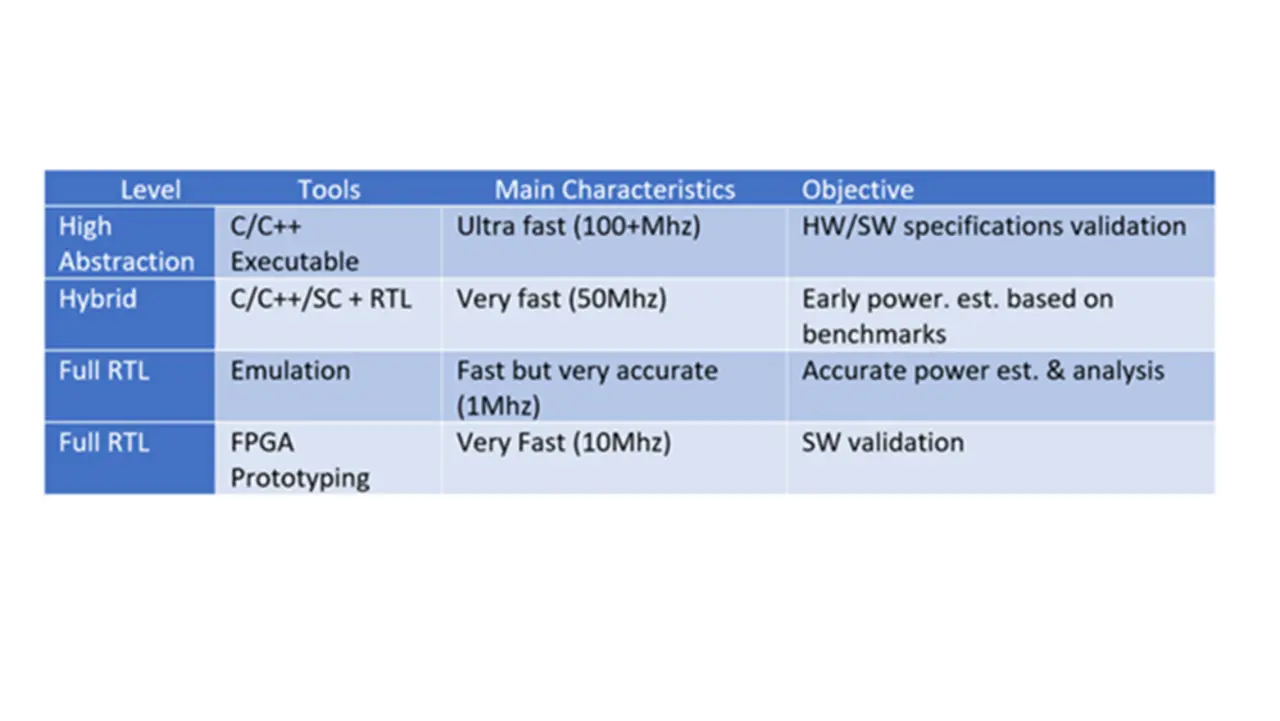

Offensichtlich kann die RTL-Simulation diese anspruchsvolle Aufgabe nicht mehr erfüllen. Benötigt wird ein hierarchischer Ansatz, der auf einer hohen Designabstraktionsebene beginnt und sich schrittweise bis hin zur RTL- und Gate-Ebene bewegt. Ein einziges Werkzeug reicht nicht mehr für alle Aufgabenbereiche aus. Stattdessen können mehrere Werkzeuge mit jeweils optimalen Einsatzbereichen die Leistungsbewertung und -optimierung beschleunigen, siehe Tabelle 1.

Im ersten Schritt wird das gesamte, auf einem hohen Abstraktionslevel in C/C++ beschriebene, DUT schnell anhand der Hardware-/Softwarespezifikationen validiert und der Stromverbrauch sehr grob geschätzt.

Als nächstes wird die Verlustleistung in einem Hybrid-Setup validiert. Dieses Setup besteht aus zwei Teilen. Ein Designteil wird auf hoher Abstraktionsebene beschrieben. Typisch beinhaltet dieser Teil Prozessorkerne und -Speicher wie z.B. ARM Fast Models. Dieser Teil wird auf einem Host-Server ausgeführt. Der andere Designteil wird als RTL Code modelliert, der auf einem Hardware-Emulator ausgeführt wird. Beide Teile sind über eine transaktionsbasierte Schnittstelle verbunden.

Während der Emulator mit einer Geschwindigkeit von wenigen Megahertz läuft, kann die Hybridkonfiguration Geschwindigkeiten im Bereich von 50 MHz erreichen. Das ist schnell genug, um Betriebssysteme wie Android oder Linux zu booten sowie Benchmarks und reale Anwendungen auszuführen.

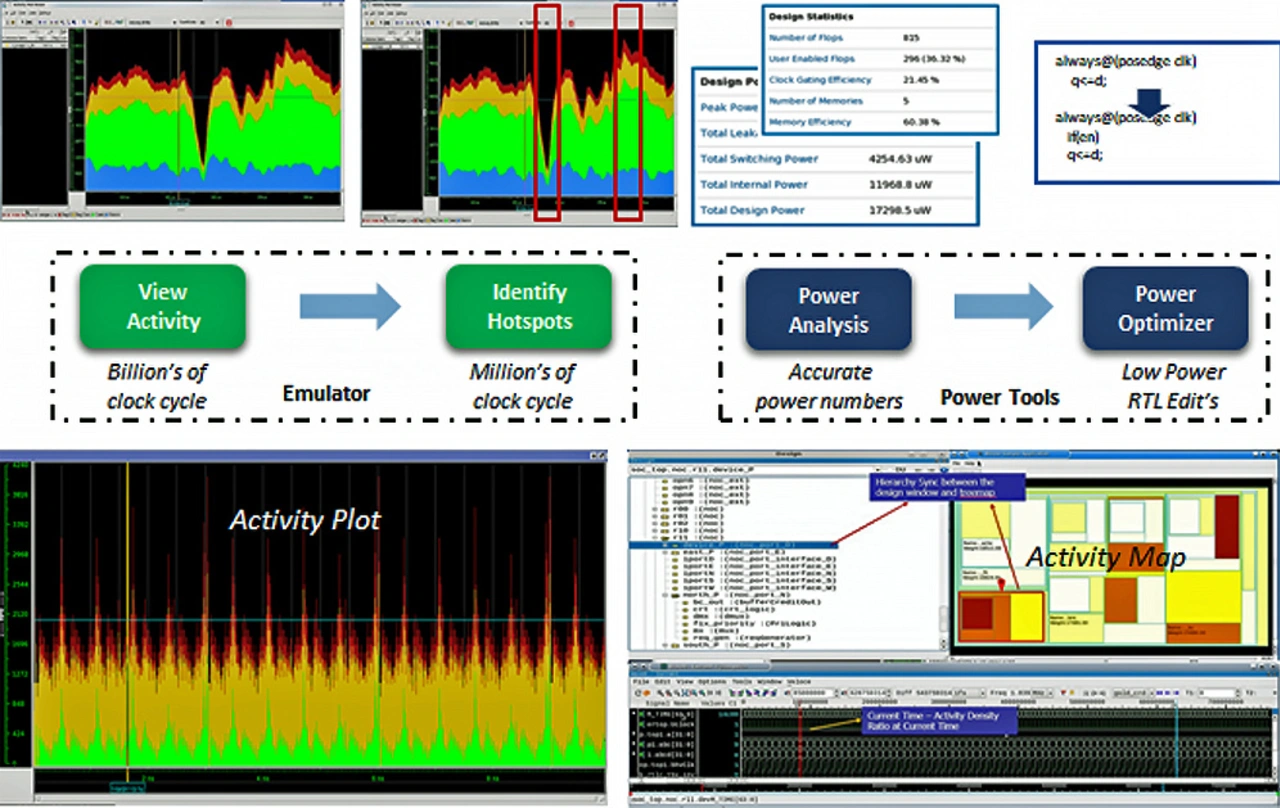

Dieses Setup bietet einen Ansatz, um für das gesamte Design den Stromverbrauch in relativ kurzer Zeit aufzuzeichnen. Durch das Mitschreiben der Schaltaktivität über einen langen Lauf von Milliarden von Taktzyklen kann das Designteam Hotspots von hohen und niedrigen Verlustleistungen in Bereichen von wenigen Millionen Taktzyklen erkennen. Ebenso kann das Team Designabschnitte mit hoher und niedriger Verlustleistung visuell darstellen.

Sobald Hotspots und kritische Bereich entdeckt wurden, kann das Team das vollständige RTL Design Modell verwenden und dadurch eine genaue und detaillierte Darstellung aller internen Designhierarchien erhalten. Durch Abgleich der ermittelten graphischen Protokolle mit dem im Design ausgeführten Softwarecode sowie mit dem RTL-Code kann sich das Team schnell auf Bereiche mit potenziellen Leistungsproblemen konzentrieren.

Es ist äußerst wichtig, alle Designaktivitäten während des kompletten Testzeitraumes zu aufzuzeichnen. Weil diese mangels Speicher nicht alle interne Designknoten zu jedem Zeitpunkt aufzeichnen, können FPGA-basierte Plattformen die Designaktivitäten nur zu definierten Zeitpunkten abtasten und protokollieren (Bild 2).

Ein SoC eines großen Halbleiterherstellers war auf einem Emulator abgebildet. Nachdem die Entwickler des SoC beobachtet hatten, wie der »Angry Birds« Benchmark auf diesem Emulator lief, fand bei besagtem großen Halbleiterhersteller ein Sinneswandel bezüglich des Profiling des Stromverbrauchs auf RTL-Level statt. Ich musste etwas lachen, als ich daran dachte, dass meine Tochter »Angry Birds« auf ihrem iPod spielt und diese große Halbleiterfirma dasselbe Programm auf einem Emulator betreibt.

Welche Entwicklungen können als Nächstes erwartet werden?

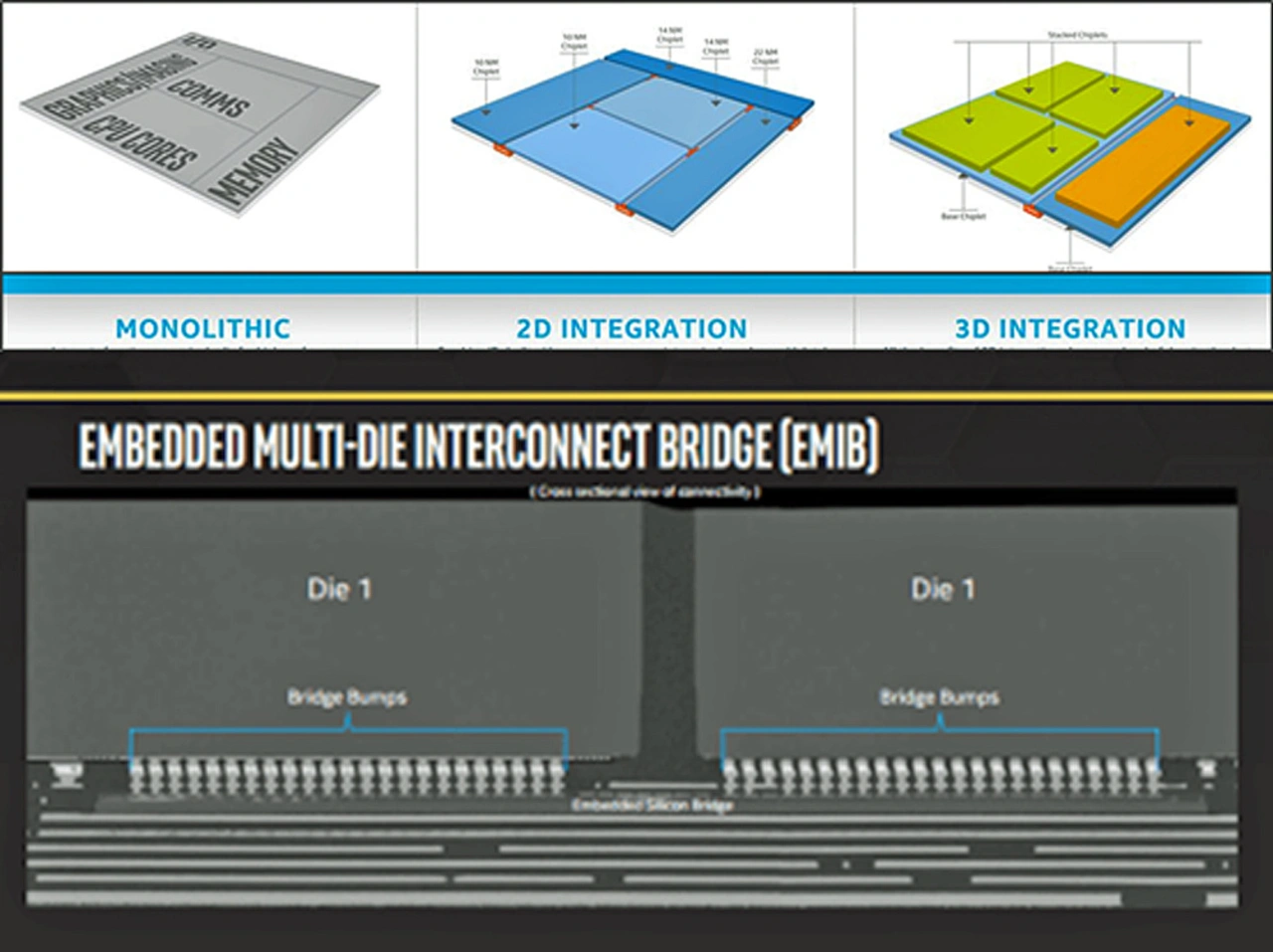

Ein neuartiger Designaspekt, der in der Phase vor der Produktion sehr komplex zu handhaben ist, betrifft Chiplets, Stapeln von Dies und 3D-IC-Verpackungen.

Meine bisherige Darstellung des Leistungsprofiling und der Analyse bezog sich auf ein monolithisches Design, bei dem alle Komponenten auf einem einzigen Chip kombiniert wurden. Was wir als nächstes betrachten müssen, sind Designs, die in einem komplexen 3D-IC-Paket implementiert werden. In vielen dieser Designs befinden sich CPU-Kerne auf einem Silizium Die, GPU-Kerne auf einem anderen, Speicher auf einem dritten usw. Diese kommunizieren untereinander über ein eingebettetes Multi Die-Verbindungssubstrat oder eine Brücke (EMIB) (Bild 3).

Das Durchführen von Leistungsprofiling und -analysen sowie von thermischen Analysen der Designhierarchie und des konfigurierbaren eingebetteten Software-Stacks, der auf mehrere Dies verteilt ist, ist komplex und anspruchsvoll.

Wir müssen eine modulare und hierarchische Zusammenstellung eines kompletten Designs entwerfen, welche auf einer bestimmte Hardware-Emulationsplattform abbildbar ist, und die Möglichkeiten entwickeln, hardware- und softwarebasierten Aktivitäten innerhalb der gesamte Designhierarchie zu suchen, zu identifizieren und zu debuggen.