Safety in Hinblick auf autonomes Fahren

Schnelle Kommunikation für redundante Systeme

Fortsetzung des Artikels von Teil 1

Hohe Verfügbarkeit in Fail-Operational-Systemen

Hohe Verfügbarkeit spielt bei Fail-Operational-Systemen eine wesentliche Rolle, vor allem in gemischten Systemen, bei denen sicherheitskritische und komfortrelevante Funktionen wie gerade dargestellt parallel existieren. Die Dual-Dual-Architektur sollte im Fehlerfall die Komfortfunktionen weitestgehend aufrechterhalten. Zu diesem Zweck hat Infineon eine Chipset-Architektur entwickelt und patentieren lassen, die einen Mikrocontroller mit einem Support-Sicherheits-Baustein kombiniert (in diesem Fall sichere Stromversorgung) und so für höhere Systemverfügbarkeit sorgt.

Jobangebote+ passend zum Thema

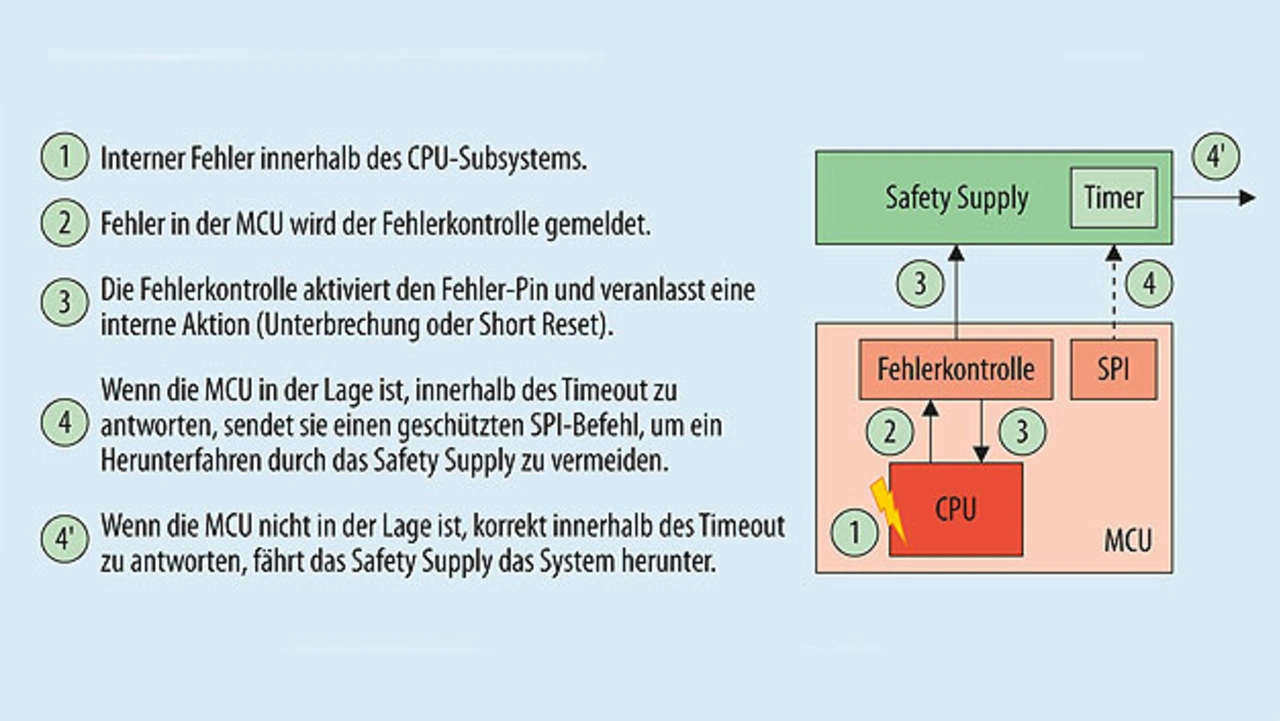

Bei derartigen Fail-Silent-Systemen werden die durch den Sicherheits-Mikro-controller erkannten kritischen Fehler an einem „Error Pin“ angezeigt. Der externe, unterstützende Safety-Baustein überprüft diesen Error Pin und fährt das System im Falle eines vorliegenden Fehlerzustands kontrolliert herunter. In Bild 3 ist zu sehen, wie das System sicher auf die Fehlerbedingung reagieren kann. Der Prozess ist sicher, weil die Fehlerbedingung an einen externen Monitoring-Baustein berichtet wird. Damit wird die Verfügbarkeit des Systems erhöht, während die Fehlerreaktion des Mikrocontrollers individuell konfiguriert werden kann.

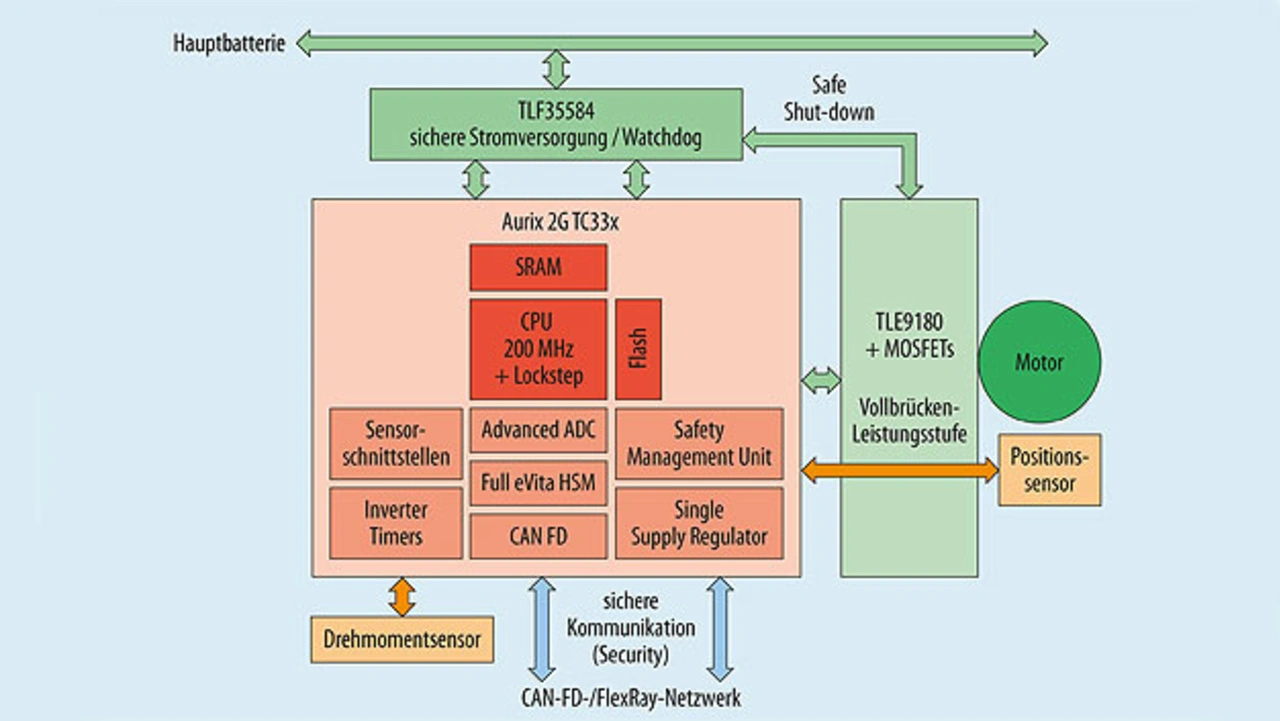

Mit dieser von Infineon vorgeschlagenen Methode werden die Vorzüge der Safety Management Unit (SMU) des Aurix genutzt. Denn mittels der SMU können die Reaktionen für jede Fehlerquelle (Interrupt, NMI, CPU Core Reset, CPU Core Idle, SOC Reset) einzeln konfiguriert werden. Bild 4 zeigt ein Fail-Silent-EPS-Design, das einen Aurix-Mikrocontroller mit dem Safety-Supply-Baustein TLF35584 kombiniert und so eine hohe Verfügbarkeit gewährleistet.

Implementierung eines Fail-Operational-Systems

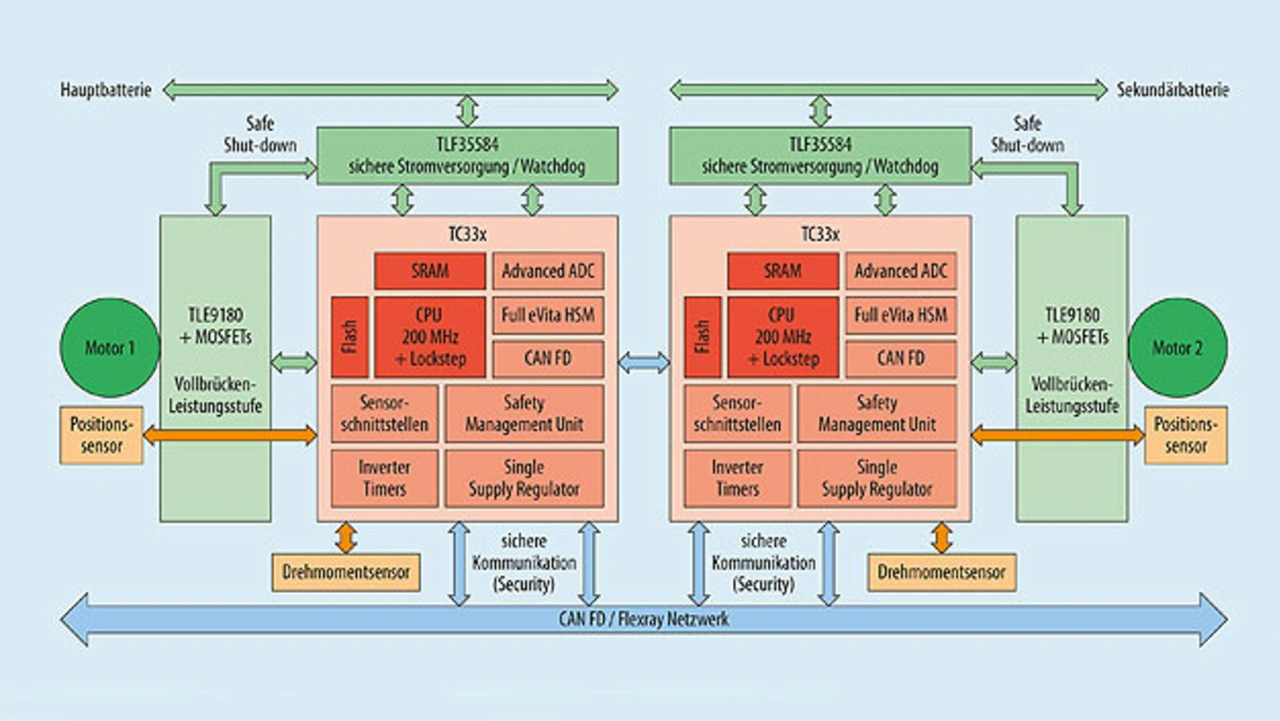

Die Implementierung von Fail-Operational-Systemen erfordert eine gewisse Redundanz – verbunden mit Herausforderungen bezüglich Platzbedarf, Leistungsaufnahme und Kosten.

Die neue Aurix-Generation steht in 12 mm × 12 mm (BGA196) und 14 mm × 14 mm großen Gehäusen (TQFP100) zur Verfügung. Das bedeutet, dass zwei BGA196-Gehäuse etwa um 27 Prozent weniger Board-Fläche als zwei TQFP100-Versionen benötigen. Darüber hinaus unterstützt der integrierte Spannungsregler der MCU eine Switch-CAP-DC/DC-Topologie, womit der Platz und die Kosten für bis zu zwei externe MOSFETs und Induktoren eingespart werden können. Mit dieser Topologie lässt sich die Leistungsaufnahme im Betrieb halbieren.

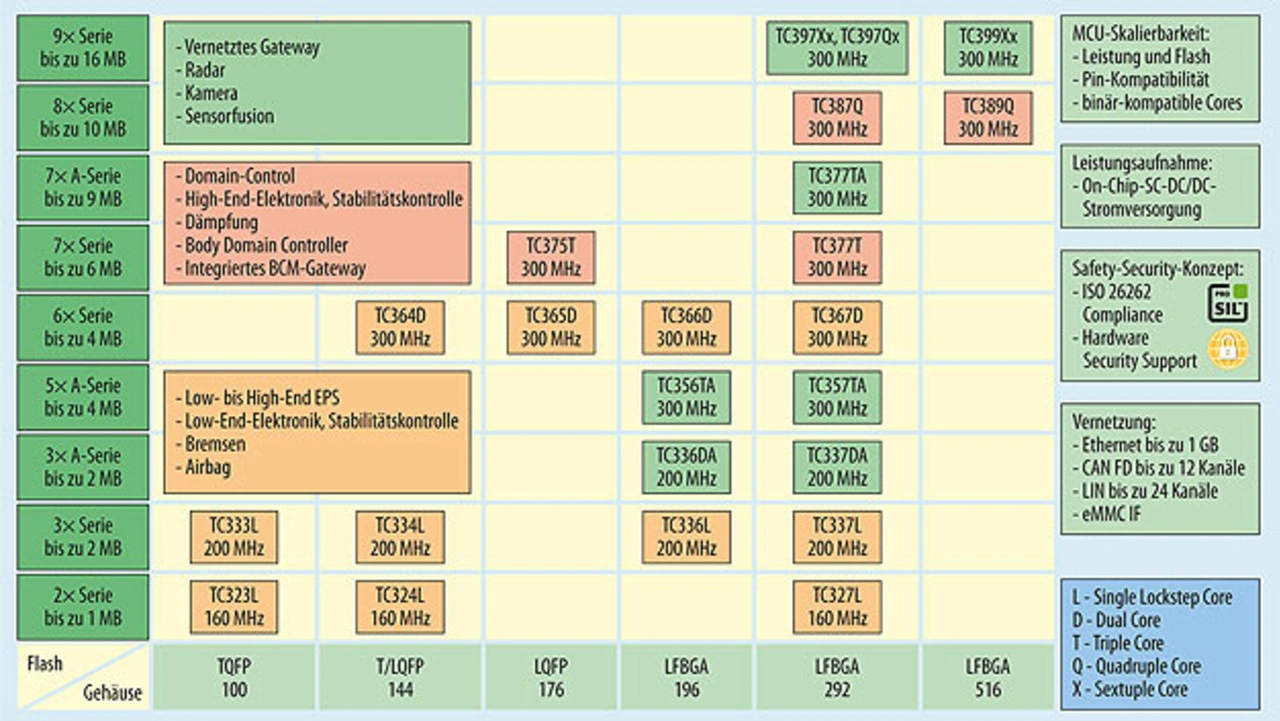

Wie bereits erwähnt lässt sich eine asymmetrische Architektur mit einem größeren und einem kleineren, preiswerteren Mikrocontroller nutzen, um die Kosten für eine Fail-Operational-Implementierung zu senken. Die Skalierbarkeit und Kompatibilität der Aurix-Familie ermöglicht den Einsatz eines High-End- und Low-End-Derivates im gleichen Design (Bild 5). Das vereinfacht das Design, weil das Safety-Konzept, die Latenzzeiten und andere Design-Parameter beibehalten werden. Außerdem vereinfacht der Einsatz eines Herstellers die Versorgungskette, reduziert den Entwicklungs- und Qualifizierungsaufwand sowie die Kosten für die Software-Entwicklungswerkzeuge.

Darüber hinaus kann mit den Mikrocontrollern die Verfügbarkeit von Fail-Operational-Systemen erhöht werden. Alle Aurix-Mikrocontroller haben das gleiche Safety-Konzept und nutzen fortschrittliche Schutzmechanismen wie Locksteps, Error-Correction-Code-geschützte Speicher sowie die bereits erwähnte Safety Management Unit.

Mit den Architektur-Optimierungen in der neuen Generation wird die Verfügbarkeit nochmals verbessert, wobei die Unabhängigkeit zwischen den Cores erhöht wird. Somit können Cores nun separat in den Reset-, Sent- oder Idle-Status versetzt werden. D.h., dass ein fehlerhafter Core für sich allein einen Reset ausführen kann, während die anderen Cores normal weiterarbeiten. Die Cores haben direkten Zugriff auf ihre privaten Ressourcen. Das erhöht die Verfügbarkeit nicht nur in Fail-Operational-Systemen beim autonomen Fahren (L3/L4), sondern auch auf L2-Ebene, wo Systeme nur teilweise redundant sein müssen.

Optimiert für maximale Sicherheit

Mit ihrer High-Performance-Architektur und bis zu sechs Cores sowie Schnittstellen-, Security- und Safety-Funktionen eignet sich die Aurix-Familie für vielfältige Applikationen in der Automobil- und Industrieelektronik. Insbesondere Ansteuerungen in Hybridantrieben und Umrichtern, das Batteriemanagement oder Spannungsregler profitieren von der neuen Architektur. Außerdem sind die Aurix-TC3xx-Mikrocontroller ideal für Safety-kritische Anwendungen, vom Airbag über Brems- und Lenkungs-Applikationen bis hin zu Sensor-basierten Systemen mit Radar- oder Kamera-Technologien. Auch Domain-Control- und Datenfusions-Anwendungen beim autonomen Fahren mit höheren Automatisierungs-Levels werden adressiert.

Die TC3xx-Familie ist skalierbar (Bild 6), mit Flash-Größen von 1 MB bis 16 MB sowie integriertem RAM-Speicher von 150 KB bis mehr als 6 MB. Während die bisherige Generation (TC2xx) über bis zu drei Cores verfügte, bietet die TC3xx-Multicore-Architektur bis zu sechs TriCore-CPUs, jede mit einer Taktfrequenz von 300 MHz.

Autonomes Fahren erfordert eine schnellere und dennoch extrem sichere Konnektivität bzw. Kommunikation zwischen den kritischen Steuereinheiten, beispielsweise zwischen dem zentralen Antriebsrechner und der Lenkung oder dem Bremssystem. Vor diesem Hintergrund wurden die Kommunikations- und Security-Funktionen mit der neuen Aurix-Generation nochmals verbessert: So bieten die Controller Schnittstellen für CAN FD, FlexRay und optional Gigabit-Ethernet. Ein Evita Hardware Security Module (HSM) ermöglicht die asymmetrische Verschlüsselung gemäß ECC256 und SHA256, Message-Authentifizierung zwischen verschiedenen ECUs und das sichere Booten zum Schutz vor Schad-Software.

Für ASIL D

Die TC3xx-Mikrocontroller unterstützen die Umsetzung hin zum automatisierten/autonomen Fahren und zur Elektromobilität. Dafür bieten sie die richtige Mischung aus Rechengeschwindigkeit, Safety- und Security-Funktionen. Mit bis zu vier Lockstep-Cores bei maximal sechs Cores wird eine hohe Rechenleistung für die Safety-Implementierung gemäß ISO 26262 erreicht: Bis zu 2400 DMIPS stehen für Applikationen gemäß ASIL D zur Verfügung, während es bei der Vorgänger-Generation noch 740 DMIPS waren.

Die neue Aurix-TC3xx-Familie ist rückwärtskompatibel zur TC2xx-Generation. Erste Entwicklungsmuster des Lead-Bausteins TC39x mit 300 MHz, 16 MB Flash-Speicher und 6,8 KB SRAM werden in BGA516- und BGA292-Gehäusen verfügbar sein.

Die Autoren

| Lassaad Ben Cheikh |

|---|

| arbeitet als Product Marketing Manager bei Infineon Technologies. |

| Dr. Andre Roger |

|---|

| ist Lead Principal System Architect bei Infineon Technologies. |

- Schnelle Kommunikation für redundante Systeme

- Hohe Verfügbarkeit in Fail-Operational-Systemen