Ethernet-PHY mit Hardwaresynchronisation

Höhere Reichweite für Kfz-Radarsysteme

Ethernet-PHY-Transceiver können die Genauigkeit, Effizienz und Reichweite bestehender Kfz-Radararchitekturen verbessern. Durch Vereinfachung der ADAS-Architekturen und Verringerung des Verarbeitungsaufwands für den Software-Stack lassen sich die Anforderungen der OEMs und Tier-1-Zulieferer erfüllen.

Die Fahrerassistenzsysteme in modernen Kfz werden mit immer mehr Radarsensoren ausgestattet. Zudem unterstützen verschiedene Radarsysteme mittlerer bis großer Reichweite das autonome Fahren bis Level 2 nach Definition der Society of Automotive Engineers (SAE). Diese Kombination von Radar-Lösungen erzielt den für ein sicheres Fahren notwendigen Erfassungsbereich in Fahrtrichtung und hat sich bisher als ausreichend erwiesen. Die Anforderungen der Automobilhersteller auf diesem kostensensiblen Markt entwickeln sich jedoch weiter, sodass ein Bedarf an neuen Designlösungen entsteht.

Bild 1 veranschaulicht, wie Frontradarsysteme andere Fahrzeuge detektieren und die Distanz zu ihnen messen.

Bei Fahrzeugen der nächsten Generation, die die Autonomie-Level 2 und höher unterstützen, wird ein Wettbewerb darum entstehen, die verschiedenen Autonomie-Level zu für die Konsumenten immer niedrigeren Kosten zu erreichen, woraus eine Nachfrage nach optimierter Hard- und Software resultiert.

Moderne Architekturen – wie ist der heutige Stand?

Die Sensorarchitekturen autonomer Fahrzeuge richten sich danach, welchen Autonomiegrad das jeweilige Automobil erzielt. Für das autonome Fahren ist es notwendig, in Echtzeit große Mengen an Sensordaten zu erfassen und zu verarbeiten. Sind die Sensoren zueinander synchronisiert, lässt sich aus den Sensordaten mithilfe spezieller Software ein virtuelles Abbild der Szenerie vor dem Fahrzeug erstellen, und mithilfe dieses virtuellen Abbilds kann der ADAS-Mikrocontroller den richtigen Fahrweg berechnen und etwaige Hindernisse umfahren.

Radarsysteme detektieren Objekte, indem sie elektromagnetische Wellen aussenden, deren Reflexionen sie anschließend empfangen und auswerten. Das System misst die Zeit zwischen dem Aussenden und dem Empfang der Wellen und kann hieraus die Entfernung zum detektierten Objekt berechnen. Die Radarsensor-Konstellation eines typischen Fahrzeugs der Autonomiestufe 2 oder höher umfasst drei bis fünf Radarsensoren mittlerer Reichweite (bis 150 m) sowie ein einzelnes Frontradar großer Reichweite für Distanzen bis 250 m.

Alle diese Radarsysteme schicken fortlaufend Daten, die in Frames gegliedert sind, an das zuständige elektronische Steuergerät. Ein Software-Stack, für dessen Entwicklung die Fahrzeughersteller bzw. Tier-1-Zulieferer zuständig sind, übernimmt dann die Synchronisation der Frames zum zentralen Takt, was einen erheblichen Verarbeitungsaufwand verursacht. Der große Datenbedarf verschärft somit die Anforderungen, die in Sachen Leistungsfähigkeit, Strombedarf, Platzbegrenzung und Kosten an den Zentralprozessor gestellt werden.

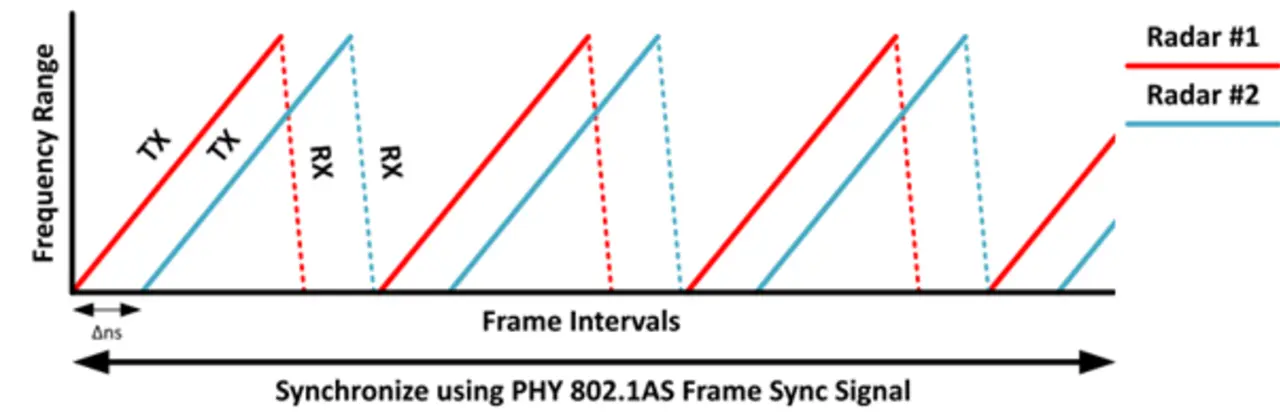

Erfolgt die hardwaremäßige Synchronisation der Frames auf dem Physical Layer (PHY) des TCP/IP-Protokollstapels (Transmission Control Protocol/Internet Protocol), lassen sich die Nachbearbeitungs-Anforderungen an den zentralen ADAS-Mikrocontroller erheblich reduzieren. Binnen Nanosekunden kann der Ethernet-PHY-Transceiver DP83TC817S-Q1 von TI Radar-Frames von zwei oder mehr Radarsystemen auf der Hardware-Ebene sowohl im Zeit- als auch im Frequenzbereich synchronisieren. Bild 2 verdeutlicht dieses Konzept.

Vorteile der Hardware-Synchronisation für das autonome Fahren

Die Fahrzeughersteller nutzen Ethernet als Kommunikations-Rückgrat umfangreicher Systeme in Zonen-, Domänen- und Hybridarchitekturen. In existierenden ADAS-Architekturen fungiert Ethernet zudem als Kommunikationsmedium zwischen den Radarsystemen und dem zentralen Rechnersystem. In den jeweiligen Radar-Subsystemen angeordnet, senden die Ethernet-PHYs Datenframes an den zentralen ADAS-Rechner.

Die anspruchsvollen Features des DP83TC817S-Q1 ermöglichen das Regenerieren des ankommenden zentralen Takts mithilfe des Precision Time Protocol (PTP). Der integrierte Ein/Ausgang des Bausteins triggert den Frame des Radarsystems und erzeugt so einen synchronisierten Radar-Frame für mehrere Radar-Subsysteme und überträgt diesen an das Radar-Steuergerät. Anschließend misst der DP83TC817S-Q1 den Frequenzversatz des empfangenen Radar-Frames, um im nächsten Framezyklus den Frequenz-Offset zu korrigieren und die nachfolgenden Frames im Frequenzbereich zu synchronisieren. Die Synchronisation im Zeit- und Frequenzbereich sorgt dafür, dass der zentrale ADAS-Mikrocontroller die aus den Sensoren extrahierten Daten mit geringem Nachbearbeitungs-Aufwand nutzen kann, und ergibt zusätzlich eine höhere Genauigkeit als die softwaremäßige Synchronisation.

Der DP83TC817S-Q1 reduziert also den Verarbeitungsaufwand für den ADAS-Mikrocontroller, sondern verkürzt auch die Entwicklungszyklen und steigert die Leistungsfähigkeit des kompletten Radarsystems, sodass sich auch solche Architekturen realisieren lassen, die früher aus Kostengründen nicht in Frage kamen. Die Kombination dieser Eigenschaften erlaubt somit kürzere Zykluszeiten für die kommende Fahrzeuggeneration mit Autonomie-Level 2 und darüber.

Nach Unterlagen von Texas Instruments