Erweiterte EPR-Standards

Mehr Leistung in GaN-USB-C-Adaptern und -Ladegeräten

Der neue USB-PD Extended Power Range (EPR)-Standard ermöglicht die Entwicklung universeller AC/DC-Adapter für viele verschiedene Anwendungszwecke: von Smartphones über Gaming-Laptops bis hin zu Elektrowerkzeugen und sogar E-Bikes. Das bringt aber neue Herausforderungen mit sich.

Die Einführung des USB PD 3.1-Standards [1] ermöglicht USB-C-Adapter und -Ladegeräte mit Leistungen bis zu 240 W. Allerdings entstehen durch den breiten Ausgangsspannungsbereich von 5 bis 48 V neue Herausforderungen für die derzeit verwendeten Wandler-Topologien: Diese müssen gewisse Anforderungen an die elektromagnetische Verträglichkeit, die Blindleistungskompensation, die Standby-Leistung und den mittleren Wirkungsgrad erfüllen. Zusätzlich legen Endkunden immer mehr Wert auf kompakte Bauformen, die natürlich auch eine höhere Leistungsdichte erfordern.

Für einen breiten Ausgangsspannungsbereich kommen derzeit die folgenden zwei Schaltungstopologien infrage:

- PFC+Flyback: Die Topologie ist äußerst flexibel, was den Eingangs- und Ausgangsspannungsbereich betrifft. Die Größe des Transformators limitiert jedoch die Leistungsdichte. Außerdem erfordert der Schalter eine höhere dielektrische Festigkeit und die Schaltfrequenz wird durch die nicht recyclebare Leakage-Energie begrenzt. Das Problem kann durch den Active-Clamp-Flyback behoben werden, dennoch schränkt die Größe des Transformators das Design bezüglich des Formfaktors ein.

- PFC+LLC+Buck: Der PFC+LLC kann sehr kompakt und effizient sein, ist aber an anderer Stelle äußerst begrenzt: Um einen breiten Ausgangsspannungsbereich zu erreichen, muss zusätzlich ein Abwärtswandler eingesetzt werden, was zu einer aufwendigen und teuren Systemlösung führt.

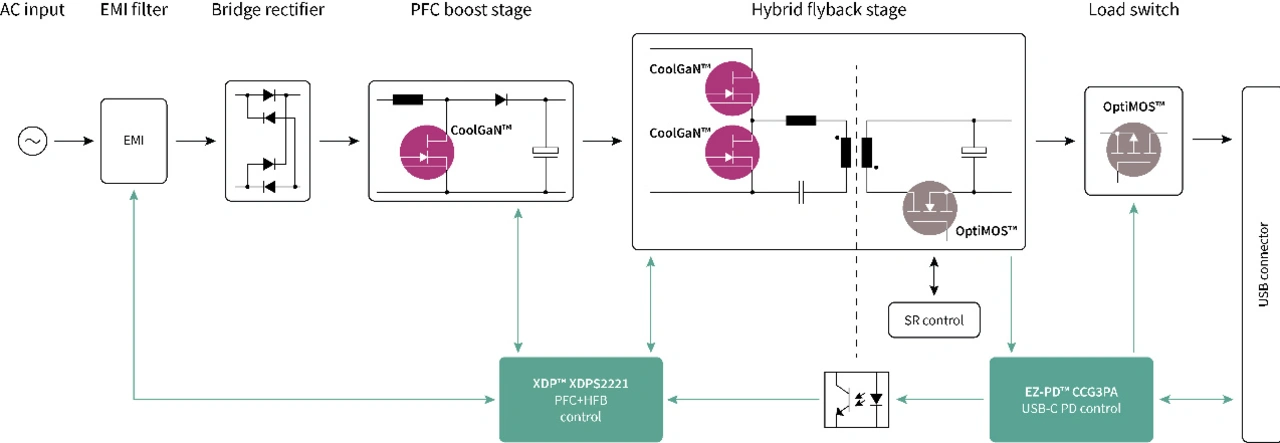

Um die höchstmögliche Leistungsdichte zu erreichen, schlägt Infineon eine innovative Wandler-Architektur (Bild 1) vor: Sie umfasst eine AC/DC-PFC-Aufwärtsstufe und einen DC/DC-Hybrid-Flyback (HFB) [2] in Kombination mit synchroner Gleichrichtung am Ausgang [3][4]. Das Ergebnis ist eine PFC+Hybrid-Flyback-Topologie. Die Architektur ermöglicht eine hohe Leistungsdichte mit hoher Leistungseffizienz – die zudem internationale regulatorische Standards wie EU CoC Version 5 Tier 2 und DoE Level VI erfüllt. Darüber hinaus unterstützt die Architektur eine effektive Steuerung der weiten Ausgangsspannung für den neuesten USB PD ERP Standard V3.1. Im Vergleich zu herkömmlichen Flyback-Varianten kann die Größe des Transformators deutlich reduziert werden.

Die Wandler-Architektur im Detail

Der XDP XDPS2221 integriert einen AC/DC-Leistungsfaktorkorrekturregler (PFC) mit einem DC/DC-HFB-Regler, auch bekannt als asymmetrische Halbbrücke (AHB), in einem Gehäuse. Durch den abgestimmten Betrieb der beiden Stufen können die Effizienzanforderungen des erweiterten EPR-Standards leicht erfüllt werden. Darüber hinaus ermöglicht die zusätzliche Integration der Gate-Treiber und einer 600-V-Hochvolt-Start-up-Zelle für die initiale IC-Spannungsversorgung ein sehr kompaktes Design. Basierend auf einer neuen Zero-Voltage-Switching (ZVS) HFB-Topologie in Verbindung mit GaN-basierten Bauteilen bietet die Architektur erstklassige Effizienz bei verschiedenen Netz-/Lastbedingungen. Aufgrund dieser Merkmale und der inhärenten Topologievorteile, wie ZVS und resonante Energieübertragung zur Reduzierung der Transformatorgröße, können Systemdesigns mit XDP XDPS2221 sehr hohe Leistungsdichten erreichen.

Darüber hinaus bietet das neue Combo-IC einen synchronen Betrieb zwischen PFC und HFB-Burst-Mode-Betrieb für die geringstmögliche Leerlaufeingangsleistung im Standby-Modus. Die quasi-resonante Multimode-PFC-Stufe ist mit einer automatischen PFC-Aktivierungs-/Deaktivierungsfunktion sowie einer adaptiven PFC-Busspannungsregelung ausgestattet. Dadurch wird die Effizienz bei mittlerer und geringer Last maximiert. Optional kann die integrierte PFC-Funktion auch deaktiviert werden, sodass der Einsatz eines externen PFC-Controllers möglich ist.

Die Hybrid-Flyback-Stufe ist stromgeregelt, was eine robuste Regelung der Ausgangsspannung und ein schnelles dynamisches Lastverhalten ergibt. Um den ZVS-Betrieb unter allen Bedingungen zu ermöglichen, verfügt die Hybrid-Flyback-Stufe zudem über eine ZVS-Impulseinfügung, die im diskontinuierlichen Betriebsmodus eine Querleitung der Body-Diode verhindert. Darüber hinaus können beim XDP XDPS2221 die Parameter über eine grafische Benutzeroberfläche einfach konfiguriert werden, um die Systemleistung zu optimieren.

Der eingebettete digitale Kern des XDP XDPS2221 ermöglicht einen raffinierten Regelungsalgorithmus, mit dem die Leistung der beiden Leistungsstufen optimiert werden kann. Um eine optimale Systemeffizienz und reduzierte Standby-Leistung zu erreichen, wird die PFC-Stufe nur in Abhängigkeit von den Eingangs- und Ausgangsspannungsbedingungen sowie den Lastbedingungen aktiviert. Zusätzlich trägt eine Modulation der Busspannung in Abhängigkeit vom Arbeitspunkt des HFB dazu bei, den Wirkungsgrad weiter zu erhöhen.

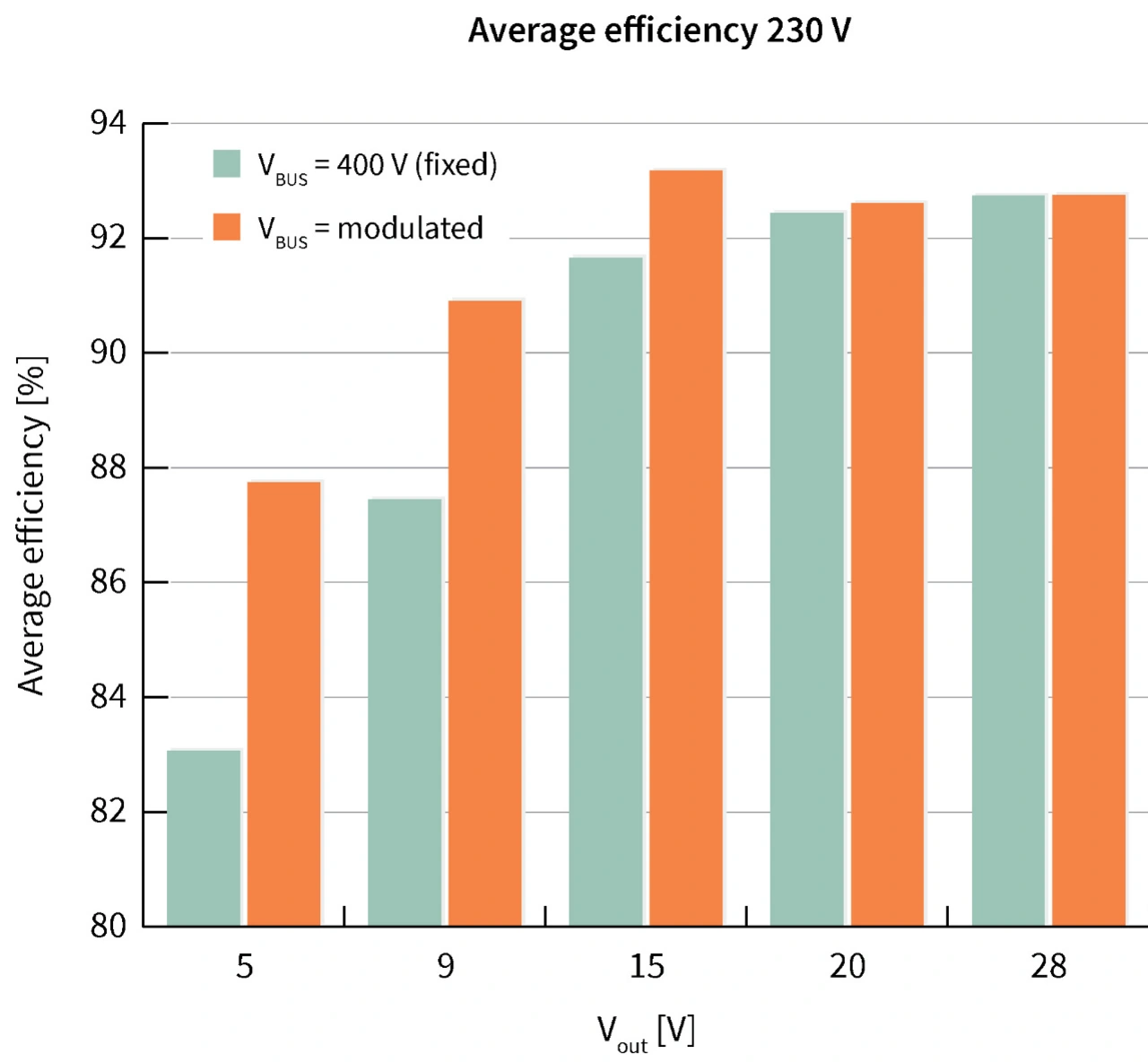

Um die höchste Leistungsdichte zu erreichen, ist es erstrebenswert, den Wirkungsgrad bei maximaler Last zu optimieren, da dies in der Regel der ungünstigste Fall für die Leistungsverluste ist. Mit der neu implementierten PFC-Modulation ist es jetzt möglich, die Effizienz auch für die niedrigeren Ausgangsspannungspegel zu verbessern. Bild 2 zeigt den durchschnittlichen Vier-Punkte-Wirkungsgrad mit PFC-Modulation und mit fester PFC-Ausgangsspannung.

Durch die Modulation kann die Effizienz bei der niedrigsten Ausgangsspannung um fast 5 Prozent verbessert werden. Neben der leistungsstarken Multimode-PFC, die im Critical-Conduction-Mode (CRM) mit Valley-Switching-Betrieb arbeitet, sowie der hocheffizienten Multimode-HFB-Topologie enthält der Controller eine 600-V-Startzelle, mit der das System gestartet werden kann, bevor die Hilfsspannung die Versorgung übernimmt.

Der eingebettete digitale Kern unterstützt die Feinabstimmung des Systems durch konfigurierbare Parameter. Auf diese Weise können Entwickler sehr flexibel auf unterschiedliche Leistungspegel und Anwendungsanforderungen reagieren. Zusätzlich können Schaltanwendungen mit sehr hohen Frequenzen unterstützt werden, wobei die Nullspannungsschaltung (ZVS) und die Nullstromschaltung (ZCS) die Verwendung eines Planartransformators ermöglichen.

Prototyp

Um die Vorteile der Architektur zu demonstrieren, wurde ein 140-W-Prototyp (28 V/5 A) entwickelt (Bild 3). Für die Umsetzung wurden zweilagige Leiterplatten und Standardmagnetkerne verwendet, um niedrige Systemkosten zu erreichen.

Die Wirkungsgradergebnisse sind in Bild 4 (VAC = 115 V, Bildergalerie) und Bild 5 (VAC = 230 V, Bildergalerie) dargestellt. Die Ergebnisse decken den Ausgangsspannungsbereich von 5 bis 28 V mit einer Lastvariation von 10 bis 100 Prozent ab. Zudem erreicht die Schaltung einen Spitzenwirkungsgrad von 95 Prozent bei maximaler Last – sie erreicht jedoch auch bei minimaler Last eine Effizienz von über 80 Prozent.

Daraus ergibt sich ein Vier-Punkte-Durchschnittswirkungsgrad (Bild 6, Bildergalerie). Mit dem integrierten hoch entwickelten Regelalgorithmus zwischen PFC und HFB können die CoC Tier 2-Grenzwerte leicht erreicht werden.

Bild 7 (Bildergalerie) zeigt die Standby-Verluste im Eingangsspannungsbereich von 90 bis 264 V. Durch den synchronen PFC und HFB-Burst-Mode-Betrieb konnten die Standby-Verluste im gesamten Eingangsspannungsbereich auf unter 70 mW gesenkt werden.

Hybrid Flyback

Schlussfolgerungen und künftige Entwicklungen

Die Kombination von HFB und PFC-Boost mit der neuen ausgeklügelten Regelungsstrategie verdeutlicht, dass USB-PD EPR-Adapter sowohl bei geringer als auch bei maximaler Last hohe Wirkungsgrade erreichen können. Der hochintegrierte Controller mit kombiniertem PFC- und HFB-Betrieb ermöglicht ein einfaches Design bei geringer Größe, das gleichzeitig eine hohe Leistungsdichte ermöglicht. Die Vorteile der neuen Architektur konnten mit einem 140-W-Prototyp demonstriert werden: Er erreichte einen hohen Spitzenwirkungsgrad von 95 Prozent und eine Leistungsdichte von 22,67 W/Zoll3 auf einer kostengünstigen zweilagigen Leiterplatte.

Quellen

- [1] »Universal Serial Bus Power Delivery Specification, revision 3.1,« www.usb.org, 26 May 2021

- [2] Medina-Garcia A., Schlenk M., Morales D.P., Rodriguez N., »Resonant Hybrid Flyback, a New Topology for High-Density Power Adaptors,« Electronics, vol. 7, 363,2018, DOI: 10.3390/electronics7120363.

- [3] B. Talesara, Jayapal R., Susheel B., S. N. Rao, and B. K. Singh, »Efficiency enhancement of flyback converter using synchronous rectification,« 2015 Annual IEEE India Conference (INDICON), New Delhi, 2015, pp. 1-5, DOI: 10.1109/INDICON.2015.7443380.

- [4] G. Jeong, »High efficiency asymmetrical half-bridge flyback converter using a new voltage-driven synchronous rectifier,« IET Power Electronics, vol. 3, no. 1, pp. 18-32, Jan. 2010. Available: 10.1049/iet-pel.2008.0306.