Gigabit-Schnittstellen im Boardtest

Mit dem integrierten FPGA testen

Fortsetzung des Artikels von Teil 4

USB-3.0-Testablauf im Detail

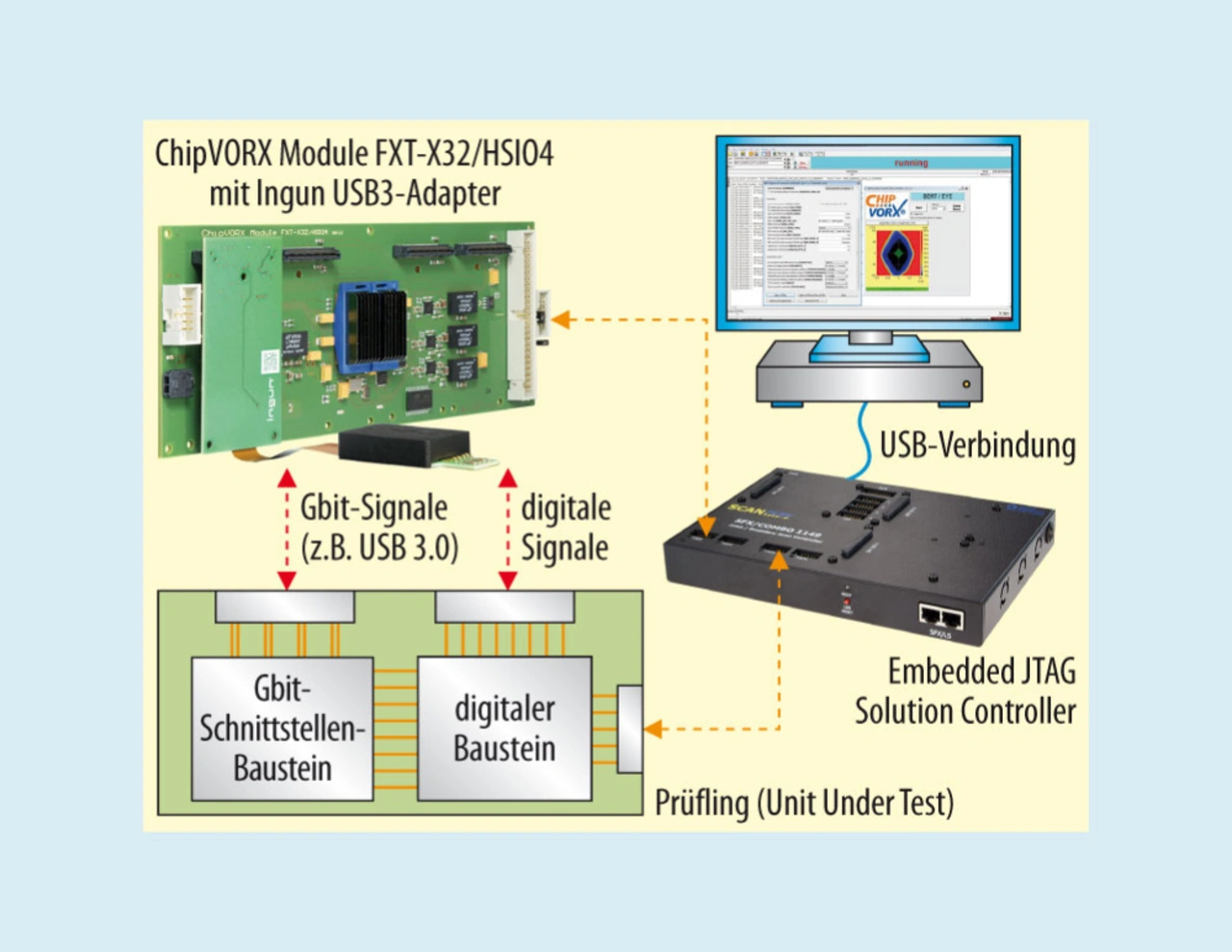

Bei dem Testszenario (Bild 4) muss eine Aktivierung sowohl der zu testenden Baugruppe als auch des ChipVORX-Moduls erfolgen. Die Standarddefinitionen der meisten Hochgeschwindigkeits-Schnittstellen enthalten die Möglichkeit eines Loopback-Modes. Das heißt, von außen kann die Schnittstelle in einen Zustand gebracht werden, bei dem alle ankommenden Bitmuster wieder in gleicher Art und Weise zurückgesendet werden. Dieser Loopback-Modus kann mit speziellen Kommandos auf den untersten Protokollschichten der jeweiligen Schnittstelle konfiguriert werden, sodass keinerlei zusätzliche Software- oder Firmware-Voraussetzungen auf der zu prüfenden Baugruppe geschaffen werden müssen. Diese externe Konfiguration übernehmen die ChipVORX-BERT-IPs völlig automatisiert. Die beim Testablauf vorgesehene Baugruppen-Firmware für den Auslieferungszustand genügt in den meisten Fällen zum notwendigen Aktivieren und Vorkonfigurieren der Schnittstelle und der Baugruppe, sodass vom extern angeschlossenen ChipVORX Module FXT-X32/HSIO4 über die USB-Schnittstelle ein Loopback-Test vorgenommen werden kann.

Der Bit-Error-Test erfolgt in zwei Schritten. Im ersten Schritt wird der Loopback-Mode der jeweiligen Schnittstelle durch die ChipVORX-IP aktiviert und im zweiten Schritt erfolgt der eigentliche Bit-Error-Test. Dabei kann hier ebenfalls zwischen einem einfachen Bit-Error-Rate-Test im Mittelpunkt, einem statistischen Augendiagramm oder einer Multipoint-Messung mit Hilfe des im System Cascon vorhandenen automatischen Testgenerators ausgewählt werden.

Beim Erstellen eines Multipoint-BER-Tests hilft ebenfalls der im System Cascon integrierte automatische Testgenerator. Durch die Möglichkeit ein zuvor aufgenommenes statistisches Augendiagramm einzublenden, kann die Definition der Messpunkte anhand dieses »Gutmusters« erfolgen. In jedem Messpunkt können dabei beliebig viele Bits übertragen werden. Für die automatisierte Pass/Fail-Auswertung werden zudem die maximale Anzahl der erlaubten Fehler-Bits ausgewertet. Durch zusätzliche Template-Vorlagen können einfache Messpunktschemen im Diagramm gesetzt werden, sodass nicht jeder Messpunkt einzeln per Hand gesetzt werden muss. Nach der Definition der Messpunkte wird anschließend der Test anhand dieser Parameter vollautomatisch generiert und kann sofort ausgeführt werden.

Ein weiterer Vorteil der ChipVORX-IP für den Bit-Error-Rate-Test ist die mögliche Online-Konfiguration während des Testablaufes. Gerade für die optimale Parameterfindung während der ersten Inbetriebnahme einer Baugruppe kann es sinnvoll sein, bestimmte Parameter der Hochgeschwindigkeits-Schnittstelle zu optimieren. Durch ein zusätzliches Fenster können die meisten der im FPGA veränderbaren Parameter direkt zur Laufzeit geändert und die Auswirkungen mit kurzer Verzögerung im Diagramm verfolgt werden.

Jobangebote+ passend zum Thema

Quellen

[1] IEEE Std.1149.1-2013, Standard Test Access Port and Boundary Scan Architecture.

Die Autoren

Sven Haubold studierte von 1996 bis 2000 Elektrotechnik an der FH Jena. Er entwickelt und betreut als Senior Engineer bei Göpel Electronic im Geschäftsbereich »Embedded JTAG Solutions« verschiedene Hardware-Produkte sowie kundenspezifische Test- und Prüflösungen.

Hosea Busse studierte Elektrotechnik an der FH Westküste. Er ist als Applikationsingenieur bei Göpel Electronic und unter anderem verantwortlich für Organisation und Durchführung professioneller Trainings zu Embedded System Access.

- Mit dem integrierten FPGA testen

- Integrierte Testverfahren

- Embedded-Bit-Error-Rate-Test mit ChipVORX

- Praktische Umsetzung

- USB-3.0-Testablauf im Detail