Gigabit-Schnittstellen im Boardtest

Mit dem integrierten FPGA testen

Fortsetzung des Artikels von Teil 1

Integrierte Testverfahren

Auf der Suche nach Alternativen stößt man schnell auf die Hilfsmittel, die die Chiphersteller selbst in ihren Bausteinen zur Verfügung stellen. Heutige Mikroprozessoren oder FPGAs haben für ihre Hochgeschwindigkeits-Schnittstellen oft ausgeklügelte Mechanismen im Silizium integriert, die auch zum Testen einer Baugruppe sehr gut verwendet werden können. Einfachstes Beispiel für eine solche Schnittstelle sind die Gigabit-Transceiver von FPGAs. Oft werden mehrere FPGAs über diese Schnittstellen gekoppelt (zum Beispiel in einem Backplane-System), um einen schnellen und einfachen Datenaustausch zu ermöglichen. Diese Schnittstellen arbeiten heute schon mit Geschwindigkeiten über 20 Gbit/s und sind damit durch herkömmliche Test- und Prüfverfahren kaum noch zufriedenstellend zu testen. Ein einfacher Funktionstest, der verschiedene Prüfpattern sendet und empfängt, reicht zwar für einen prinzipiellen Übertragungstest aus, aber eine qualitative Bewertung der Übertragungsstrecke wird hierbei nicht durchgeführt. Was aber passiert, wenn sich die Bedingungen auf der Baugruppe gegenüber dem Inbetriebnahme- oder Labormuster ändern?

Ein Problem stellen beispielsweise falsch bestückte oder defekte Bauelemente dar. Letztere sind zwar sehr seltene Fehler, können aber auch eine Baugruppe oder einzelne Schaltungsteile unbrauchbar machen. Bei einem Referenztaktgeber oder Quarzoszillator, bei dem ein Typ mit einer anderen Frequenz bestückt wurde, sieht man den Fehler nicht unbedingt im ersten Augenblick beim Schnittstellentest selbst. Er läuft einfach nur mit einer anderen Geschwindigkeit ab.

Jobangebote+ passend zum Thema

FPGA-basierende Testverfahren

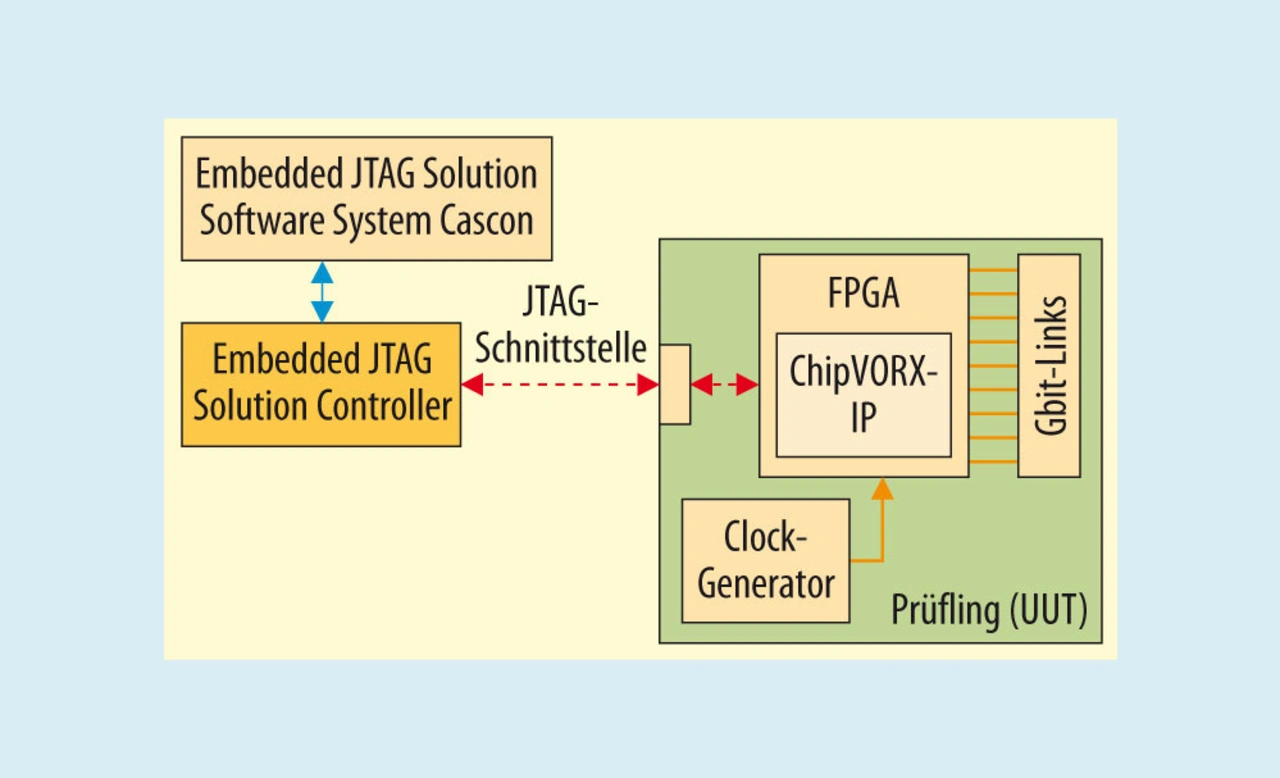

Für solche Testszenarien ermöglicht das System ChipVORX (Bild 1) der Firma Göpel Electronic ein standardisiertes Testverfahren. Durch bereits vorkonfigurierte IPs (Intellectual Property) wird dem Anwender ein Werkzeug in die Hand gegeben, mit dem er in sehr kurzer Zeit einfache Testabläufe erstellen kann, ohne dass er sich mit den FPGA-Werkzeugen selbst auseinandersetzen muss. ChipVORX besteht dabei aus einer großen IP-Bibliothek, die für den jeweils verwendeten FPGA-Baustein die vorgenerierten IPs zur Verfügung stellt. Mit Hilfe eines automatischen Testgenerators in der Embedded-JTAG-Solutions-Software System Cascon kann diese IP dann individuell und einfach für die jeweilige Baugruppe passend konfiguriert werden.

Mit dem daraus erstellten Testprogramm kann nun beispielsweise der für die Hochgeschwindigkeits-Schnittstelle notwendige Referenztakt gemessen werden. Dazu wird über die standardisierte IEEE1149.1-Schnittstelle [3] des FPGAs die IP zunächst in den FPGA geladen und gestartet. Nun erfolgt die Konfiguration der IP mit den im automatischen Testgenerator vorher eingestellten Parametern. Diese Parameter sind bei einer Frequenzmessung sehr einfach, da nur der zu messende Pin bzw. Referenztakteingang vom Anwender vorgegeben werden muss. Für ein automatisiertes Pass/Fail-Testergebnis kann zusätzlich ein erwarteter Frequenzwert mit zulässigen Toleranzwerten angegebenen werden. Damit ist der ChipVORX-Test fertig erstellt und kann sofort verwendet werden.

- Mit dem integrierten FPGA testen

- Integrierte Testverfahren

- Embedded-Bit-Error-Rate-Test mit ChipVORX

- Praktische Umsetzung

- USB-3.0-Testablauf im Detail