JTAG Boundary Scan oder Funktionstest

Die Mischung machts

Fortsetzung des Artikels von Teil 3

Getrennt marschieren, vereint testen

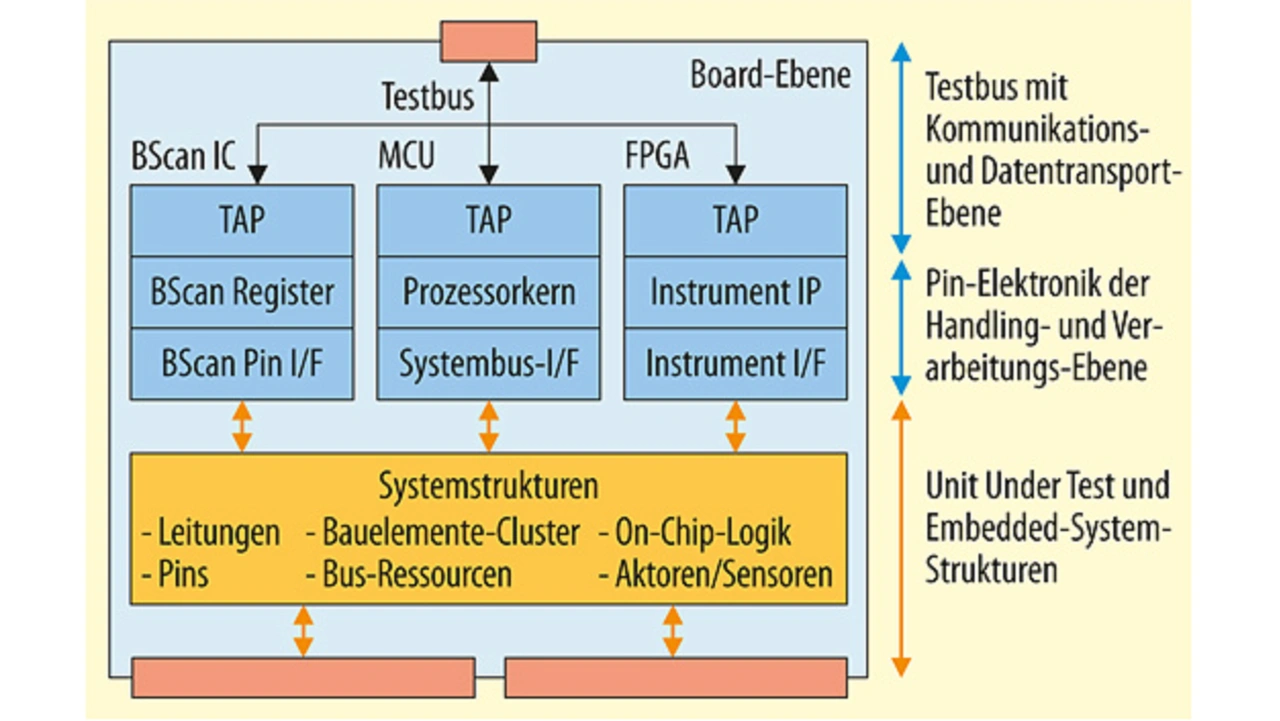

Auch wenn die aufgezeigten funktionalen Testverfahren für sich bereits viele neue Möglichkeiten bieten, wird das volle Potenzial erst durch sinnvolle Kombinationen erschlossen. Für die JTAG-basierten Verfahren ist dabei von Vorteil, dass sie alle die gleiche Infrastruktur benutzen (Bild 9). Auf Basis entsprechend multifunktionaler Systemlösungen wie die von Göpel Electronic entwickelten JTAG-Plattformen Scanflex und System Cascon gelingt der interaktive Mix von Struktur- und Funktionstests problemlos.

Jobangebote+ passend zum Thema

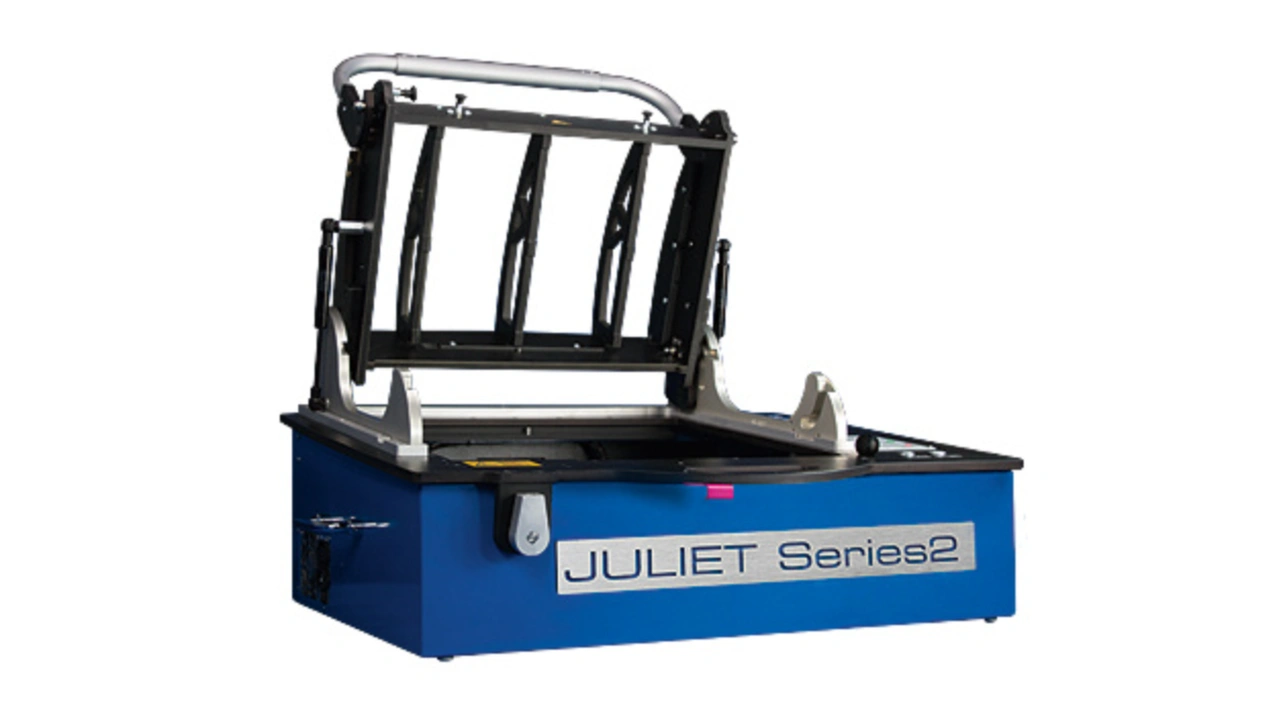

Für den Produktionsbedarf sind auch komplette Desktop-JTAG-Tester wie zum Beispiel das JULIET-System verfügbar (Bild 10). Darüber hinaus gibt es auch sehr leistungsstarke Plattformen zur offenen, modularen Instrumentierung von klassischen Funktionstestern, die sich mit entsprechenden Komponenten sehr gut in Richtung Strukturtest konfigurieren lassen. Eine der führenden Integrationsplattformen ist hierbei PXI bzw. PXI Express.

Der Vorteil solcher Architekturen ist, dass eine sehr hohe Zahl von Multi-Vendor-Modulen für nahezu alle Anwendungs- und Leistungsbereiche zur Verfügung steht. Gestützt auf offene Software-Pakete wie LabView oder TestStand gelingt die Umsetzung flexibler Systemkonzepte. Die Integration der JTAG-Komponenten erfolgt auf Basis von entsprechenden Hardware-/Software-Plug-ins. Dabei existieren auch Software-Lösungen, die dem Funktionstester die volle Kontrolle der JTAG-Hardware ermöglichen und ein interaktives Vektor-Interface bieten. Über diesen transparenten Slave-Modus sind beispielsweise auch Clustertests realisierbar. Zur Integration der Embedded-System-Access-Technologien steht eine ganze Reihe von JTAG-Boundary-Scan-Controllern bereit, alle im PXI/PXIe Format und ausgeführt als Single-Slot-Instrument.

Das gleiche Prinzip des Plug-in von JTAG-Boundary-Scan-Komponenten wird im Übrigen auch zur Kombination mit invasiven Testern wie ICT, FPT und MDA verwendet. Auch hier sind interaktive Prozeduren zur Erhöhung der Fehlerabdeckung möglich und sinnvoll.

Für den Mix der verschiedenen Strategien stehen ausgereifte und leistungsstarke Plattformen zur Verfügung. Das gilt auch für die Kombination mit klassischen, externen Testinstrumenten. Den Anwendern eröffnet sich damit ein großes Arsenal an technischen Lösungswegen. Die richtige Entscheidung muss aber individuell auf Basis einer genauen Analyse der Produkteigenschaften, der Prozessparameter und nicht zuletzt der Kostensituation getroffen werden.

Literatur:

[1] IEEE Std.1149.1-1990, Standard Test Access Port and Boundary Scan Architecture

[2] IEEE Std. 1149.6-2003, Standard for Boundary Scan Testing of Advanced Digital Networks

[3] IEEE Std.1149.1-2013, Standard Test Access Port and Boundary Scan Architecture

[4] Thomas Wenzel, Andreas Türk: Die Crux der BGA-Lötstellen. White Paper, Göpel Electronic, 2014

[5] Thomas Wenzel, Martin Borowski: Einsamer Boundary Scan IC sucht Anschluss. White Paper, Göpel Electronic, 2014

[6] Thomas Wenzel, J.Heiber: Große Teststrategien klein verpackt. White Paper, Göpel Electronic, 2015

[7] IEEE Std. P1687, Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device.

Die Autoren:

| Thomas Wenzel |

|---|

| ist bei Göpel Electronic als Geschäftsführer für den Produktbereich Boundary Scan verantwortlich. |

| Enrico Zimmermann |

|---|

| ist Vertriebsleiter für JTAG/Boundary Scan und Inspektionslösungen bei Göpel Electronic. |

- Die Mischung machts

- Standardisierte Vielfältigkeit

- Den Anwender entlasten

- Getrennt marschieren, vereint testen