JTAG Boundary Scan oder Funktionstest

Die Mischung machts

Fortsetzung des Artikels von Teil 1

Standardisierte Vielfältigkeit

Obwohl JTAG Boundary Scan mittlerweile schon über 25 Jahre als IEEE-1149.1-Standard existiert [1], haben ihn die zyklisch vorgenommenen Erweiterungen wie z.B. IEEE 1149.6 [2] und neue Releases [3] beständig auf Höhe der technologischen Anforderungen und damit jung gehalten. Im Zusammenhang mit dem hier diskutierten Thema sollen einige Eigenschaften jedoch besonders herausgehoben werden:

- Der Standard wurde als Nachfolger des digitalen, statischen In-Circuit Test konzipiert; darüber hinausgehende Bereiche kann er nur schwer oder gar nicht abdecken.

- JTAG Boundary Scan definiert lediglich digitale Testpunkte innerhalb von Chips; diese sind sowohl für den Strukturtest als auch für statischen Funktionstest nutzbar.

- Da der innere Schaltkreiskern bei aktivem Testmodus quasi isoliert wird, gelingt in genialer Weise die grundsätzliche Trennung von Funktion und Struktur.

- Die hohe Automatisierbarkeit der Testvektorgenerierung sichert gleichzeitig auch die hohe Diagnosequalität. Hier zeigt das Verfahren eine fast unschlagbare Effektivität.

- Die Fehlerabdeckung ist im Voraus kalkulierbar, das heißt Designs können noch in der Testbarkeit optimiert werden, bevor ein Prototyp gebaut wird.

- Die Fehlerabdeckung wird im digitalen Bereich primär durch die begrenzte Vektorfolgefrequenz limitiert, kann also keine dynamischen Fehler erkennen.

Boundary Scan hat sich sinnvollerweise vor allem in den komplexen Chips wie Prozessoren, FPGA, DSP und ASIC etabliert. Bereits ein Boundary-Scan-Schaltkreis kann hervorragende Dienste beim Testen erzielen [4] und ist im Verbund mit Inspektionstechnologien auch eine sinnvolle Ergänzung als Prozesssensor [5].

Jobangebote+ passend zum Thema

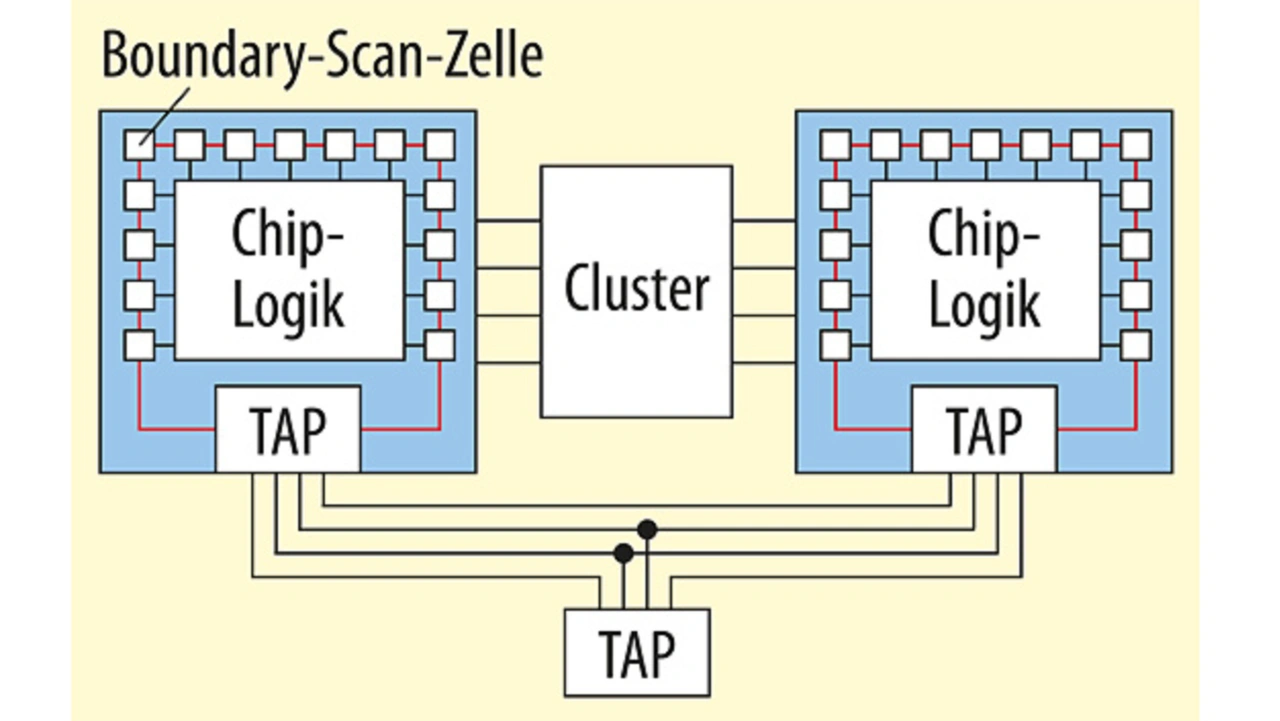

Eine Möglichkeit der Nutzung von Boundary Scan zum Funktionstest ist durch den Clustertest gegeben (Bild 2). Es gibt sehr vielfältige Spielarten, wie ein Clustertest aussehen kann. Zur weiterführenden Erklärung sei an dieser Stelle auf die Literatur verwiesen [4].

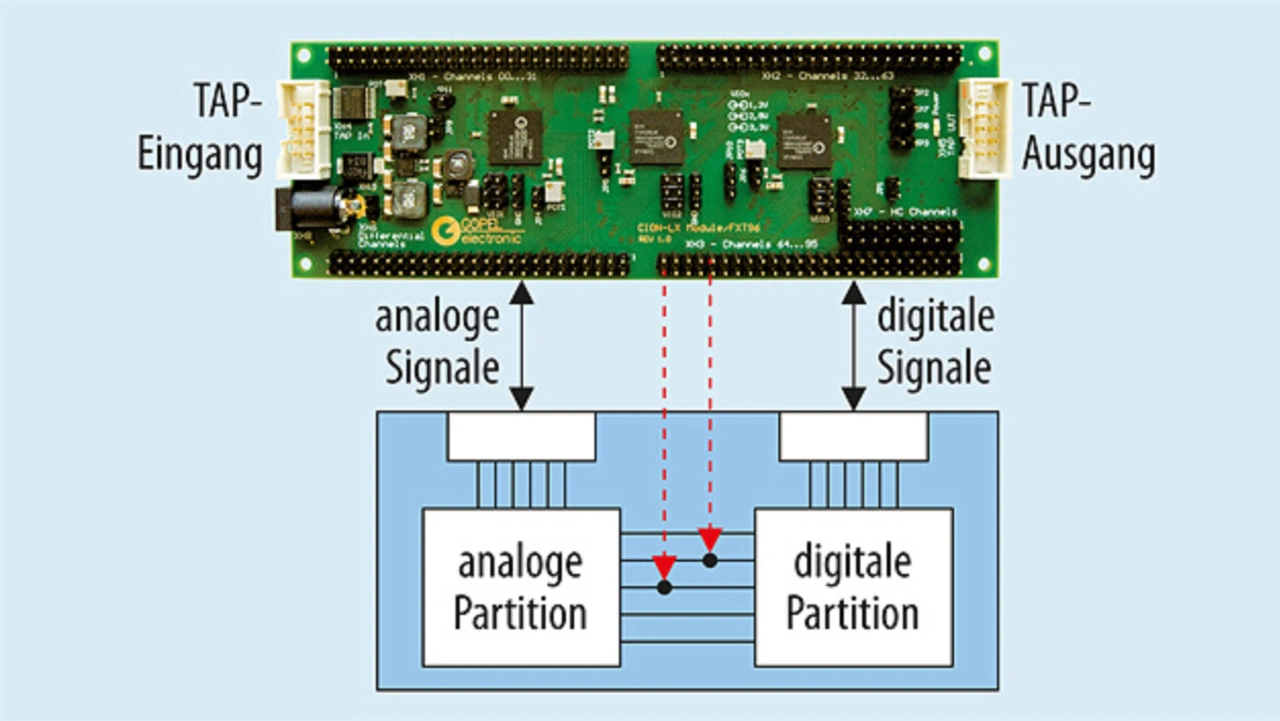

Neben solchen eingebetteten Applikationen können auch externe I/O-Module zum Einsatz kommen (Bild 3). Sie sind in der Lage, eine Gesamtschaltung einfach über die nativen Steckverbinder statisch funktional anzusteuern oder auch über Testpunkte auf der UUT. Sind weitere Boundary-Scan-Schaltkreise auf dem Board, können oftmals auch tiefe strukturelle Tests von Steckverbindern oder anderen nicht scanfähigen Partitionen ausgeführt werden. Das Boundary-Scan-Prinzip bleibt damit immer gleich, da die externen Module quasi zur natürlichen Schaltung hinzugefügt werden.

Über ein derartiges Szenario lassen sich selbst analoge Funktionen oder Cluster testen. Voraussetzung ist allerdings, dass die I/O-Module auch über Mixed-Signal-Kanäle verfügen, wie es zum Beispiel beim CION-LX I/O Module von Göpel Electronic [6] (Bild 3) der Fall ist.

Zusammenfassend bietet Boundary Scan also von Haus aus schon einige Funktionstestmöglichkeiten, allerdings sind diese auf das statische Niveau begrenzt.

Die Funktionstestwelt auf den Kopf stellen

Wenn der Begriff Funktionstest in der Produktion fällt, geht die erste Assoziation fast immer in Richtung der klassischen Variante – ein externer Tester ist mit der UUT über die nativen Steckverbinder kontaktiert, fährt seine Sequenzen ab und wertet die Responses aus. Doch es gibt noch weitere interessante Methoden (Tabelle 2), die insbesondere auf den Embedded Test fokussiert sind und viele innovative Eigenschaften aufweisen.

| Verfahren | Grundlegendes Wirkprinzip | Typische Eigenschaften |

|---|---|---|

| Prozessor-Emulationstest |

|

|

| Chip Embedded Instruments |

|

|

| Embedded Operating System |

|

|

Tabelle 2. Funktionale Verfahren zum eingebetteten Testzugriff

- Die Mischung machts

- Standardisierte Vielfältigkeit

- Den Anwender entlasten

- Getrennt marschieren, vereint testen