JTAG Boundary Scan oder Funktionstest

Die Mischung machts

Fortsetzung des Artikels von Teil 2

Den Anwender entlasten

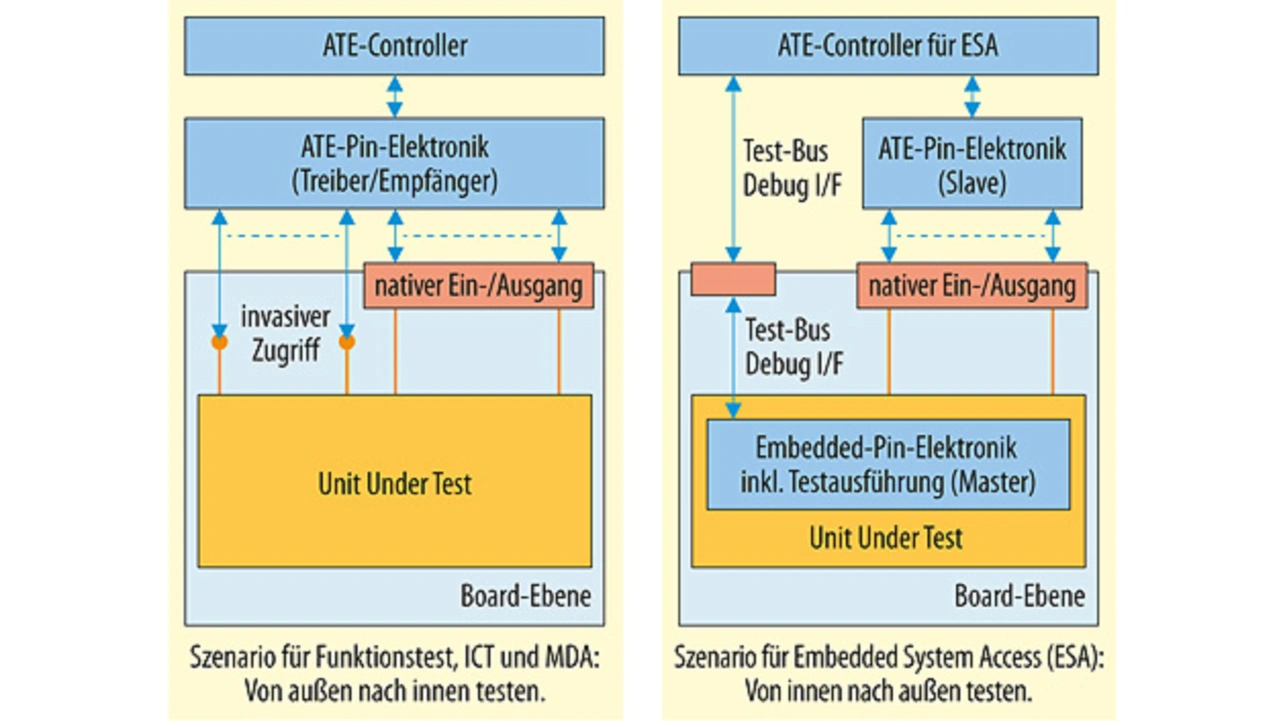

Alle diese Verfahren verfolgen primär ein Ziel: den Anwender von der Codierung eigener Testroutinen durch vorkonfektionierte Lösungen zu entlasten und damit eine wesentlich höhere Effektivität und Kalkulierbarkeit des gesamten Testprozesses zu gewährleisten. Dabei werden die eigentlichen Test-Instrumente ins Innere der UUT verlagert und man spricht vom Embedded System Access. Das hat weitreichende Folgen (Bild 4).

Die augenscheinlichste Veränderung ist, dass sich die mit Boundary Scan begonnene Transformation von Tester-Anteilen weiter verstärkt und nun auch die Testausführungseinheit umfasst. Das heißt, es wird noch mehr auf die durch das Design definierten Elemente zurückgegriffen. Das senkt gleichzeitig auch den externen Aufwand.

Jobangebote+ passend zum Thema

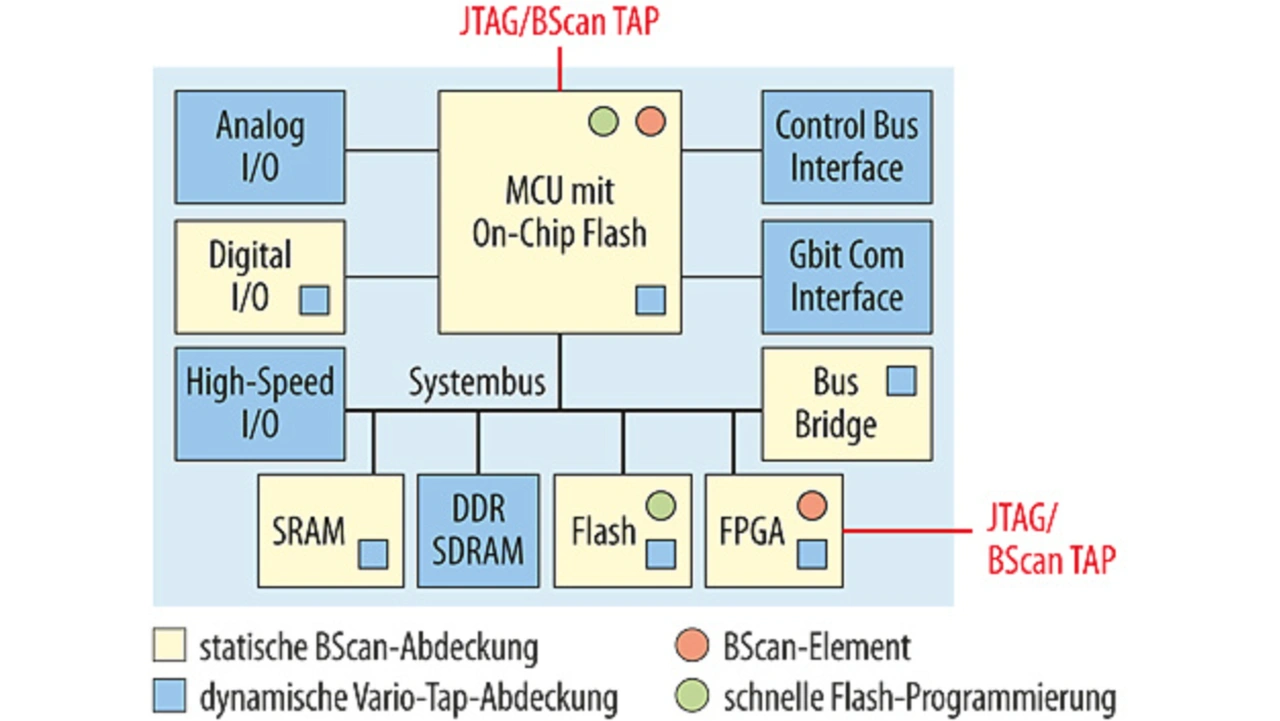

Dabei nutzt der Emulationstest den nativen On-Board-Prozessor als Testausführungseinheit und kann dadurch alle an den Core angeschlossenen Elemente erreichen. Typischerweise erfolgt durch den Systembus auch eine natürliche Partitionierung der Gesamtschaltung, wodurch sich die Generierungsprozesse auf Basis von Modellen automatisieren lassen (Bild 5).

Gleichzeitig ermöglicht das Prinzip auch eine schnelle Programmierung von Flash-Bausteinen. Dieses sogenannte Core Assisted Programming bietet in vielen Fällen eine wesentlich höhere Leistungsfähigkeit als Boundary Scan.

Grundsätzlich wird beim Emulationstest der Prozessor von außen mit Vektoren versorgt, legt diese in einem natürlichen Buszyklus an, liest Daten zurück und gibt diese wieder an die übergeordnete Steuereinheit zur Auswertung. Daher gelingt auch nur ein At-Speed-Test. Neueste Entwicklungen ermöglichen jedoch auch eine Echtzeit-Abarbeitung von Emulations-Scripts. Als Beispiel sei die von Göpel Electronic entwickelte VarioTAP-Technologie mit RT-Erweiterung genannt.

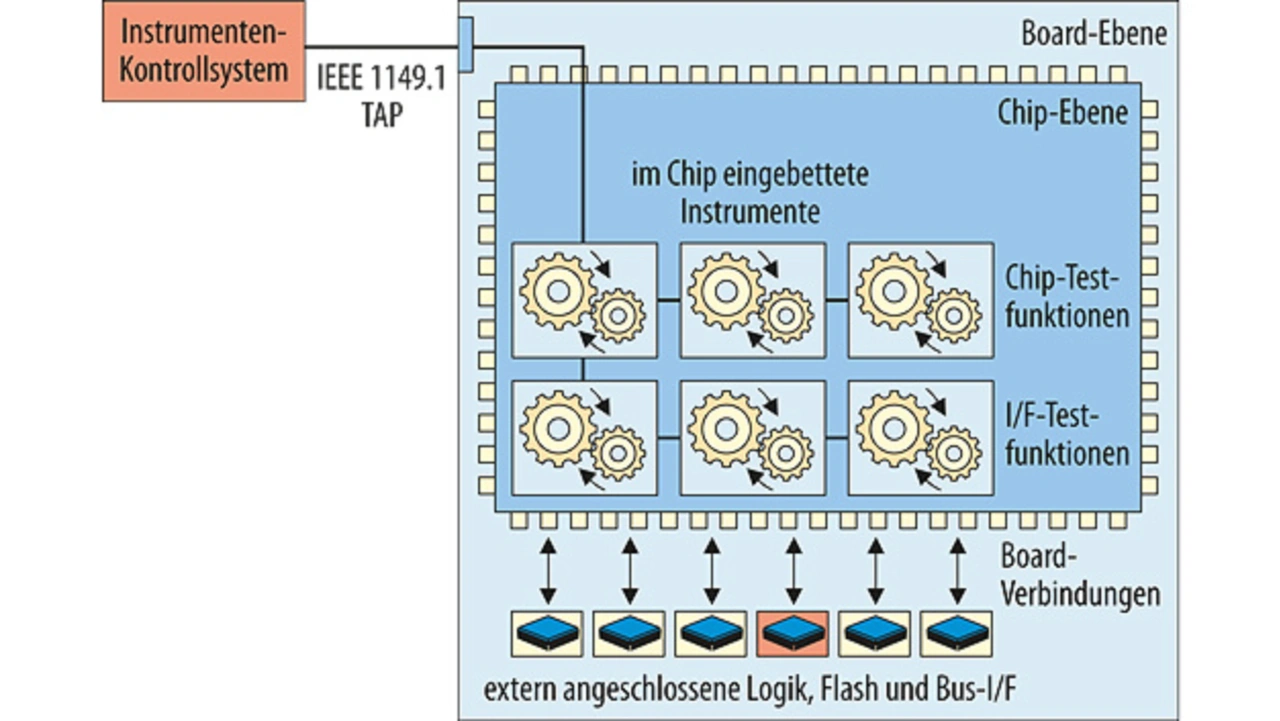

Chip Embedded Instruments finden bereits seit vielen Jahren erfolgreich auf dem Gebiet des Schaltkreis-Tests Verwendung. Dabei werden spezielle IP in das Design fest integriert. Diese Infrastruktur wird durch neueste Standards wie IEEE 1687 [7] und IEEE 1149.1-2013 [3] nun auch für den funktionalen Board-Test erschlossen. Das Prinzip ist eigentlich recht einfach zu durchschauen und basiert auch auf dem Einsatz von JTAG als Transfermedium (Bild 6).

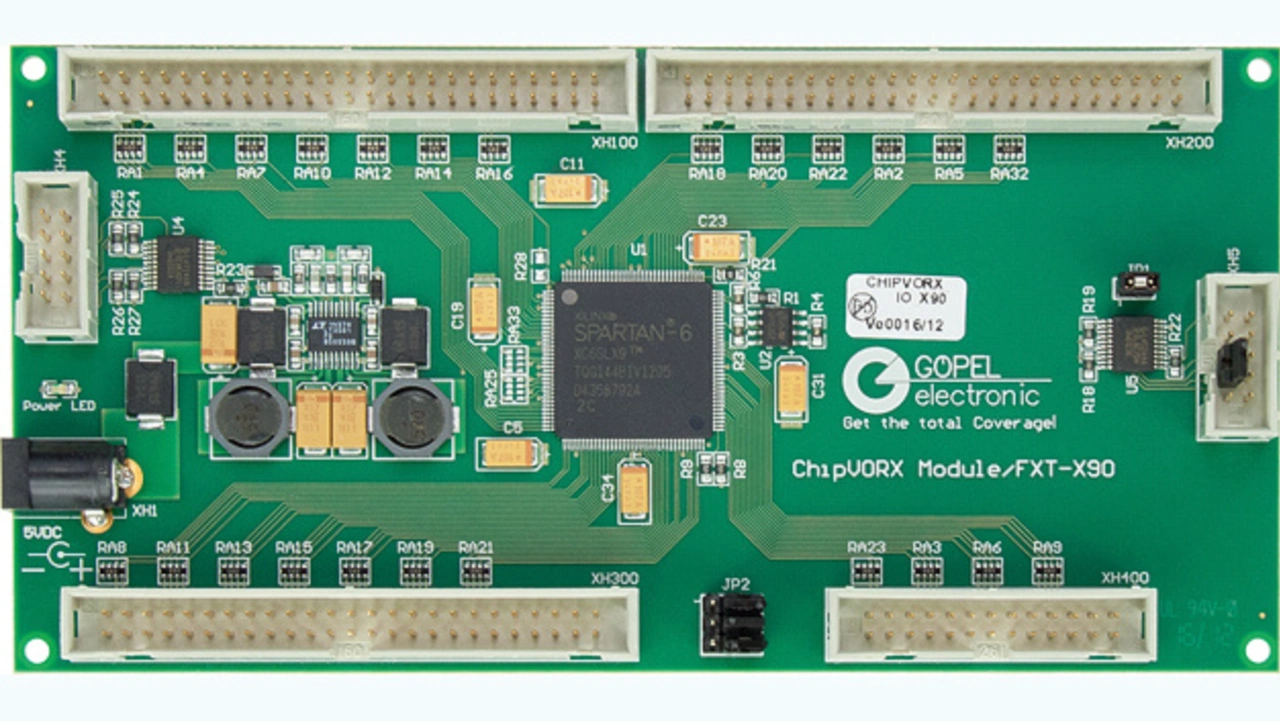

Der Vielfältigkeit solcher Instrumente sind in der Praxis de facto keine Grenzen gesetzt. Besonders interessant ist hierbei die Nutzung von FPGA-basierten Instrumenten. Sie werden als Soft-IP temporär in das Target geladen und können individuell an die Testaufgabe angepasst werden. Beispiele für solche Instrumente sind Frequenzmesser, Speichertester, Bit Error Rate Tester, LAN-Tester, Flash Programmer und Logik-Analyzer, um nur einige zu nennen. Allerdings existiert bei FPGAs immer das Problem, die IP individuell an die jeweiligen Pins der zu testenden Schaltung anzupassen. Neueste Entwicklungen wie die von Göpel Electronic entwickelte ChipVORX-Technologie automatisieren jedoch auch diese IP-zu-Pin-Kontaktierung ohne erneute Design-Compilierung.

Interessant ist in diesem Zusammenhang auch der Einsatz von externen I/O-Modulen mit FPGA (Bild 7). Sie erweitern auf direktem Weg den Einsatz von FPGA-Embedded Instruments zum funktionalen Board-Test über Zugriff auf die natürlichen Steckverbinder.

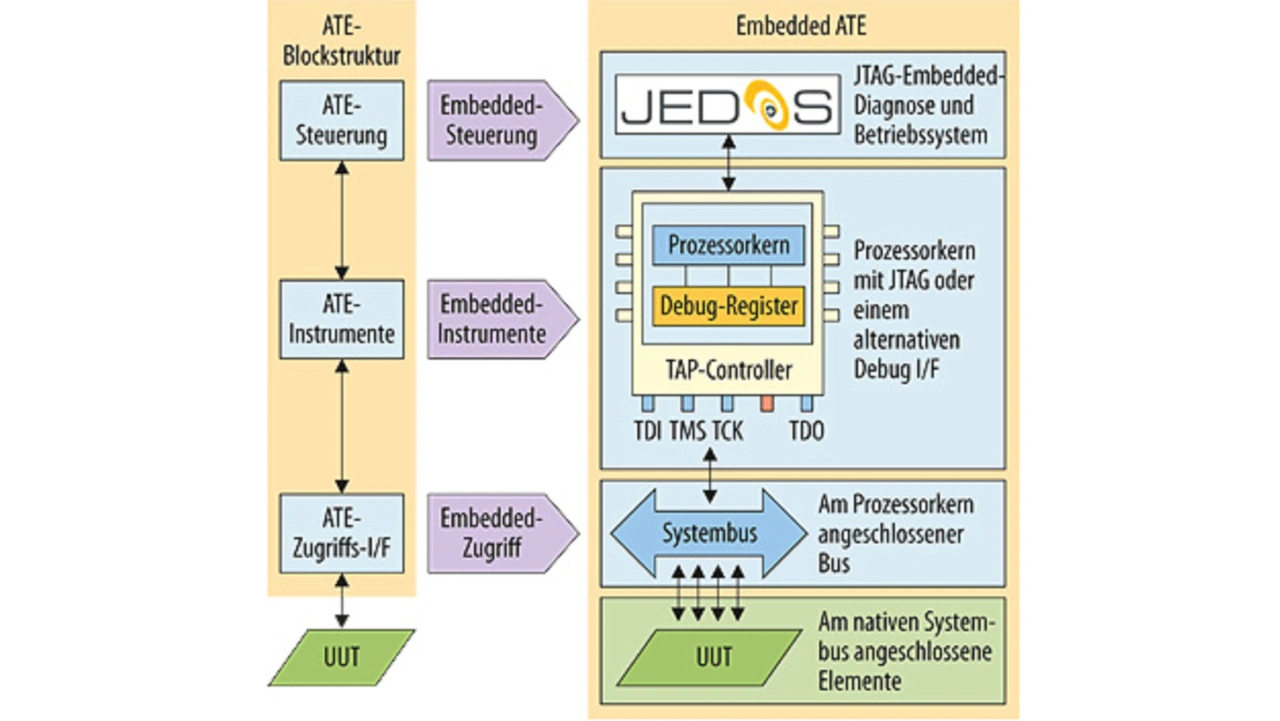

Das dritte bereits in Tabelle 2 ausgewiesene Verfahren ist das eingebettete Betriebssystem zum Test und zur Diagnose. Auch hier wird der Prozessor als Testausführungseinheit genutzt, allerdings unter Kontrolle einer kompletten Test- und Diagnose-Software, wie beispielsweise Jedos (Bild 8).

Die Software beinhaltet auch bereits vorkonfektionierte Test-Vektoren und Diagnose-Algorithmen, die prinzipiell in Echtzeit ausgeführt werden. Der Vektor-Download entfällt komplett. Damit wird der Schritt zu einer vollständig integrierten ATE zum Funktionstest vollzogen.

- Die Mischung machts

- Standardisierte Vielfältigkeit

- Den Anwender entlasten

- Getrennt marschieren, vereint testen