EMV von MEMS-Sensoren optimieren

Simulation in fünf Schritten

Fortsetzung des Artikels von Teil 1

Fallbeispiel MEMS-Beschleunigungssensor

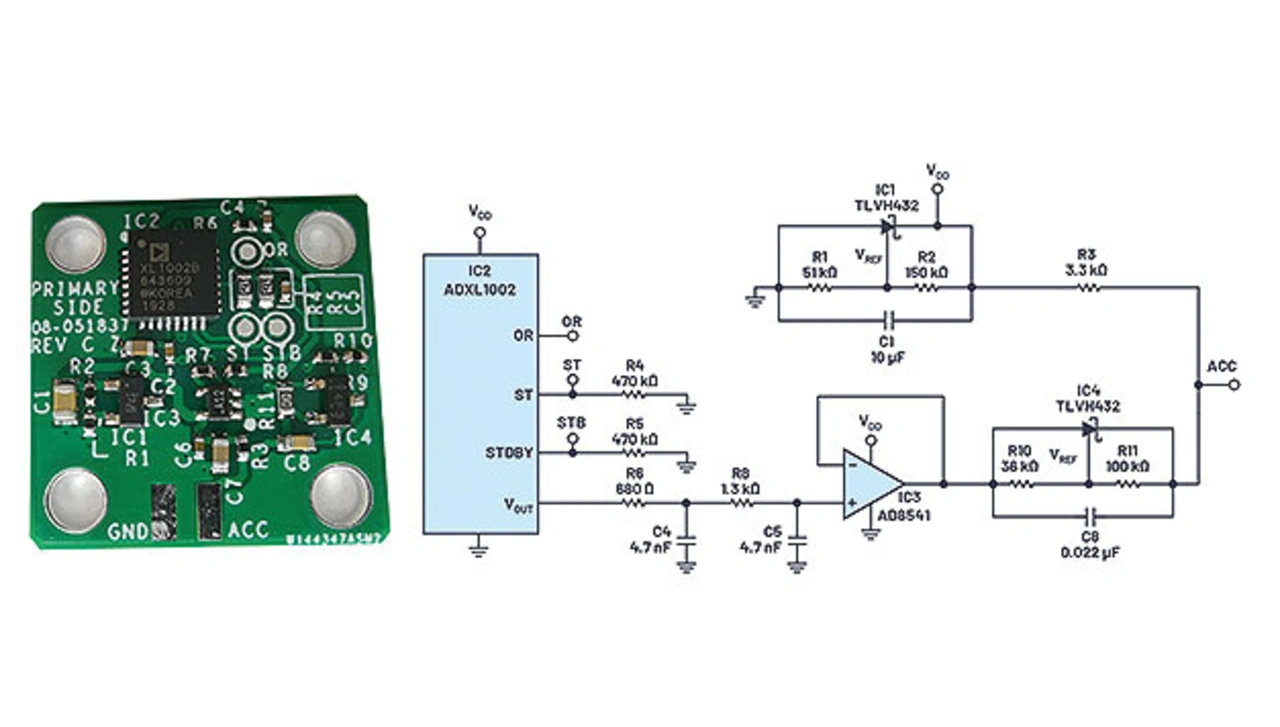

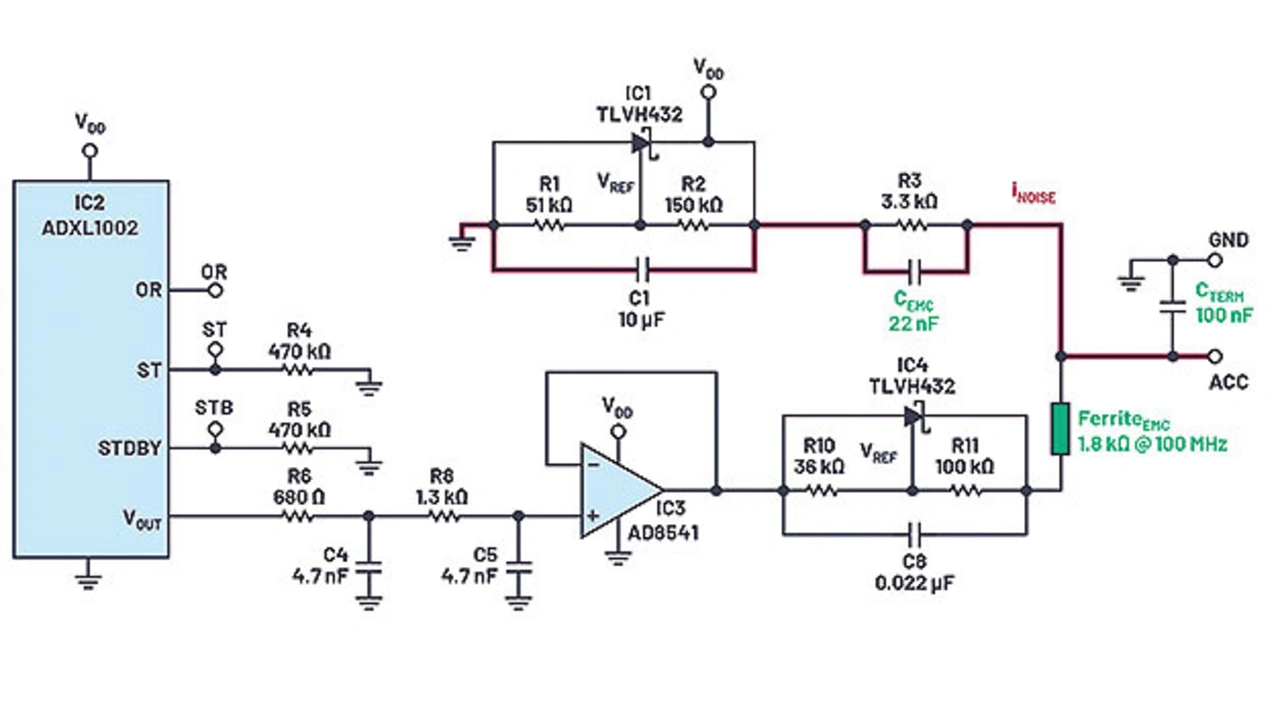

Als Simulationsbeispiel wird eine Schaltung zur Vibrationsüberwachung betrachtet (Bild 4). Sie enthält den MEMS-Beschleunigungssensor ADXL 1002 von Analog Devices und kann über eine IEPE-Schnittstelle betrieben werden.

Jobangebote+ passend zum Thema

Die Schaltung enthält zwei Shunt-Regler, wovon einer (IC1) den Beschleunigungs-sensor und den Operationsverstärker AD8541 (IC3) versorgt, sowie eine zweite Schaltung (IC4), die einen Bias von 9,5 VDC liefert. Wenn das System eingeschaltet ist und der ADXL 1002 nicht aktiv ist, dann stellt sich der Kommunikationsbus auf 12 VDC ein. Nachgewiesen werden muss eine leitungsgebundene HF-Immunität gemäß IEC 61000-4-6 – eine Standardanforderung für industrielle Anwendungen.

Um die Güte der Simulation hoch zu halten, muss sie mit den Messergebnissen aus einem realen Labor korreliert werden. Das erfordert im Wesentlichen fünf Schritte:

(1) Korrelation des realen Labortestaufbaus mit der Simulationsumgebung, (2) Entwickeln von Simulationsmodellen mit dem virtuellen Labor, (3) Aufdecken von EMV-Schwächen des Designs mit der Simulation, (4) Designver- besserungen simulieren und (5) die EMV-Verbesserungen in der realen Laborumgebung verifizieren.

Schritt 1: Testaufbau mit Simulation abgleichen

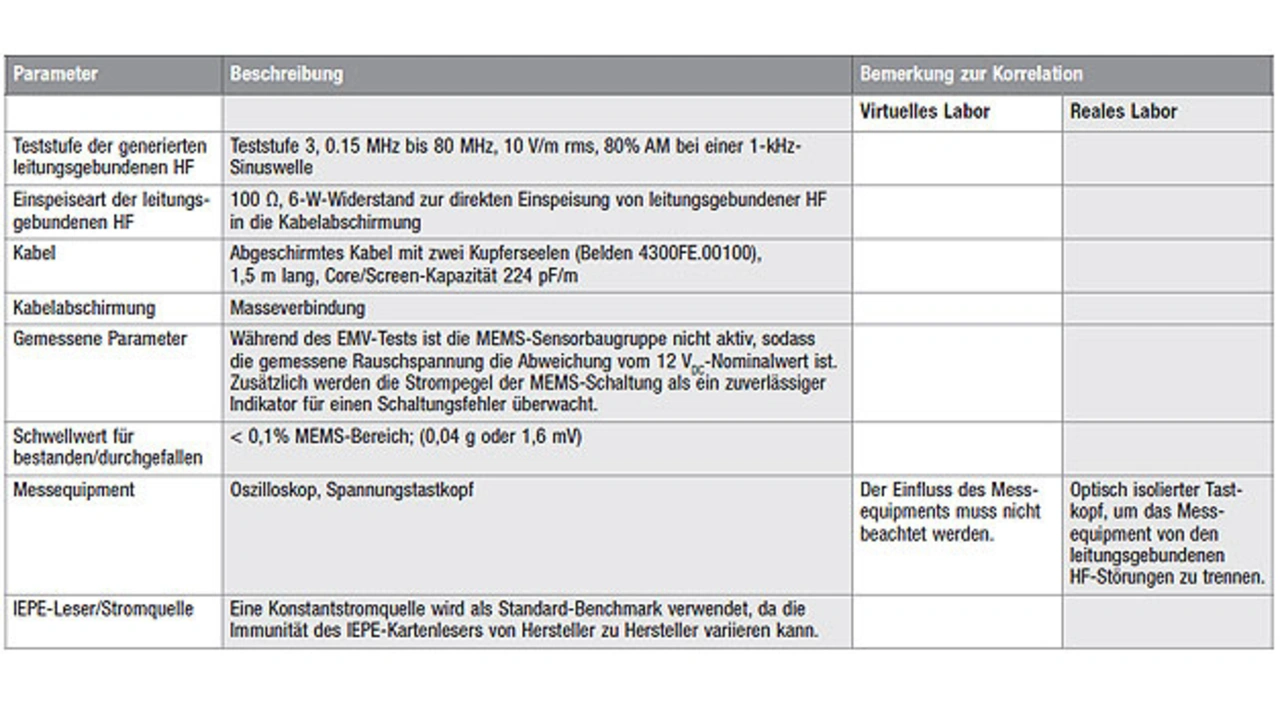

Zunächst werden die relevanten Anforderungen aus den Teststandards und die Eigenschaften des Prüflings ermittelt und aufgelistet (Tabelle 2). In diesem Beispiel wird IEC 61000-4-6 betrachtet, die Prüfvorschrift für den Test auf Störfestigkeit gegen leitungsgebundene HF-Störungen.

Er zielt auf Geräte ab, die in Umgebungen mit HF-Belastungen eingesetzt werden und dort störungsfrei funktionieren müssen. Die HF-Störfelder können dabei über die gesamte Kabellänge einwirken, weshalb der Test gerade für leitungsgebundene Sensoren eine wichtige Rolle spielt. Zeile 1 der Tabelle zeigt die Gemäß IEC 61000-4-6 geforderten Feldstärken und Frequenzen: Das HF-Feld wird schrittweise von 150 kHz bis 80 MHz angelegt, ist bei einer 1-kHz-Sinuswelle 80 % Amplitudenmoduliert (AM) und beträgt bei Testlevel 3 maximal 10 V/m. Zeilen zwei und drei zeigen die definierte Einspeisemethode und die Kabelspezifikationen des Prüflings. Die weiteren Zeilen enthalten Angaben zu Systemmasse einschließlich Kabelabschirmung, ermittelte Messparameter sowie Schwellwerte für Amplitude und Frequenz zur Beurteilung bestanden/durchgefallen.

Schritt 2: Simulationsmodelle entwickeln

Typische SPICE-Modelle sind heute für die meisten aktiven und passiven Komponenten allgemein verfügbar. Simulatoren für elektromagnetische Bauteile können weitere nicht standardisierte Komponenten wie Leiterplattenmaße und Netze auf der Leiterplatte aber auch Kabel modellieren.

Die in Tabelle 2 zusammengefassten Informationen helfen bei der akkuraten Modellierung von Kabelparametern. Dieses System nutzt ein geschirmtes Kabel mit zwei Leitungen, das zwar deutlich teurer als ein ungeschirmtes Kabel ist, aber auch einen besseren EMV-Schutz bietet. Die MEMS-IEPE-Schaltung aus Bild 4 wurde mit 19 mm × 19 mm sehr kompakt entwickelt und hat nur zwei Leiterplattenlagen. Aufgrund der größeren Kopplungskapazitäten und der Neigung zum Übersprechen muss hier sehr sorgfältig entwickelt werden, um EMV-Probleme zu vermeiden.

An dieser Stelle kann der Systemingenieur damit beginnen, die Modelle für die Leiterplatten und Kabel zu generieren und sie mit den SPICE-Modellen für die ICs und passiven Komponenten zu verbinden. Damit kann nun eine SPICE-Simulation durchgeführt werden und ein EMV-Stimulus auf Systemebene damit interagieren.

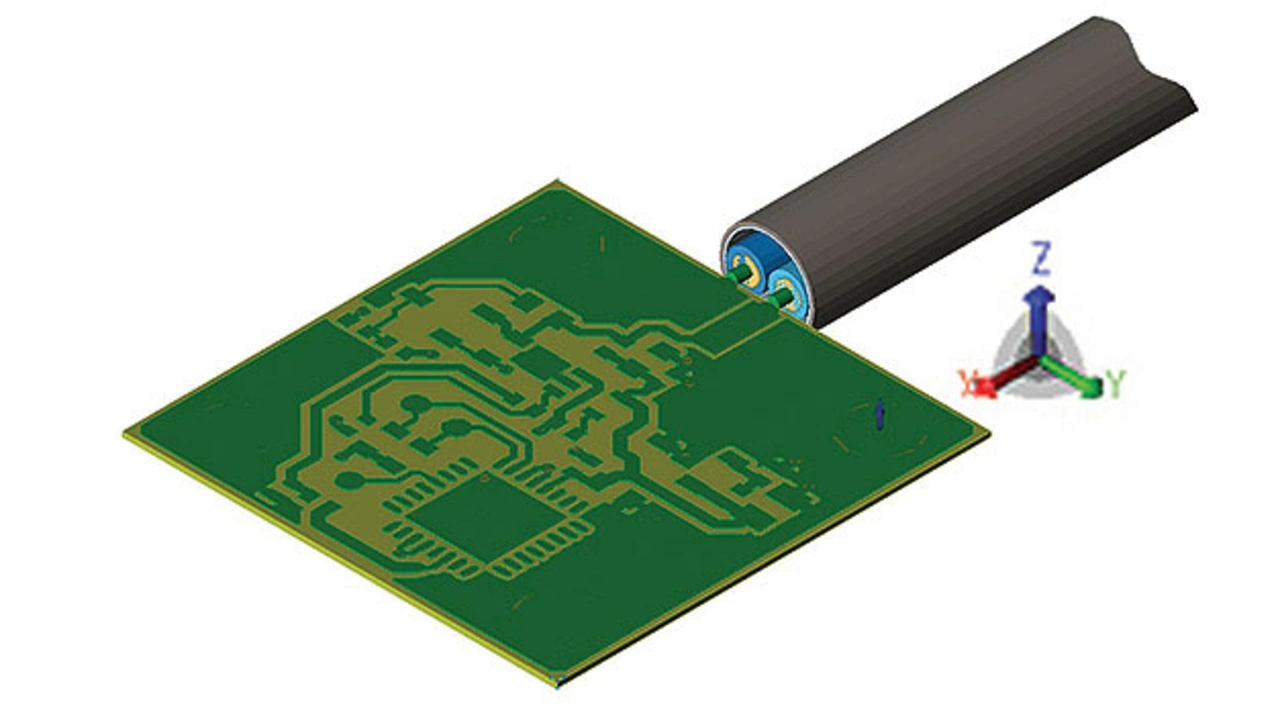

Bild 5 zeigt ein EMV-Simulationsmodell für die Leiterplattenmaße mit Netzen und abgeschirmtem Kabel. Es ist eine vollständige Abstrahierung der physikalischen Leiterplatte und kann über die elektrischen Anschlüsse mit Simulationsmodellen des MEMS, des Operationsverstärkers und des Shunt-Reglers verbunden werden. Die Parameter der passiven Komponenten (Kondensatoren, Widerstände, Spulen) lassen sich am Modell schnell verändern und die jeweiligen Systemresonanzen beobachten und anpassen. Der Aufwand dafür ist deutlich geringer als bei der Prüfung und Änderung von realer Hardware. Das Kabel-SPICE-Modell kann auch während der Prüfung noch geändert werden – z. B. kann das Kabel verlängert oder verkürzt werden, was erhebliche Auswirkungen auf die EMV-Kopplung und Systemleistung haben kann.

Nach der EMV-Simulation im Zeitbereich folgt eine Analyse des Einschwingverhaltens über Zeit und Frequenz. Abhängig von der Art des EMV-Tests muss eine Transienten- oder Frequenzanalyse gemacht werden.

Schritt 3: EMV-Schwächen im Design identifizieren

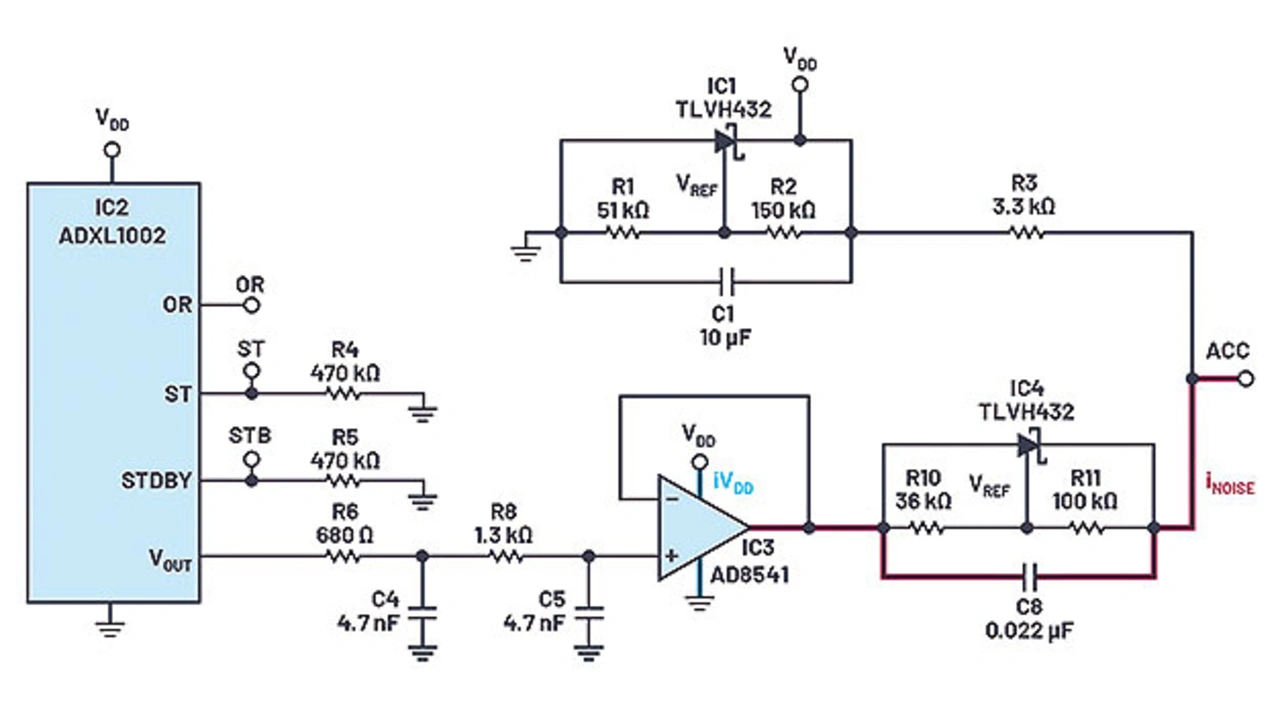

Sind die Simulationsmodelle erstellt, lassen sich die Fehlermechanismen relativ schnell herausfinden. Die EMV-Rauschspannung wird in die Kabelabschirmung eingespeist. Diese wird dann über die parasitäre Kapazität zwischen der Kabelabschirmung und den beiden Fasern eingekoppelt.

Das Rauschen ist gegen den ACC-Knoten auf der Leiterplatte gerichtet. Der Pfad ist in Bild 6 rot eingezeichnet. Das Rauschen folgt dem Pfad mit der geringsten Impedanz, hier durch Kondensator C8 zum Ausgang des OPVs. Als Resultat davon geht der OPV in Sättigung und zieht einen hohen Strom aus dem Versorgungsknoten (VDD). Der VDD-Regler kann diesen hohen Strom aber nicht liefern, deshalb fällt die VDD-Spannung ab. Der VDD-Spannungsabfall schaltet den MEMS-Sensor temporär ab (normal mit 5 V versorgt), was zu einer Welligkeit des OPV-Ausgangs führt (rauschen). Ein zweiter entdeckter Fehlermechanismus wäre allein mit Labortests schwer bis gar nicht aufzudecken gewesen. Übertragungsleitungen für Hochfrequenzen sind üblicherweise mit einer Last abgeschlossen, die mit der Impedanz der Übertragungsleitung übereinstimmt. Das IEPE-Kabel ist wegen der niederfrequenten Datenkommunikation im kHz-Bereich jedoch üblicherweise offen. Wenn das EMV-Rauschen dann im 60- bis 70-MHz-Frequenzbereich eingespeist wird, werden die Rauschspannungen auf dem Kommunikationsbus reflektiert, da das Kabel nicht mit einer passenden Last abgeschlossen ist.

Schritt 4: EMV-Verbesserung simulieren

Das Ziel in Schritt 4 ist es, die kostengünstigste und effektivste Abänderung der Schaltung zu finden. Die beiden erwähnten EMV-Probleme können gelöst werden, indem die beiden Kondensatoren CEMC undCTERM (Bild 7) integriert werden.

Der 22-nF-CEMC führt das Rauschen weg von den beiden empfindlichen Schaltungen Operationsverstärker und MEMS, wobei der Rauschstrom nun über den Kondensator C1 auf Masse abgeleitet wird. Um weiteres Restrauschen zu unterdrücken, kann eine Ferritperle mit hoher Impedanz bei 100 MHz hinzugefügt werden. Der Kondensator CTERM verschiebt während der EMV-Prüfungen Kabelreflexionen bei hohen Frequenzen.

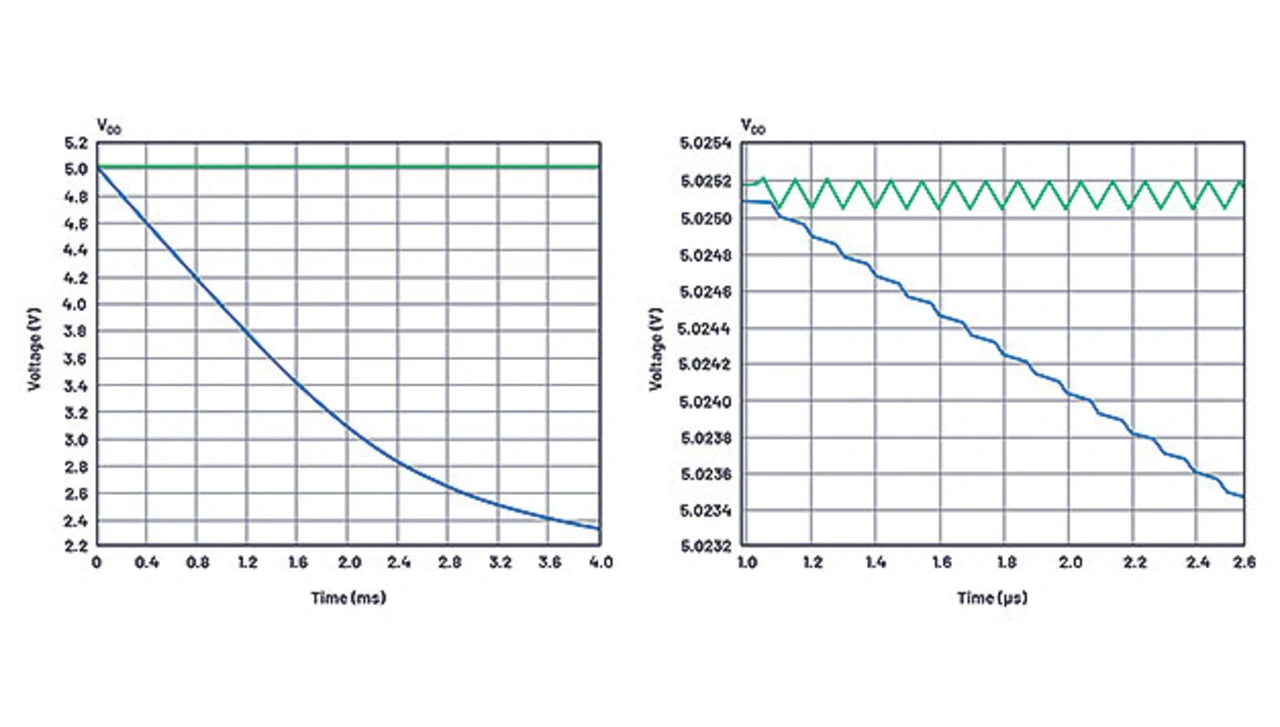

Der Fehler in der VDD-Stromversorgung ist ein sicherer Indikator für Anfälligkeit gegen EMV-Störungen. Die blaue Kurve in Bild 8 zeigt den Spannungsabfall von VDD, wenn CEMC nicht verwendet wird.

Die Simulation ergibt einen Spannungsabfall von rund 2 V oder größer. Wird CEMC eingesetzt, liegt die Abweichung vom Nominalwert im Bereich von einigen Mikrovolt und damit deutlich unter dem Schwellwert für die geforderte Kompatibilität von 1,6 mV.

Der MEMS-Sensor ADXL 1002 hat eine 3-dB-Bandbreite von 11 kHz, sodass die richtige Auswahl der Kondensatoren CEMC und CTERM wichtig ist, um den 11-kHz-Kommunikationsbus beizubehalten. Mit dem virtuellen Labor lassen sich schnell viele verschiedene Kapazitätswerte simulieren und zwei Kondensatoren auswählen, die den optimalen Werten am nächsten kommen. Die Simulation der beiden Kondensatoren ergab, dass das System mit einer Rauschspannung von 1,6 mV oder drunter die EMV-Kriterien erfüllt.

Schritt 5: Design im Testlabor validieren

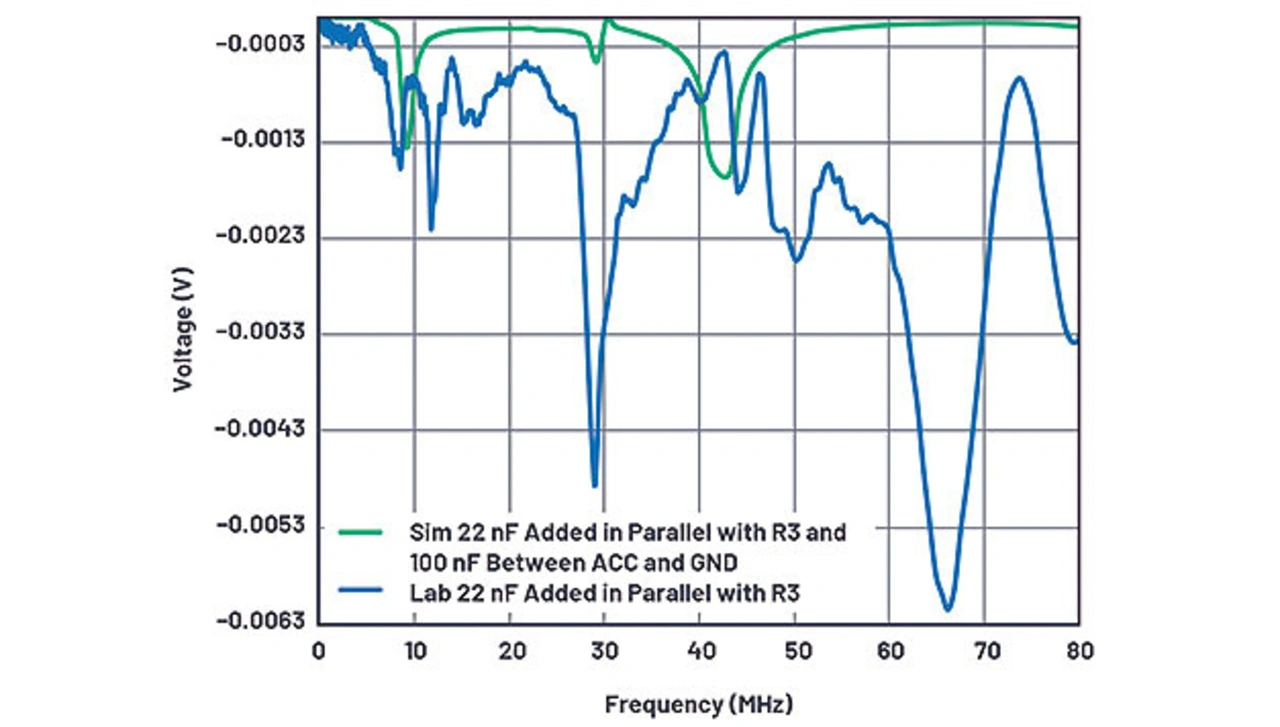

Die Originalschaltung wurde mit den Parametern aus Tabelle 2 getestet. Das Ergebnis war ein sehr hohes Rauschen von 912 mV bei 77 MHz. Nach Integration des 22-nF-Kondensators (CEMC) parallel zum Widerstand R3 fiel das gemessene Rauschen auf unter 6 mV (blaue Messkurve in Bild 9).

Um das Entwicklungsziel von weniger als 1,6 mV zu erreichen, wurden ein 100-nF-CTERM und auch der CEMC zwischen die ACC- und GND-Knoten eingefügt. Bild 9 zeigt in Grün die Simulationsergebnisse mit einer abgeflachten Rauschkurve über das Frequenzspektrum von 0,15 MHz bis 80 MHz.

Aus der Simulation lässt sich auch bestimmen, welcher Teil des Systems das schwächste Glied aus Sicht der EMV ist. Hier ist es das Kabel, weil es die EMV-Leistung von der Quelle in die Schaltung einkoppelt und wegen seiner Länge und Abschlussimpedanz bei höheren Frequenzen Reflexionen hervorruft. Die beiden Kondensatoren CTERM und CEMC konnten die beiden Rauschquellen des Kabels effektiv auf Masse ableiten. Alternativen wie ein Austausch des OPVs gegen ein Modell mit geringer Ausgangsimpedanz sind unrealistisch, da Bausteine mit kleinerer Ausgangsimpedanz auch eine höhere Verlustleistung haben und davon wäre die Wettbewerbsfähigkeit des Gesamtsystems beeinträchtigt.

Die Autoren

Richard Anslow

ist Systementwickler für zustandsbasierte Überwachungs- und industrielle Kommunikationssysteme. Er arbeitet in der Arbeitsgruppe Conncted Motion & Robotics des Geschäftsbereichs Automation and Energy von Analog Devices. Er studierte an der Universität in Limerick, Irland, und schloss dort als B. Eng. und M. Eng. ab.

Ricardo Zaplana

arbeitet als Design-Engineer bei Analog Devices. Er studierte Telekommunikation und Mikroelektronik an der Universidad de Valencia in Spanien. Seit rund 20 Jahren entwickelt er Mikroelektronik mit Schwerpunkt Power-Management, Schnittstellen und Isolierung. Aktuell arbeitet er an den Themen schnelle Isolatoren, isolierte Stromversorgung und EMV-Simulation.

- Simulation in fünf Schritten

- Fallbeispiel MEMS-Beschleunigungssensor