IEDM 2016

Speicher: Evolution und Revolution

Fortsetzung des Artikels von Teil 2

NAND-Flash-Technologie

Auch im NAND-Flash-Bereich wurde in den letzten Jahren kräftig skaliert, so dass mittlerweile Prozesse mit 1x-Strukturen zum Einsatz kommen. Lee: »Dadurch wurde die Dichte von 16 MBit mit SLC-Speicherzelle auf 128 GBit mit TLC-Speicherzelle erhöht.« Setzten die Hersteller lange auf eine Skalierung der 2D-Floating-Gate-Technik, gehen sie mittlerweile mit dem Wechsel auf 3D »revolutionäre Wege«, so Lee weiter. Alle großen NAND-Hersteller bauen derzeit ihre Serienfertigung auf Basis eigener 3D-Zellstrukturen (P-BiCS/Toshiba, TCAT/Samsung, 3D-FG/Hynix) auf. Mit 3D-NAND haben sich aus Lees Sicht viele Skalierungsprobleme etwas entspannt, allerdings nicht ohne, dass neue, bis dato unbekannte Schwierigkeiten dazugekommen wären. Außerdem ist Lee nicht davon überzeugt, dass die Kosten bei 3D-Speichern mithilfe einer Technologieskalierung weiterhin effektiv gesenkt werden können. Das Bit-Wachstum fällt beim 3D-Ansatz im Vergleich zu einer lateralen Skalierung bei 2D-NAND-Speichern um rund 50 Prozent niedriger aus. Dazu kommen noch deutlich längere Prozesszeiten und mechanischer Stress.

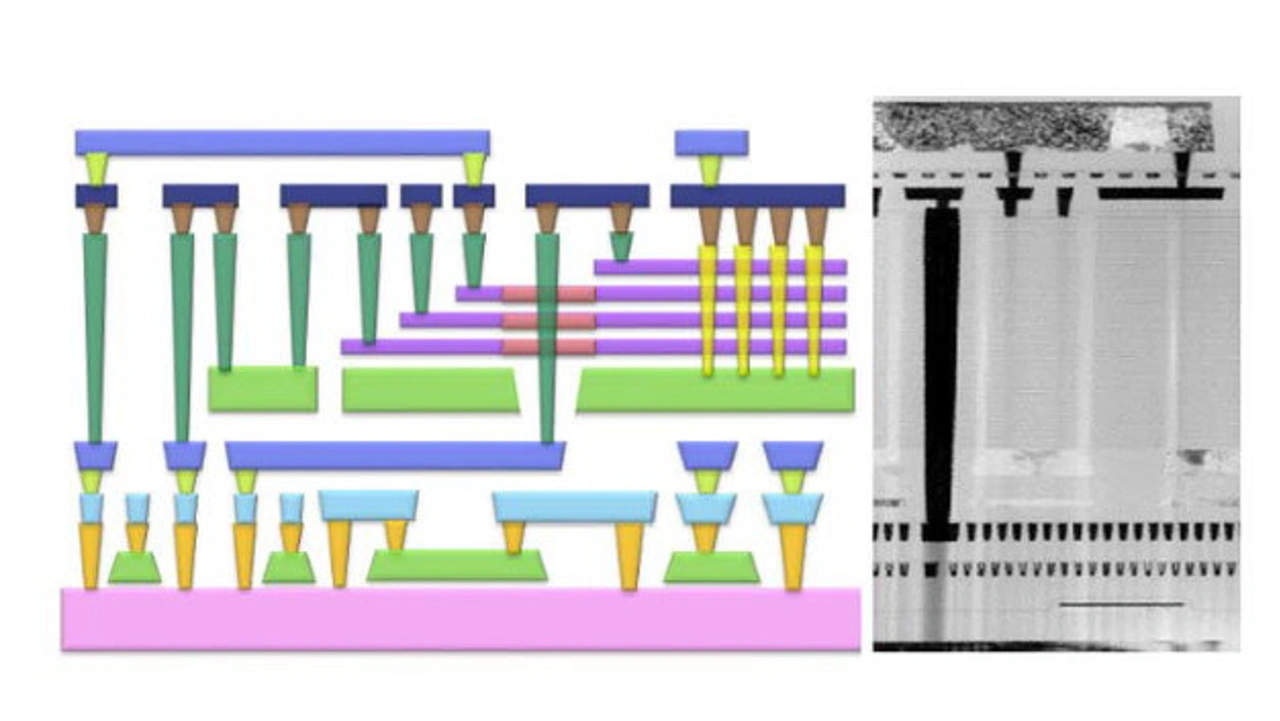

Neben den Fertigungsschwierigkeiten glaubt Lee, dass auch die Chip-Höhe ein Problem für Multi-Chip-Gehäuse werden könnte. Also müsste auch an einer Skalierung in z-Richtung (Verringerung des Unit-Stacks) gearbeitet werden, damit mit der 3D-Technologie in Zukunft 200 Stacks und mehr integriert werden können. Lee ist sogar der Überzeugung, dass die Skalierung in z-Richtung einer der wichtigsten Erfolgsfaktoren für zukünftige 3D-NAND-Speicher ist, denn davon wird die Herstellbarkeit maßgeblich beeinflusst. Aber auch in Hinblick auf Zuverlässigkeit und Performance dürften sich die Hersteller noch mit einigen Problemen herumschlagen müssen. Laut Lee wird derzeit an mehreren Ansätzen gearbeitet, um die Skalierungsprobleme in z-Richtung in den Griff zu bekommen. Er selbst hält Metall-Oxid-Stacks für einen vielversprechenden Ansatz, weil damit die Integration deutlich vereinfacht und der Widerstand niedriger ausfällt.

Einen weiteren Ansatz stellt die PUC-Struktur (Peripheral under Cell) dar, bei der Peripherie-Schaltungen unter dem Zell-Array vergraben werden. Lee hält viele technische Probleme beim PUC-Ansatz für gelöst, nur in Hinblick auf die Wärmeentwicklung und eine deutliche Skalierung der Transistoren müssten noch Lösungen gefunden werden.

Jobangebote+ passend zum Thema

- Speicher: Evolution und Revolution

- DRAM-Technologie

- NAND-Flash-Technologie

- Es herrsche Revolution